具有測距、測速和測角功能的信號處理芯片

本發明涉及信息處理,尤其涉及一種具有測距、測速和測角功能的信號處理芯片。

背景技術:

1、當前,數字信號處理技術正以前所未有的速度發展,特別是在探測目標距離、速度和角度的計算領域。其核心發展需求聚焦于實現更快的計算速度、拓展更寬的探測范圍,以及追求更高的探測精度。為了滿足這些迫切的應用需求,研發實時性強、能夠處理海量數據的信號處理芯片,且需兼具測距、測速與測角功能,已成為業界研究的焦點。

2、目前,這類數字信號處理系統大多依賴現場可編程門陣列(fpga)或商用數字信號處理器(dsp)平臺,然而,它們在面對上述需求時仍顯得力不從心。受限于面積、功耗及資源分配,這些平臺在實現大數據量的數字信號處理算法時遭遇了重重挑戰,難以高效部署與實施。相比之下,專用的數字信號處理芯片憑借其大規模、可重構的數字信號處理子模塊陣列脫穎而出。它不僅能夠支撐大規模的處理任務,還展現出極高的靈活性,為應對復雜多變的信號處理需求提供了有力保障。

技術實現思路

1、(一)要解決的技術問題

2、為解決現有技術中針對距離、速度和角度進行計算的數字信號處理技術所存在的上述問題,本發明的實施例提供了一種具有測距、測速和測角功能的信號處理芯片,通過基于單指令多數據流處理方式的并行處理架構,以調用大規模的數字信號處理子模塊的形式處理數據,有效提高對大規模處理任務的支持度,以及通過可重構的數字信號處理子模塊提高靈活性,支持更多種類的信號處理算法。

3、(二)技術方案

4、鑒于上述問題,本發明的實施例提供了一種具有測距、測速和測角功能的信號處理芯片。

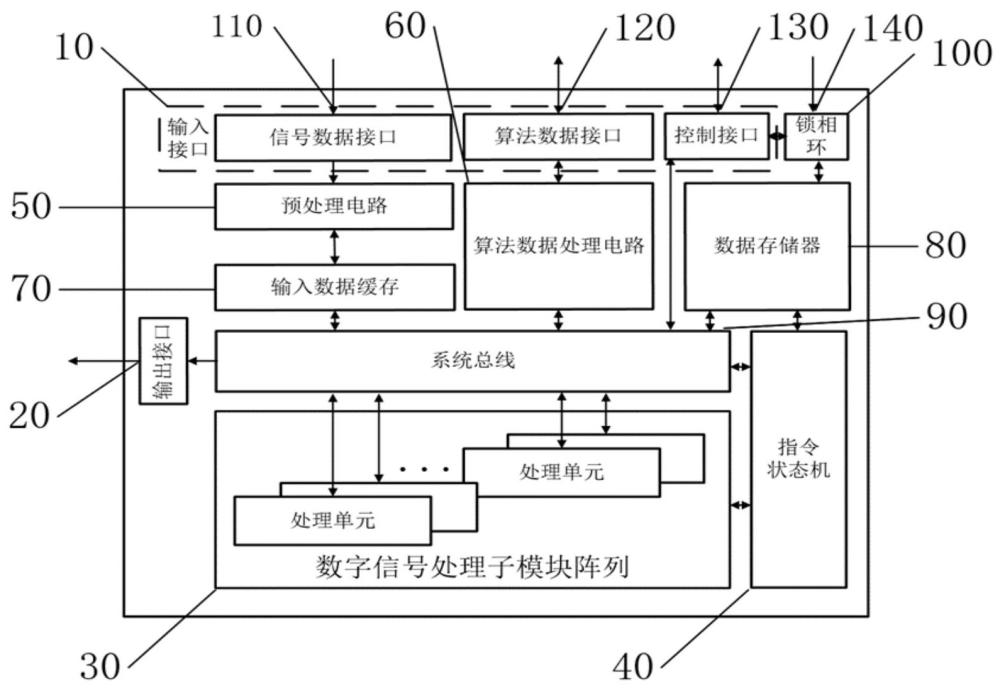

5、根據本發明的第一個方面,提供了一種具有測距、測速和測角功能的信號處理芯片,包括:數據輸入接口、數據輸出接口、數字信號處理子模塊陣列、指令狀態機、預處理電路、算法數據處理電路、輸入數據緩存、數據存儲器、系統總線以及鎖相環,其中,數據輸入接口,用于接收待處理的數字信號數據和算法數據,主控時鐘和控制信號;數據輸出接口,用于發送運算結果數據、運算中間數據和狀態機校驗信息;數字信號處理子模塊陣列,用于編程并行處理大規模數字信號數據;指令狀態機,用于執行輸入的指令代碼,調度片上的數據傳輸鏈路和運算資源完成對應的處理任務;預處理電路,用于將輸入數字信號轉換為能夠被處理的數據格式;算法數據處理電路,用于將輸入的數據信息轉換為能夠被系統總線處理并存儲的數據格式,其中,數據信息包括算法參數;輸入數據緩存,用于存儲經預處理電路處理后的輸入數字信號數據;數據存儲器,用于存儲運算中間數據、運算結果數據、算法參數和指令代碼;系統總線,用于芯片內部的數據傳輸,連接數字信號處理子模塊陣列與數據存儲器;以及鎖相環,用于根據指令配置產生芯片工作的主頻時鐘。

6、在一些示例性的實施例中,數據輸入接口包括數字信號接口、算法數據接口、控制信號接口以及主控時鐘接口,其中,數字信號接口,用于接收來自前端的數字信號;算法數據接口,用于接收來自芯片外存儲的數字信號處理算法參數,狀態機指令和中間數據;以及控制信號接口,用于控制芯片全局復位和狀態機校驗選擇。

7、在一些示例性的實施例中,數字信號數據從數字信號接口輸入,經預處理電路處理后存入輸入數據緩存;算法參數從算法數據接口輸入,經算法數據處理電路處理后存入數據存儲器;以及數字信號數據和算法參數經數字信號處理子模塊陣列處理后得到處理結果,存入數據存儲器中,最后經過系統總線,由輸出接口輸出到上位機。

8、在一些示例性的實施例中,數字信號處理子模塊陣列包括:降頻抽取濾波模塊、脈沖壓縮模塊、傅里葉變換模塊、恒虛警率檢測模塊以及角度檢測模塊,其中,降頻抽取濾波模塊,用于對數字信號序列執行正交下變頻、有限沖激響應和抽取濾波操作;脈沖壓縮模塊,用于對數字信號執行頻域相關操作;傅里葉變換模塊,用于對數字信號執行傅里葉變換;恒虛警率檢測模塊,用于對二維數字信號圖執行恒虛警率檢測,以去除虛警點;角度檢測模塊,用于對數字信號執行目標角度信息檢測。

9、在一些示例性的實施例中,數字信號處理子模塊陣列包括多個并列的數字信號處理子模塊,根據指令狀態機的控制,每個數字信號處理子模塊能夠分立處理不同的運算任務;以及多個數字信號處理子模塊能夠協同計算。

10、在一些示例性的實施例中,數字信號處理子模塊陣列的運行流程包括:重復運行降頻抽取濾波模塊和脈沖壓縮模塊,以得到二維信號數據;運行傅里葉變換模塊和恒虛警率檢測模塊,以得到目標的距離和速度信息;以及運行角度檢測模塊,以得到目標的角度信息。

11、在一些示例性的實施例中,數據存儲器包括:一維信號數據存儲,用于緩存降頻抽取濾波的結果;二維信號數據存儲,用于積累經脈沖壓縮處理后的一維信號數據;算法參數存儲,用于存儲各數字信號處理子模塊所需的參數;以及指令參數存儲,用于存儲指令狀態機的算法指令。

12、在一些示例性的實施例中,預處理電路在單次接收周期內對輸入數字信號進行實時預處理操作并寫入輸入數據緩存;在下一個接收周期開始時,數字信號處理子模塊陣列中的降頻抽取濾波模塊讀取數據緩存,并將結果寫入一維信號數據存儲;脈沖壓縮模塊讀取一維信號數據存儲,并將結果寫入二維信號數據存儲。

13、在一些示例性的實施例中,包含一些特征中的至少之一:預處理電路將輸入數字信號轉換為可被處理的數據格式,包括,將數字信號接口輸入的數字信號進行合并和積累,將積累后的信號轉換為可被處理的數據格式;算法數據處理電路將輸入的數據信息轉換為可被系統總線處理并存儲的數據格式,包括,將算法數據接口輸入的數據信息進行積累和重新排列,轉換為可被系統總線傳輸并存儲的數據格式;在數據存儲器中,每種數據具有獨立的存儲空間。

14、在一些示例性的實施例中,指令狀態機采用自定義精簡指令集實現數字信號處理算法,其中,自定義精簡指令集包括計算指令、數據搬運指令以及指令流控制指令;以及自定義精簡指令集存儲于數據存儲器中。

15、(三)有益效果

16、從上述技術方案可以看出,本發明的實施例提供的一種具有測距、測速和測角功能的信號處理芯片至少具有以下有益效果其中之一:

17、(1)能夠通過指令編程方式調整運算順序和內容,以靈活的形式對硬件設計進行復用。

18、(2)使用分離式的數字信號處理子模塊設計,在提升支持數據量的同時降低芯片功耗。

19、(3)不同用途的存儲各自獨立,提升訪存速度和數據吞吐率。

20、(4)數字信號處理子模塊陣列以數字信號處理子模塊為單位分立處理不同的運算任務,并可以多個模塊協同計算,通過增大子模塊運算單元數量提升可支持的待處理數據規模,通過可重構的數字信號處理子模塊硬件設計提升靈活性。

技術特征:

1.一種具有測距、測速和測角功能的信號處理芯片,其特征在于,包括:數據輸入接口、數據輸出接口、數字信號處理子模塊陣列、指令狀態機、預處理電路、算法數據處理電路、輸入數據緩存、數據存儲器、系統總線以及鎖相環,

2.根據權利要求1所述的信號處理芯片,其特征在于,所述數據輸入接口包括數字信號接口、算法數據接口、控制信號接口以及主控時鐘接口,

3.根據權利要求2所述的信號處理芯片,其特征在于,數字信號數據從數字信號接口輸入,經預處理電路處理后存入輸入數據緩存;

4.根據權利要求1所述的信號處理芯片,其特征在于,所述數字信號處理子模塊陣列包括:降頻抽取濾波模塊、脈沖壓縮模塊、傅里葉變換模塊、恒虛警率檢測模塊以及角度檢測模塊,

5.根據權利要求4所述的信號處理芯片,其特征在于,所述數字信號處理子模塊陣列包括多個并列的信號處理子模塊,根據指令狀態機的控制,每個數字信號處理子模塊能夠分立處理不同的運算任務;以及多個數字信號處理子模塊能夠協同計算。

6.根據權利要求4所述的信號處理芯片,其特征在于,數字信號處理子模塊陣列的運行流程包括:重復運行降頻抽取濾波模塊和脈沖壓縮模塊,以得到二維信號數據;

7.根據權利要求4所述的信號處理芯片,其特征在于,所述數據存儲器包括:

8.根據權利要求7所述的信號處理芯片,其特征在于,預處理電路在單次接收周期內對輸入數字信號進行實時預處理操作并寫入輸入數據緩存;

9.根據權利要求1所述的信號處理芯片,其特征在于,包含一些特征中的至少之一:

10.根據權利要求1所述的信號處理芯片,其特征在于,所述指令狀態機采用自定義精簡指令集實現數字信號處理算法,

技術總結

本發明提供了一種具有測距、測速和測角功能的信號處理芯片,可應用于信息處理技術領域。該信號處理芯片包括:數據輸入接口,用于接收待處理數據,時鐘和控制信號;數據輸出接口,用于發送結果數據和校驗信息;數字信號處理子模塊陣列,用于并行處理大規模數字信號數據;指令狀態機,用于調度片上的數據傳輸和運算資源;預處理電路,用于轉換輸入數字信號的格式;算法數據處理電路,用于將轉換輸入數據信息的數據格式;輸入數據緩存,用于存儲輸入數字信號數據;數據存儲器,用于存儲運算數據;系統總線,用于芯片內部的數據傳輸;鎖相環用于產生芯片工作的主頻時鐘。該芯片能夠通過編程進行高速并行的數字信號處理流程。

技術研發人員:徐宣哲,劉力源,竇潤江,劉顯軍,于雙銘,馮鵬,劉劍,吳南健

受保護的技術使用者:中國科學院半導體研究所

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!