一種基于RRAM對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng)及方法

本發(fā)明屬于集成電路相關(guān),更具體地,涉及一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng)及方法。

背景技術(shù):

1、對于逐次逼近型模數(shù)轉(zhuǎn)換器(sar?adc)來說,其電容陣列的開關(guān)能耗是主要的能耗,如果能降低其單位電容的面積,則其能耗會大大減小,但減小單位電容面積會導(dǎo)致單位電容之間的失配率會增加,使得整個adc的線性度無法滿足要求。對sar?adc進行前臺校準(zhǔn)可以一定程度上補償電容失配帶來的誤差,提高系統(tǒng)的線性度,降低線性度對電容失配的要求。

2、而目前的關(guān)于sar?adc的數(shù)字前臺校準(zhǔn)方案都不具有非易失性,導(dǎo)致存儲的數(shù)據(jù)每次掉電之后都會丟失,每次sar?adc在工作前都要進入校準(zhǔn)模式,大大浪費了時間和能耗。

3、所以,目前需要設(shè)計一種具有非易失性的極低功耗的sar?adc的前臺校準(zhǔn)方案,用于校準(zhǔn)adc由于電容失配帶來的誤差,提升sar?adc的線性度,放寬對電容失配率的要求,提升整個sar?adc系統(tǒng)的能效。

技術(shù)實現(xiàn)思路

1、針對相關(guān)技術(shù)的缺陷,本發(fā)明的目的在于提供一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng)及方法,旨在解決現(xiàn)有數(shù)字前臺校準(zhǔn)方案不具有非易失性,導(dǎo)致存儲的數(shù)據(jù)每次掉電之后都會丟失,每次在工作前都要進入校準(zhǔn)模式,大大浪費了時間和能耗的問題。

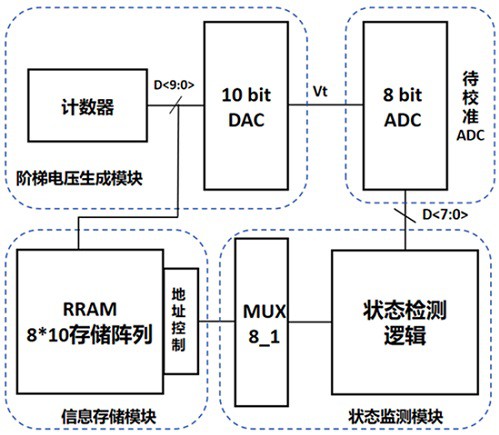

2、為實現(xiàn)上述目的,第一方面,本發(fā)明提供了一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng),包括:階梯電壓生成模塊、狀態(tài)監(jiān)測模塊、信息存儲模塊和數(shù)據(jù)處理模塊;所述階梯電壓生成模塊只在校準(zhǔn)模式下有效,在工作模式下關(guān)斷;所述數(shù)據(jù)處理模塊在校準(zhǔn)模式下關(guān)斷,在工作模式下有效;

3、所述階梯電壓生成模塊包括一個n+m位寬的計數(shù)器和一個分辨率為n+m位的數(shù)模轉(zhuǎn)換器,所述計數(shù)器的輸入端與外部時鐘連接,輸出端與所述數(shù)模轉(zhuǎn)換器的輸入端連接,所述數(shù)模轉(zhuǎn)換器的輸出端與待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的輸入端連接;所述計數(shù)器用于產(chǎn)生不斷自加的數(shù)字碼,所述數(shù)模轉(zhuǎn)換器用于將數(shù)字碼轉(zhuǎn)換為一個不斷上升的模擬階梯電壓vt,并輸出至待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器;其中,m、n均為正整數(shù);

4、所述狀態(tài)監(jiān)測模塊包括一個狀態(tài)檢測邏輯單元和一個選擇器;在校準(zhǔn)模式下,所述狀態(tài)檢測邏輯單元的輸入端與待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的輸出端連接,輸出端與所述選擇器的輸入端連接,所述選擇器的輸出端與所述信息存儲模塊連接;所述狀態(tài)檢測邏輯單元用于檢測待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字輸出碼的模式,所述選擇器用于根據(jù)數(shù)字輸出碼的模式響應(yīng)不同的控制信號;在工作模式下,所述狀態(tài)監(jiān)測邏輯單元的輸入端與被校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的輸出端連接,所述狀態(tài)檢測邏輯單元用于檢測被校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字輸出碼的模式,所述選擇器用于根據(jù)數(shù)字輸出碼的模式響應(yīng)不同的控制信號;

5、所述信息存儲模塊包括地址控制單元和基于rram的存儲陣列單元;在校準(zhǔn)模式下,所述存儲陣列單元與所述計數(shù)器連接,用于存儲階梯電壓生成模塊所產(chǎn)生的n個(n+m)位的數(shù)字校準(zhǔn)碼;所述地址控制單元用于根據(jù)所述狀態(tài)監(jiān)測模塊輸出的控制信號,選中所述存儲陣列中不同的列,將數(shù)字校準(zhǔn)碼寫入所述存儲陣列;在工作模式下,所述存儲陣列單元與數(shù)據(jù)處理模塊連接,所述地址控制單元用于根據(jù)所述狀態(tài)監(jiān)測模塊輸出的控制信號,選中所述存儲陣列中不同的列,從所述存儲陣列中讀出數(shù)字校準(zhǔn)碼;

6、所述數(shù)據(jù)處理模塊包括一個n+m位的數(shù)據(jù)累加器和一個n位的數(shù)據(jù)斬斷器,所述數(shù)據(jù)累加器的輸入端與所述信息存儲模塊連接,輸出端與所述數(shù)據(jù)斬斷器的輸入端連接;所述數(shù)據(jù)累加器用于對所述信息存儲模塊中選中的n+m位數(shù)字校準(zhǔn)碼進行累加,所述數(shù)據(jù)斬斷器用于對數(shù)據(jù)進行斬斷,只保留其前n位,作為校準(zhǔn)后的逐次逼近型模數(shù)轉(zhuǎn)換器的輸出。

7、可選的,所述計數(shù)器接收外部時鐘信號,在每個時鐘的上升沿將輸出自加,產(chǎn)生位寬為n+m位的數(shù)字碼;

8、所述數(shù)模轉(zhuǎn)換器在系統(tǒng)時鐘的控制下周期性地將所述計數(shù)器的數(shù)字輸出碼轉(zhuǎn)換為模擬電壓,得到階梯電壓vt,將其輸出至逐次逼近型模數(shù)轉(zhuǎn)換器;所述階梯電壓vt包含n位數(shù)字輸出的所有情況。

9、可選的,校準(zhǔn)模式下,所述狀態(tài)監(jiān)測模塊用于自動檢測所述待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字輸出碼的模式,檢測其模式是否為只有一位是“1”而其余所有位全為“0”,如果檢測結(jié)果為真,則檢測所述數(shù)字輸出碼中“1”所處的位置,所述選擇器用于根據(jù)檢測得到的位置響應(yīng)不同的控制信號輸出到信息存儲模塊;如果檢測結(jié)果為假,則直接跳過這一個校準(zhǔn)周期;

10、在工作模式下,所述狀態(tài)監(jiān)測模塊用于自動監(jiān)測所述被校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字輸出碼的模式,檢測其中含有數(shù)字碼為“1”的個數(shù)n,并以此將該次工作模式的工作周期設(shè)為n,并檢測數(shù)字輸出碼中每個“1”所處的位數(shù),所述選擇器用于在接下來的n個工作周期對每個不同的“1”響應(yīng)不同的控制信號。

11、可選的,在校準(zhǔn)模式下,所述信息存儲模塊中的地址控制單元用于接受所述狀態(tài)檢測模塊響應(yīng)的控制信號,選中所述存儲陣列中的不同位置的列,并將該周期所對應(yīng)的數(shù)字輸出碼存儲到相應(yīng)位置作為數(shù)字校準(zhǔn)碼;

12、在工作模式下,所述信息存儲模塊中的地址控制單元用于接受所述狀態(tài)檢測模塊響應(yīng)的控制信號,選中所述存儲陣列中的不同位置的列,并將存儲陣列存儲的數(shù)字校準(zhǔn)碼依周期讀取出來傳輸?shù)綌?shù)據(jù)處理模塊。

13、可選的,所述存儲陣列單元的數(shù)量為n*(n+m)個;每個所述存儲陣列單元包括7個mos管和2個rram,其中,3個mos管作為信號的選通開關(guān),4個mos管構(gòu)成首尾相連的反相器用以增強存儲信號,2個rram作為存儲信息的媒介;

14、在校準(zhǔn)模式下,所述存儲陣列單元處于寫模式,將數(shù)字校準(zhǔn)碼一一寫入;

15、在工作模式下,所述存儲陣列單元處于讀模式,將數(shù)字校準(zhǔn)碼一一讀出到數(shù)據(jù)處理模塊。

16、可選的,所述數(shù)據(jù)處理模塊的數(shù)據(jù)累加器用于將接收到的n+m位數(shù)字校準(zhǔn)碼進行累加,判斷累加結(jié)果是否超出n+m位,若超出,則輸出n+m位“1”,若不超出,則所述數(shù)據(jù)斬斷器對累加后的數(shù)據(jù)進行斬斷操作,只保留數(shù)據(jù)的高n位作為輸出。

17、可選的,n=8,m=2。

18、第二方面,本發(fā)明還提供了一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)方法,基于如第一方面中任一項所述的基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng)執(zhí)行,針對一個待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器,先進行一次校準(zhǔn)模式,后續(xù)均為工作模式;

19、當(dāng)處于校準(zhǔn)模式時,所述方法包括:

20、所述階梯電壓產(chǎn)生模塊產(chǎn)生階梯電壓vt輸入所述待校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器,使其產(chǎn)生不同的數(shù)字輸出碼;

21、所述狀態(tài)監(jiān)測模塊檢測數(shù)字輸出碼的模式,如果符合預(yù)設(shè)的輸出模式,則選擇器根據(jù)所述數(shù)字輸出碼中“1”所處的位置響應(yīng)一個控制信號,并注入所述存儲陣列單元,控制其對相應(yīng)的數(shù)字校準(zhǔn)碼進行寫入操作;

22、當(dāng)處于工作模式時,所述方法包括:

23、所述狀態(tài)監(jiān)測模塊檢測所述被校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字輸出碼的模式,記錄其數(shù)字輸出碼中“1”的個數(shù)和每個“1”所處的位置,所述選擇器根據(jù)不同的數(shù)字輸出碼響應(yīng)不同的控制信號,并控制所述存儲陣列單元分別讀出相應(yīng)的數(shù)字校準(zhǔn)碼;

24、所述數(shù)據(jù)處理模塊分周期獲取所述數(shù)字校準(zhǔn)碼進行數(shù)據(jù)累加與斬斷,輸出校準(zhǔn)后的數(shù)字輸出碼。

25、通過本發(fā)明所構(gòu)思的以上技術(shù)方案,與現(xiàn)有技術(shù)相比,能夠取得以下有益效果:

26、1、本發(fā)明提供的一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng),存儲部分使用了rram作為存儲數(shù)字信號的媒介,所有數(shù)字信號都存儲在rram中,使其存儲的數(shù)據(jù)具有非易失性,不會因為上電掉電而丟失,故穩(wěn)定性得以保證,只要寫入后便不會發(fā)生信號泄露,使得校準(zhǔn)的精度增加,抗干擾性也增強,因此該校準(zhǔn)系統(tǒng)針對sar?adc只需進行一次校準(zhǔn)模式,獲取到足夠的校準(zhǔn)碼后,之后再使用該款adc無需再進行校準(zhǔn),可以直接進入工作模式,所以極大節(jié)省了校準(zhǔn)所消耗的時間,極大降低校準(zhǔn)所需的功耗,提高了速度。

27、2、本發(fā)明提供的一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng),在校準(zhǔn)模式時,存儲的n*m位的數(shù)字校準(zhǔn)碼累加并取代掉待校準(zhǔn)sar?adc的數(shù)字輸出碼后,使得該adc的動態(tài)性能包括有效位數(shù)得到顯著提高,降低該adc的單位電容值進,而大大降低其能耗,提高了被校準(zhǔn)adc的能效,也減小了其面積。

28、3、本發(fā)明提供的一種基于rram對逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)字前臺校準(zhǔn)系統(tǒng),結(jié)構(gòu)主要包括多路選擇器和累加器和由rram組成的存儲陣列,可以采用較簡的硬件開銷完成校準(zhǔn)的功能,為整個系統(tǒng)減少面積,提升系統(tǒng)的能效比。其中,采用rram取代傳統(tǒng)的sram進行數(shù)據(jù)存儲,rram具有面積小功耗低且集成度大的優(yōu)點,故能極大地節(jié)省存儲所需的面積與功耗。

- 還沒有人留言評論。精彩留言會獲得點贊!

- 一種分段延遲環(huán)模數(shù)轉(zhuǎn)換器的制造方法

- 逐次逼近型模數(shù)轉(zhuǎn)換器校準(zhǔn)電路的制作方法

- 一種逐次逼近型模數(shù)轉(zhuǎn)換器及其開關(guān)時序的制作方法

- 一種新型高精度電容自校準(zhǔn)逐次逼近型模數(shù)轉(zhuǎn)換器的制造方法

- 與圖像傳感器讀出兼容的模數(shù)轉(zhuǎn)換器的制造方法

- 基于一位冗余位的帶數(shù)字校準(zhǔn)的逐次逼近型模數(shù)轉(zhuǎn)換器的制造方法

- 用于逐次逼近型模數(shù)轉(zhuǎn)換器的數(shù)模轉(zhuǎn)換模塊的制作方法

- 逐步逼近式模擬數(shù)字轉(zhuǎn)換器及其控制方法

- 亞穩(wěn)態(tài)消除電路及其設(shè)備的制造方法

- 一種具備數(shù)字失配校正能力的逐次逼近型模數(shù)轉(zhuǎn)換器的制造方法