像素電路及其驅動方法、顯示面板、以及顯示裝置與流程

本公開涉及顯示,特別是涉及一種像素電路及其驅動方法、顯示面板、以及顯示裝置。

背景技術:

1、在顯示技術領域中,為了實現更好的變頻效果,目前通常會采用基于氧化物工藝的像素架構。然而,目前氧化物工藝的顯示產品邊框較寬。

技術實現思路

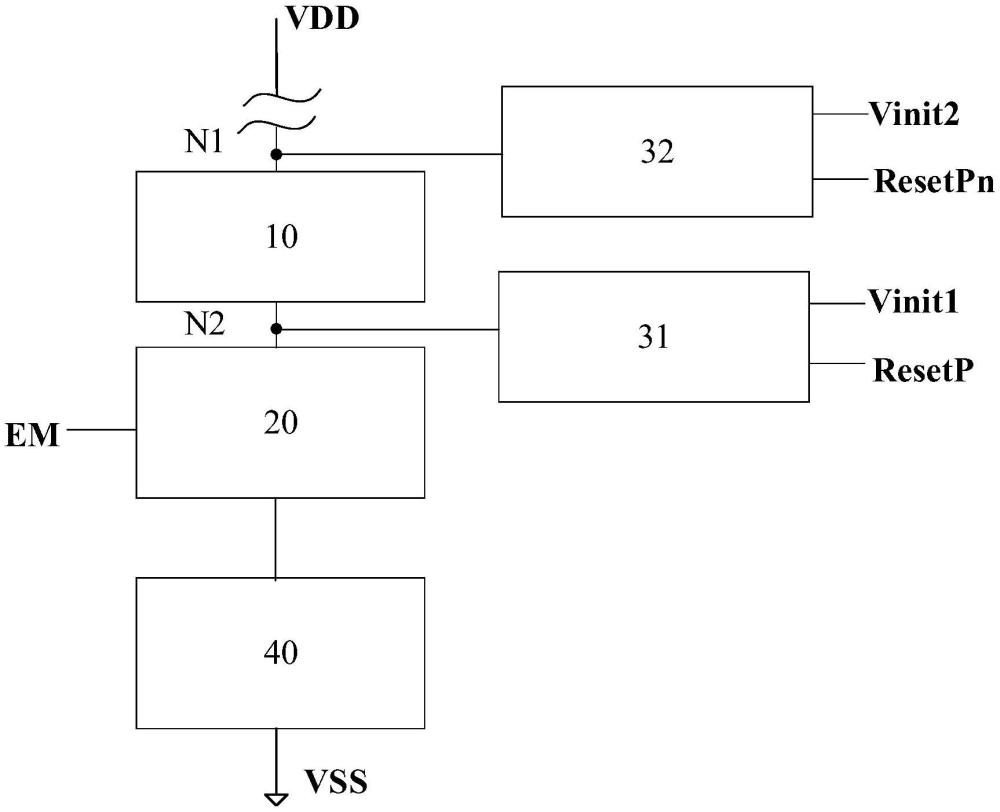

1、為了解決上述問題至少之一,本公開第一個方面提供一種像素電路,包括:驅動子電路、第一發光控制子電路、第一復位子電路、第二復位子電路、以及發光單元,

2、驅動子電路,包括驅動晶體管,電連接在第一節點和第二節點之間,配置為產生從第一電源信號端至發光單元的第一極的驅動電流,

3、第一發光控制子電路,電連接至第二節點、發光單元的第一極和第一發光控制端,配置為基于第一發光控制端的信號將驅動電流傳輸至第一極并驅動發光單元發光,

4、第一復位子電路,電連接在第一復位信號端、第一復位控制端和第二節點,配置為基于第一復位控制端的信號將第一復位信號端與第二節點電連接,

5、第二復位子電路,電連接在第二復位信號端、第二復位控制端和第一節點,配置為基于第二復位控制端的信號將第二復位信號端與第一節點電連接,

6、第二復位控制端接入的信號和第一復位控制端接入的信號來自同一組柵極驅動電路的不同輸出信號線,第二復位控制端接入的信號為第一復位控制端接入的信號延遲n個h的信號,h為第一復位控制端接入的信號掃描一行發光單元的時間,n為大于等于1的整數。

7、可選地,像素電路還包括:第三復位子電路,電連接在發光單元的第一極、第三復位控制端、第三復位信號端之間,配置為基于第三復位控制端的信號將第三復位信號端與第一極電連接,

8、第三復位控制端接入的信號與第二復位控制端接入的信號相同。

9、可選地,第一復位子電路包括:第一晶體管,第一晶體管的第一極電連接至第一復位信號端,第二極電連接至第二節點,控制極電連接至第一復位控制端,

10、第二復位子電路包括:第二晶體管,第二晶體管的第一極電連接至第二復位信號端,第二極電連接至第一節點,控制極電連接至第二復位控制端,

11、第三復位子電路包括:第三晶體管,第三晶體管的第一極電連接至第三復位信號端,第二極電連接至發光單元的第一極,控制極電連接至第三復位控制端,

12、第一晶體管、第二晶體管和第三晶體管的晶體管類型相同。

13、可選地,像素電路還包括:補償子電路和寫入子電路,

14、補償子電路電連接至第二節點、驅動晶體管的控制極對應的第三節點和補償控制端,配置為基于補償控制端的信號將第二節點和第三節點電連接,

15、寫入子電路電連接至第一節點、數據信號端和數據控制端,配置為基于數據控制端的信號將數據信號端接入的數據信號傳輸至第一節點。

16、可選地,第一發光控制子電路包括第四晶體管,第四晶體管的第一極電連接至第二節點,第二極電連接至第一極,控制極電連接至第一發光控制端,

17、補償子電路包括第五晶體管,第五晶體管的第一極電連接至第二節點,第二極電連接至第三節點,控制極電連接至補償控制端,

18、寫入子電路包括第六晶體管,第六晶體管的第一極電連接至數據信號端,第二極電連接至第一節點,控制極電連接至數據控制端,

19、像素電路還包括第一電容,第一電容的第一極電連接至第一電源信號端,第二極電連接至第三節點。

20、可選地,像素電路還包括:第二發光控制子電路,第二發光控制子電路包括第七晶體管,第七晶體管的第一極電連接至第一電源信號端,第二極電連接至第一節點,控制極電連接至第二發光控制端。

21、本公開第二個方面提供一種顯示面板,包括如上文所述的像素電路。

22、可選地,顯示面板還包括:級聯的多個第一移位寄存器和級聯的多個第二移位寄存器,

23、第一移位寄存器的數量小于像素電路的行數且第二移位寄存器的數量為小于n個,或者,第一移位寄存器的數量等于像素電路的行數且第二移位寄存器的數量等于n個,

24、第一移位寄存器級聯后再與級聯的多個第二移位寄存器級聯以構成第一柵極驅動電路,第一柵極驅動電路向第二復位控制端和第一復位控制端提供信號。

25、可選地,顯示面板包括顯示區和圍繞顯示區的非顯示區,

26、非顯示區包括設置在像素電路行的延伸方向上的延伸區域,

27、第一移位寄存器的數量為像素電路的行數的一半,每個第一移位寄存器在像素電路行的排列方向所占據的范圍與兩個像素電路行對應的延伸區域交疊。

28、可選地,顯示面板包括顯示區和圍繞顯示區的非顯示區,顯示區包括第一邊和與第一邊相交的第二邊和第三邊,非顯示區包括:與第一邊相鄰的第一側區域、與第二邊相鄰的第二側區域、與第三邊相鄰的第三側區域,

29、第二移位寄存器設置在第一側區域和第二側區域之間的角落區域或者設置在第一側區域和第三側區域之間的角落區域。

30、可選地,顯示面板還包括:級聯的多個第三移位寄存器和級聯的多個第四移位寄存器,顯示面板包括顯示區和圍繞顯示區的非顯示區,

31、顯示面板包括設置在顯示區的m個像素電路行,像素電路包括寫入子電路,寫入子電路基于數據控制端的信號將數據信號端接入的信號傳輸至第一節點,

32、非顯示區包括靠近像素電路行一端的第一側區域和靠近像素電路行另一端的第四側區域,

33、第三移位寄存器設置在第一側區域和第四側區域中的一者中且第n個第三移位寄存器的輸出端與第2n-1個像素電路行中的數據控制端電連接,

34、第四移位寄存器設置在第一側區域和第四側區域中的另一者中且第n個第四移位寄存器的輸出端與第2n個像素電路行中的數據控制端電連接,

35、n為大于等于1的整數,m為大于等于2的整數。

36、可選地,顯示面板包括顯示區和圍繞顯示區的非顯示區,

37、非顯示區包括設置在像素電路行的延伸方向上的延伸區域,

38、每個第三移位寄存器在像素電路行的排列方向所占據的范圍與兩個像素電路行的延伸區域交疊,

39、每個第四移位寄存器在像素電路行的排列方向所占據的范圍與兩個像素電路行的延伸區域交疊。

40、可選地,第一移位寄存器的數量為像素電路的行數的一半,顯示面板還包括顯示區和圍繞顯示區的非顯示區,

41、顯示面板還包括:設置在顯示區的m個像素電路行,像素電路包括寫入子電路,寫入子電路基于數據控制端的信號將數據信號端接入的信號傳輸至第一節點;

42、級聯的m個第三移位寄存器和級聯的m個第四移位寄存器,

43、非顯示區包括靠近像素電路行一端的第一側區域和靠近像素電路行另一端的第四側區域,

44、第三移位寄存器和第四移位寄存器中的一者設置在第一側區域,另一者設置在第四側區域,

45、第n個第三移位寄存器和第n個第四移位寄存器的輸出端均與第n個像素電路行中的數據控制端電連接,

46、n為大于等于1的整數,m為大于等于2的整數。

47、可選地,顯示面板還包括顯示區和圍繞顯示區的非顯示區,

48、顯示面板還包括:

49、設置在顯示區的m個像素電路行,像素電路包括補償子電路,補償子電路基于補償控制端的信號將第二節點和驅動晶體管的控制極對應的第三節點電連接;以及

50、級聯的m/2個第五移位寄存器和級聯的m/2個第六移位寄存器,

51、所述非顯示區包括靠近所述像素電路行一端的第一側區域和靠近所述像素電路行另一端的第四側區域,

52、所述第五移位寄存器和所述第六移位寄存器中的一者設置在所述第一側區域,另一者設置在所述第四側區域,

53、每個第五移位寄存器的輸出端同時電連接至相鄰兩行像素電路的補償控制端,

54、每個第六移位寄存器的輸出端同時電連接至相鄰兩行像素電路的第一發光控制端,

55、m為大于等于2的整數。

56、本公開第三個方面提供一種顯示裝置,包括如上文所述的顯示面板。

57、本公開第四個方面提供一種如權上文所述的像素電路的驅動方法,包括:

58、第一復位階段,第一復位子電路基于第一復位控制端接入的信號為有效電平將第一復位信號端的電位傳輸至第二節點;

59、第二復位階段,第二復位子電路基于第二復位控制端接入的信號為有效電平將第二復位信號端的電位傳輸至第一節點,第二復位階段的時段比第一復位時段延遲的時間段為n個h;

60、發光控制階段,基于第一發光控制端的信號為有效電平將驅動電流傳輸至第一極并驅動發光單元發光。

61、本公開的有益效果如下:

62、本公開針對目前現有的問題,制定一種像素電路及其驅動方法、顯示面板、以及顯示裝置,通過利用來自同一組信號線的具有延時的信號分別接入第一復位子電路和第二復位子電路,從而能夠縮減像素電路所需要的柵極驅動電路的組數,降低了顯示產品的邊框寬度,利于實現窄邊框設計,同時降低了驅動芯片的功耗,具有廣闊的應用前景。

- 還沒有人留言評論。精彩留言會獲得點贊!