一種離體微電極陣列芯片及其制備方法與流程

本發(fā)明涉及生物傳感器的微加工領(lǐng)域,具體涉及一種離體微電極陣列芯片及其制備方法。

背景技術(shù):

1、mems全稱micro?electromechanical?system,即微機(jī)電系統(tǒng),是在微電子技術(shù)(半導(dǎo)體制造技術(shù))基礎(chǔ)上發(fā)展起來(lái)的,融合了光刻、腐蝕、薄膜、liga、硅微加工、非硅微加工和精密機(jī)械加工等技術(shù)制作的高科技電子機(jī)械器件。mems微納加工技術(shù)是實(shí)現(xiàn)mems器件制造的關(guān)鍵。

2、mems微納加工技術(shù)是指尺度為毫米、微米和納米量級(jí)的零件,以及由這些零件構(gòu)成的部件或系統(tǒng)的設(shè)計(jì)、加工、組裝、集成與應(yīng)用技術(shù)。它能實(shí)現(xiàn)更小尺度和更高精度的加工,可以顯著提升加工產(chǎn)品的功能密度和性能,有利于推進(jìn)光電子、高端制造和生物醫(yī)學(xué)等高科技領(lǐng)域的高質(zhì)量發(fā)展。

3、微納3d打印是一種基于增材原理制造微納結(jié)構(gòu)的新型微納加工技術(shù)。其工作原理主要包括光固化、電子束和激光束等方法。在打印過(guò)程中,先通過(guò)計(jì)算機(jī)輔助設(shè)計(jì)軟件創(chuàng)建出所需的微納結(jié)構(gòu)模型,然后通過(guò)光固化、電子束或激光束等方式逐層成型,最終完成微納級(jí)物體的制造。

4、在微納加工領(lǐng)域,3d打印技術(shù)相較于傳統(tǒng)的mems微納加工技術(shù),在制備離體微電極陣列方面展現(xiàn)出了顯著的技術(shù)優(yōu)勢(shì),尤其是在成本效益和可定制化方面。

5、首先,從成本效益的角度來(lái)看,3d打印技術(shù)能夠顯著降低中小批量定制mems器件的啟動(dòng)成本。傳統(tǒng)的mems生產(chǎn)成本高昂,如果使用傳統(tǒng)半導(dǎo)體技術(shù)來(lái)制造一款mems產(chǎn)品的成本在數(shù)十萬(wàn)美元左右,而且生產(chǎn)周期通常需要幾個(gè)月甚至更長(zhǎng)。而3d打印技術(shù)不僅成本低,而且大大壓縮了生產(chǎn)時(shí)間。

6、其次,在可定制化方面,3d打印技術(shù)提供了前所未有的設(shè)計(jì)和布置靈活性,可以用最少的資源和時(shí)間單獨(dú)定制每個(gè)刀柄的高度和位置,以及它們各自的電氣布線。這種靈活性使得3d打印技術(shù)能夠支持多種生物醫(yī)學(xué)設(shè)備的可能性,尤其是在微電極陣列的設(shè)計(jì)和制造上,可以有針對(duì)性地和大規(guī)模地記錄整個(gè)大腦中的電信號(hào)。

7、綜上所述,3d打印技術(shù)在制備離體微電極陣列時(shí),相較于mems微納加工技術(shù),具有更低的成本和更高的可定制化水平,這使得3d打印技術(shù)在微納加工領(lǐng)域具有顯著的技術(shù)優(yōu)勢(shì)。

技術(shù)實(shí)現(xiàn)思路

1、本發(fā)明提供了一種離體微電極陣列芯片的制備方法,該制備方法能夠高效,成本較低的制備離體微電極陣列芯片。

2、本發(fā)明提供了一種離體微電極陣列芯片的制備方法,包括:

3、s1、清洗、吹干絕緣基底;

4、s2、采用3d打印技術(shù)在所述絕緣基底表面打印出微電極陣列;

5、s3、在微電極陣列上形成絕緣層,然后通過(guò)光刻和等離子刻蝕刻蝕絕緣層,暴露出微電極;

6、s4、通過(guò)電化學(xué)方法在微電極表面修飾納米材料。

7、優(yōu)選地,采用3d打印技術(shù)在微電極陣列上形成絕緣層。

8、優(yōu)選地,所述絕緣基底的材料為硬質(zhì)透明絕緣材料,所述硬質(zhì)透明絕緣材料包括石英玻璃、聚氯乙烯或聚碳酸酯。

9、優(yōu)選地,所述絕緣基底的邊長(zhǎng)為25mm~80mm,厚度為1mm~2mm。

10、優(yōu)選地,所述微電極陣列的材料為導(dǎo)電薄膜材料,所述導(dǎo)電薄膜材料為金屬、金屬化合物或?qū)щ娋酆衔铩?/p>

11、優(yōu)選地,所述導(dǎo)電薄膜的材料為金、鉑或氮化鈦,所述導(dǎo)電聚合物為聚乙炔、聚吡咯、聚噻吩或聚苯胺。

12、優(yōu)選地,所述微電極陣列包含9~512個(gè)微電極,所述微電極直徑為1um~100um,微電極的間距為5um~200um。

13、優(yōu)選地,所述絕緣層的材料為二氧化硅、氮化硅、氮氧化硅、su8、聚酰亞胺或聚對(duì)二甲苯。

14、優(yōu)選地,所述納米材料為導(dǎo)電聚合物、碳納米管、納米金或納米鉑。

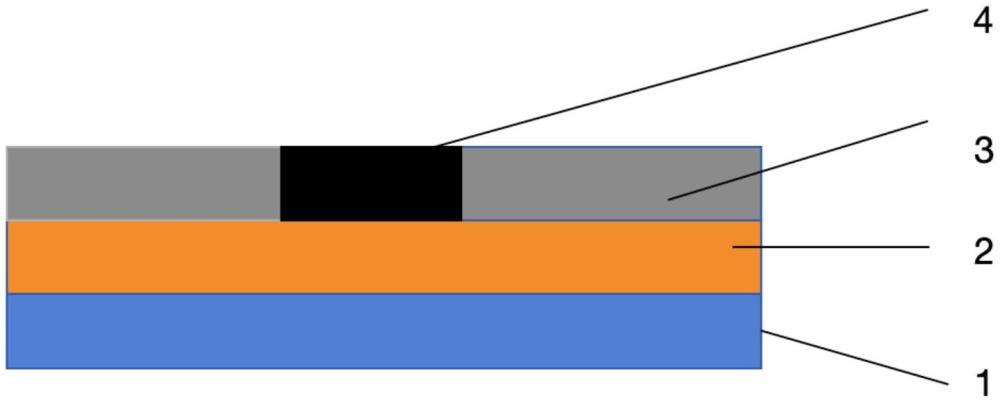

15、本發(fā)明還提供了一種所述的離體微電極陣列芯片的制備方法制得離體微電極陣列芯片,包括絕緣基底,位于絕緣基底上的微電極陣列,以及位于微電極陣列上的絕緣層和納米材料。

16、與現(xiàn)有技術(shù)相比,本發(fā)明的有益效果為:

17、本發(fā)明利用3d技術(shù)制備在絕緣基底表面制備出微電極陣列和導(dǎo)線,解決了現(xiàn)有mems微納加工成本高時(shí)間長(zhǎng)的問(wèn)題,提供了制備精度、節(jié)省時(shí)間,且節(jié)省成本。

技術(shù)特征:

1.一種離體微電極陣列芯片的制備方法,其特征在于,包括:

2.根據(jù)權(quán)利要求1所述的離體微電極陣列芯片的制備方法,其特征在于,所述絕緣基底的材料為硬質(zhì)透明絕緣材料,所述硬質(zhì)透明絕緣材料包括石英玻璃、聚氯乙烯或聚碳酸酯。

3.根據(jù)權(quán)利要求1所述的離體微電極陣列芯片的制備方法,其特征在于,所述絕緣基底的邊長(zhǎng)為25mm~80mm,厚度為1mm~2mm。

4.根據(jù)權(quán)利要求1所述的離體微電極陣列芯片的制備方法,其特征在于,所述微電極陣列的材料為導(dǎo)電薄膜材料,所述導(dǎo)電薄膜材料為金屬、金屬化合物或?qū)щ娋酆衔铩?/p>

5.根據(jù)權(quán)利要求4所述的離體微電極陣列芯片的制備方法,其特征在于,所述導(dǎo)電薄膜的材料為金、鉑或氮化鈦,所述導(dǎo)電聚合物為聚乙炔、聚吡咯、聚噻吩或聚苯胺。

6.根據(jù)權(quán)利要求1所述的離體微電極陣列芯片的制備方法,其特征在于,所述微電極陣列包含9~512個(gè)微電極,所述微電極直徑為1um~100um,微電極的間距為5um~200um。

7.根據(jù)權(quán)利要求1所述的離體微電極陣列芯片的制備方法,其特征在于,所述絕緣層的材料為二氧化硅、氮化硅、氮氧化硅、su8、聚酰亞胺或聚對(duì)二甲苯。

8.根據(jù)權(quán)利要求1所述的離體微電極陣列芯片的制備方法,其特征在于,所述納米材料為導(dǎo)電聚合物、碳納米管、納米金或納米鉑。

9.一種根據(jù)權(quán)利要求1-8所述的離體微電極陣列芯片的制備方法制得離體微電極陣列芯片,其特征在于,包括絕緣基底,位于絕緣基底上的微電極陣列,以及位于微電極陣列上的絕緣層和納米材料。

技術(shù)總結(jié)

本發(fā)明公開(kāi)了一種離體微電極陣列芯片及其制備方法,該制備方法包括清洗、吹干絕緣基底;采用3D打印技術(shù)在所述絕緣基底表面打印出微電極陣列;在微電極陣列上形成絕緣層,然后通過(guò)光刻和等離子刻蝕刻蝕絕緣層,暴露出微電極;通過(guò)電化學(xué)方法在微電極表面修飾納米材料。該制備方法能夠高效,成本較低的制備離體微電極陣列芯片。

技術(shù)研發(fā)人員:劉石碩,何恩慧,林芃

受保護(hù)的技術(shù)使用者:南湖腦機(jī)交叉研究院

技術(shù)研發(fā)日:

技術(shù)公布日:2025/4/6

- 還沒(méi)有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!