一種時鐘架構及處理模塊的制作方法

本技術涉及時鐘設計,涉及一種時鐘架構及處理模塊。

背景技術:

1、目前,隨著人工智能技術的蓬勃發展和廣泛應用,高速數據接口的需求呈現出爆炸式增長的趨勢。在這一背景下,對數據傳輸的帶寬、速率以及低延遲特性的要求愈發嚴苛,這無疑給高速電路設計帶來了前所未有的挑戰。時鐘電路作為高速電路設計的核心組成部分,其重要性不言而喻。時鐘如同數字電路的心臟,其穩定性和準確性的高低直接決定了系統能否發揮出最佳性能。

2、在復雜多變的電路系統中,多級電路級聯的情況屢見不鮮,各個模塊之間需要實現高效、精確的數據通信,以確保整個系統能夠流暢運行。而要實現這一點,模塊間的頻率同步就顯得尤為關鍵。頻率同步是確保數據在模塊間準確傳遞的基礎,一旦兩個模塊之間的頻率或相位出現較大偏差,數據通信就會受到影響,甚至可能導致數據傳輸錯誤,進而對整個系統的穩定性和可靠性構成嚴重威脅。

3、此外,在電路系統的設計中,時鐘的冗余和容錯機制也是不可或缺的重要環節。在實際應用中,主時鐘可能會因為各種原因出現故障或異常,如果沒有可以即時切換的備用時鐘,整個系統就有可能陷入癱瘓狀態。這種單點故障的風險對于追求高可靠性的系統來說,無疑是無法接受的。因此,在設計電路系統時,必須充分考慮到時鐘的冗余和容錯問題,以確保系統在主時鐘出現故障時能夠迅速切換到備用時鐘,從而維持系統的正常運行。

4、然而,現有的時鐘設計方案往往存在著結構復雜、成本高昂、難以維護等問題,難以滿足現代高速、高可靠性系統的實際需求。因此,在復雜的電路系統設計中,如何保證不同通信模塊間的頻率同步,以及如何實現主備時鐘的靈活切換,成為了設計者需要優先考慮并著力解決的關鍵問題。未來,隨著技術的不斷進步和創新,我們有理由相信,這些問題將會得到更加有效的解決,從而推動高速電路設計領域實現更加蓬勃的發展。

5、需要說明的是,在上述背景技術部分公開的信息僅用于加強對本技術的背景的理解,因此可以包括不構成對本領域普通技術人員已知的現有技術的信息。

技術實現思路

1、為了對披露的實施例的一些方面有基本的理解,下面給出了簡單的概括。所述概括不是泛泛評述,也不是要確定關鍵/重要組成元素或描繪這些實施例的保護范圍,而是作為后面的詳細說明的序言。

2、本公開實施例提供了一種時鐘架構及處理模塊,解決復雜系統中不同通信模塊間的頻率同步和主備時鐘切換問題,提高系統的穩定性和可靠性。

3、包括:

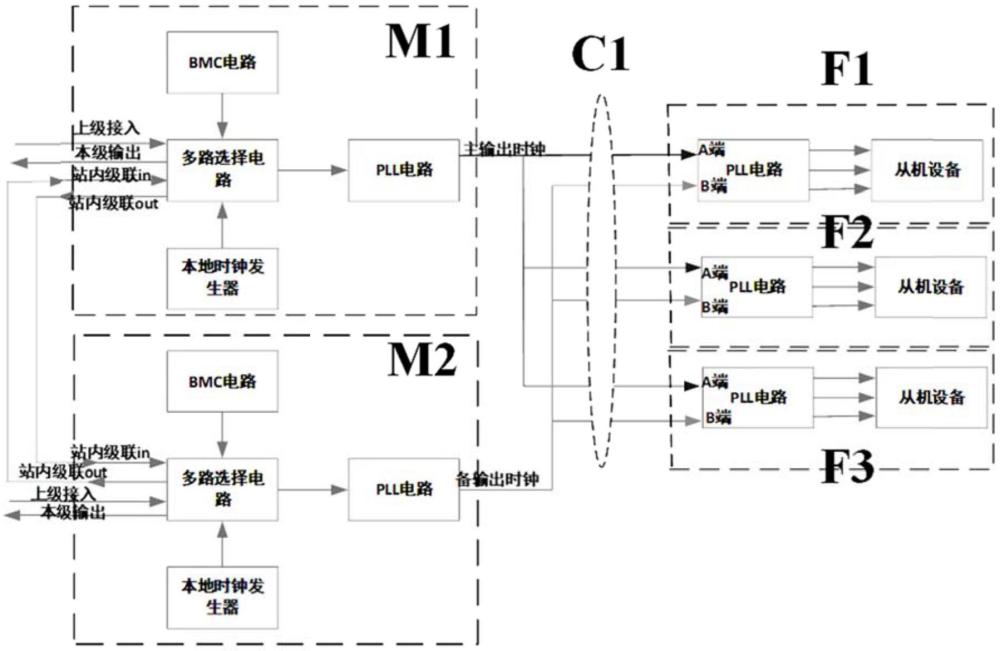

4、m1主時鐘模塊,包括本地時鐘發生器模塊、多路選擇電路、pll電路和bmc電路,其中多路選擇電路具有上級接入、站內級聯in和本地時鐘發生器三個輸入端,多路選擇電路的使能端口由bmc電路輸出信號控制,多路選擇電路的輸出信號連接到pll電路的輸入端;

5、m2備用時鐘模塊,包括本地時鐘發生器模塊、多路選擇電路、pll電路和bmc電路,用于在主時鐘異常時提供備用時鐘信號;

6、f功能模塊,用于實現系統中的功能,包括信息采集與處理、數據存儲,其時鐘設計部分由pll電路和從機設備組成,pll電路的輸入端口分別接入同級的主時鐘板和備用時鐘板輸出的時鐘信號,并輸出多個通道的時鐘信號,分別連接fpga模塊、cpu模塊、gpu模塊、交換機、高速serdes電路、retimer、bmc電路、其他通信模塊以及對外連接器;

7、c1連接器,用于連接m時鐘板和f功能板,確保時鐘信號的穩定傳輸。

8、優選的,所述bmc電路通過以太網口與pc端連接,pc端通過該以太網口寫入配置信息,使bmc電路選擇輸出使能信號,控制多路選擇電路的使能端口,進行時鐘信號的選通。通過bmc電路與pc端的以太網連接,用戶可以方便地寫入配置信息,從而動態選擇輸出使能信號,控制多路選擇電路的使能端口,實現時鐘信號的靈活選通。這種設計不僅提高了系統的靈活性,還使得時鐘管理更加便捷,能夠適應不同應用場景的需求變化。

9、優選的,所述f功能模塊中的pll電路內部進行時鐘偏斜的去除和相位的對齊,保證不同模塊之間的頻率同步。f功能模塊中的pll電路內部進行時鐘偏斜的去除和相位的對齊,確保了不同模塊之間的高精度頻率同步。這不僅提高了數據傳輸的準確性和穩定性,還有助于優化整體系統性能,特別是在對時間敏感的應用中,如高速通信、實時控制等。

10、優選的,pll輸出的第一通道連接fpga模塊;pll輸出的第二通道連接cpu模塊;pll輸出的第三通道連接gpu模塊;pll輸出的第四通道連接交換機;pll輸出的第五通道連接高速serdes電路;pll輸出的第六通道連接retimer;pll輸出的第七通道連接bmc電路;pll輸出的第八通道連接其他通信模塊;pll輸出的第九通道連接對外連接器,所述對外連接器為pcie接口;所述pll輸出作為其連接部分的工作參考時鐘。pll輸出的多個通道分別連接了fpga、cpu、gpu、交換機、高速serdes電路、retimer、bmc電路以及其他通信模塊,甚至包括對外連接器如pcie接口,提供了全面的時鐘支持。這種設計使得系統能夠集成多種高性能組件,同時保持時鐘信號的穩定性和一致性。

11、優選的,所述f功能模塊包括f1模塊、f2模塊和f3模塊。

12、優選的,所述m1主時鐘模塊和m2備用時鐘模塊中的本地時鐘發生器時鐘源包括無源晶體、標準封裝有源晶振、壓控式的晶振、帶溫度補償的晶振或恒溫晶振。m1主時鐘模塊和m2備用時鐘模塊中的本地時鐘發生器采用了多種時鐘源選項,包括無源晶體、標準封裝有源晶振、壓控式的晶振、帶溫度補償的晶振或恒溫晶振,確保了時鐘源的多樣性和高可靠性。在主時鐘故障時,備用時鐘能夠迅速切換,避免系統癱瘓,提高了系統的容錯能力和穩定性。

13、優選的,所述c1連接器采用背板形式,背板上的高速連接器插損不超過1db,背板上的整個信號走線插損不超過6db。c1連接器采用背板形式,背板上的高速連接器插損不超過1db,整個信號走線插損不超過6db,有效降低了信號傳輸過程中的損耗,保證了時鐘信號的完整性和質量。

14、優選的,該時鐘架構及處理模塊支持站內級聯和多級級聯。該時鐘架構及處理模塊支持站內級聯和多級級聯,使得系統能夠輕松擴展,適應更大規模的網絡或系統需求。同時,通過以太網網口作為輸出接口,輸出時鐘信號的頻率采用秒脈沖,進一步增強了系統的兼容性和可擴展性。

15、優選的,所述站內級聯m1主時鐘模塊和m2備用時鐘模塊相互輸出的時鐘信號通過以太網網口作為輸出接口,輸出時鐘信號的頻率采用秒脈沖。

16、本公開實施例提供的一種時鐘架構及處理模塊,針對復雜的系統中不同通信模塊間的頻率同步以及主備時鐘切換的問題,提出了一種創新的時鐘架構及處理模塊設計方法。該設計方案具有以下顯著的有益效果:

17、采用單獨的時鐘板產生系統時鐘,并供給其他功能板卡使用,有效保證了整個站內的時鐘同步。這一設計解決了因時鐘頻率相位偏差過大而導致的通信出錯問題,提升了系統的穩定性和可靠性。

18、設計了獨立的主備時鐘板,當主時鐘模塊出現異常時,備用時鐘模塊能夠迅速接管工作,確保系統能夠持續正常工作。這種冗余設計大大提高了系統的容錯能力和抗風險能力。

19、時鐘設計相對簡單,既解決了不同模塊之間的頻率同步問題,又方便了多級級聯,能夠滿足不同場景下的需求。無論是站內級聯還是站間級聯,都能通過簡單的接口和配置實現,提高了系統的靈活性和可擴展性。

20、本地時鐘發生器提供了多種時鐘源選擇,包括頻率穩定度較高的恒溫晶振ocxo等,適用于對頻率穩定度要求較高的場景,進一步提升了系統時鐘的準確性和穩定性。

21、綜上所述,本發明提出的時鐘架構及處理模塊設計方法在提升系統穩定性、增強容錯能力、簡化設計復雜度以及提高頻率穩定度等方面均表現出了顯著的有益效果。

22、以上的總體描述和下文中的描述僅是示例性和解釋性的,不用于限制本技術。

- 還沒有人留言評論。精彩留言會獲得點贊!