一種微觀電路模型區域分解建模方法和裝置

本發明涉及微觀電路模塊降階領域,特別是指一種微觀電路模型區域分解建模方法和裝置。

背景技術:

1、互連電路是集成電路的關鍵技術之一,決定了集成電路數據傳輸速度和信號完整性性能。隨著互連電路不斷向多層疊高密度方向發展,互連電路信號完整性分析所需的模型階數快速增長。有研究者開創性地提出基于物理等效的微觀電路模型,但是擴展性仍無法滿足大規模電路分析的需求。本項目將基于微觀電路模型開展大規模電路區域分解建模方法研究。

2、基于電路模型的數學等效降階方法電路模型,例如部分原件等效電路(partialelement?equivalent?circuit,peec),使用具有物理意義的電容、電感和電阻描述集成電路中的電磁場、輻射、損耗等效應,可利用spice求解時域和頻域響應,被廣泛應用在封裝、天線、電磁兼容等領域。在變換過程前中期,節點數雖然減少,支路數卻持續增加,反而導致模型階數大幅增加。此外由于只能處理電容模型,需要對大規模電位系數矩陣求逆。

3、針對大規模集成電路分析問題,微觀電路模型避免了使用矩陣求逆無法獲得精確解的瓶頸,有效降低模型仿真時間。然而,還存在以下科學與技術難題:gpu有限內存帶來的擴展性問題:利用gpu加速微觀電路模型算法時,工業級集成電路模型數據量遠大于gpu內存,因而每次迭代需要一次cpu-gpu間數據傳輸。cpu-gpu間傳輸速度只有gpu計算速度的萬分之一,導致gpu長期處在等待數據而加速算法失敗。

技術實現思路

1、本發明的主要目的在于克服現有技術中的上述缺陷,提出一種微觀電路模型區域分解建模方法和裝置。

2、本發明采用如下技術方案:

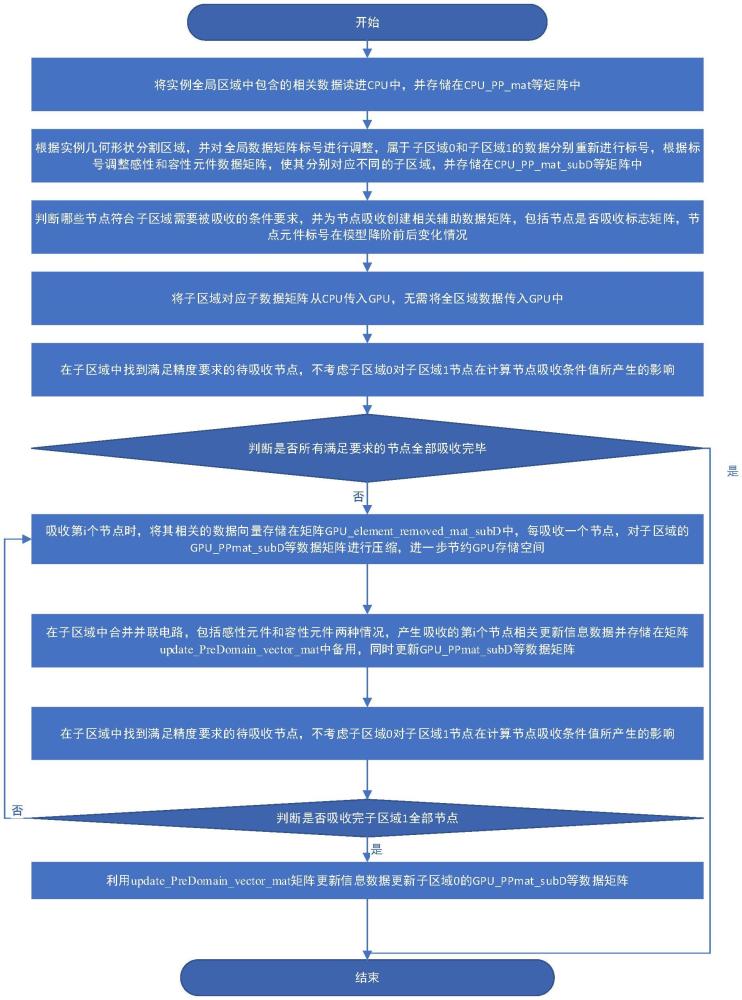

3、一種微觀電路模型區域分解建模方法,包括如下:

4、在cpu中將大規模電磁問題的微觀等效電路模型劃分成若干個子區域,得到所述子區域對應的數據矩陣;

5、在gpu中創建與所述子區域對應的降階矩陣,依次對若干所述子區域進行降階,直至若干所述子區域降階完畢:將其中一所述子區域的數據矩陣傳入對應的所述降階矩陣中進行處理以實現所述子區域的模型降階,更新所述降階矩陣中的所述數據矩陣并在該子區域的模型降階完畢后生成信息數據以傳遞若干所述子區域之間的相關性,下一所述子區域的模型降階時結合所述信息數據更新其對應的所述降階矩陣中的所述數據矩陣,以此類推。

6、根據所述微觀等效電路模型在三維直角坐標系中的特性劃分若干個子區域,所述子區域對應的數據矩陣包括有:包括電容之間的耦合矩陣pp,節點之間的電感和節點之間的電感之間的耦合矩陣m,節點上的電感與節點之間的電感之間的耦合矩陣mpm,節點上的電感與節點上的電感之間的耦合矩陣mpp、標號映射矩陣以及矩陣mpmm,所述矩陣mpmm存儲有所述子區域所有節點之間電感與所有節點上的電感之間的耦合值,所述標號映射矩陣存儲所述子區域劃分前的節點標號和劃分后的節點標號的映射關系。

7、將所述微觀等效電路模型劃分成若干個子區域,所述子區域的數據矩陣還包括標號矩陣,所述標號矩陣存儲每個子區域的節點的起始標號和結束標號,在進行所述子區域降階時,直接根據所述標號矩陣來選擇對應的所述子區域的數據矩陣。

8、在gpu中還創建過渡矩陣以存儲所述子區域降階所需要用到的部分數據,所述子區域的模型降階包括:

9、利用min方法計算出子區域的每個節點的吸收條件值△,且找到吸收條件值最小的節點最先吸收,其他節點在吸收此節點并更新完畢所有上述矩陣之后再通過min方法分別計算條件值,迭代尋找需要吸收的下一個吸收條件值最小的節點,所述吸收條件值△計算公式如下:

10、

11、其中,mii代表新增的電感元件的自耦合值,mss代表原本存在的電感元件的自耦合值,msi代表新增的電感元件和原本存在的電感元件之間的互耦合值,pii代表新增的電容元件的自耦合值,pss代表原本存在的電容元件的自耦合值,psi代表新增的電容元件和原本存在的電容元件之間的互耦合值,代表微波器件工作最大頻率;

12、每吸收一個節點進入一次循環:首先根據每次迭代需要,將要吸收的節點k及其周圍連接的若干節點i相關耦合數據值從所述數據矩陣中取出,放置于過渡矩陣xrm中:

13、

14、ppi代表電容自耦矩陣、mi代表電感自耦矩陣、mpmi代表若干節點i上的電感與子區域其余節點之間電感的耦合矩陣、mppi代表上述若干節點i上的電感自耦矩陣、mpmk代表節點k上的電感與子區域其余節點之間的電感耦合矩陣。

15、每吸收一個節點,對所述子區域的數據矩陣進行壓縮,具體為:將所述子區域對應的數據矩陣中最后一行和最后一列數據移動到被吸收掉的節點對應的數據位置。

16、在所述子區域的模型降階完畢后生成信息數據如下:

17、

18、具體地,xpk、xmk、xpmk分別代表第i組子區域吸收第k個節點產生的更新信息,n代表這個節點k周圍連接的節點i的總個數,包括電容與全部電容之間的耦合數據,節點之間電感的互耦數據、節點上電感與節點之間電感之間耦合數據;每個子區域降階產生的更新信息xi組成矩陣x,利用所述矩陣x更新所有所述子區域對應的數據矩陣,n代表一共需要吸收的子區域總個數。

19、下一所述子區域的模型降階時結合所述信息數據更新其對應的所述降階矩陣中的所述數據矩陣,具體如下:

20、pp=pp+c0xpt·xp

21、m=m+c1xmt·xm

22、mpp=mpp+c2xpmt·xp+c3xpmt·xpm

23、mpm=mpm+c4xpmt·xm+c5xpt·xm;

24、其中,c0、c1、c2、c3、c4、c5為所述微觀電路模型變換時的常量,xp表示電容元件之間的互耦信息、xm表示電感元件之間的互耦信息、xpm表示ppi支路上電感與節點之間電感之間的互耦信息。

25、所述子區域的模型降階包括合并并聯支路,當并聯支路合并時,電路中所有的互阻抗都需要更新,則并聯電路元件以及相關的互耦羅列如下:

26、并聯支路s的自阻抗為:

27、

28、并聯支路s與剩余電感支路或其他ppi支路之間的互阻抗為:

29、z'rs=[(yss+ysi)zrs+(yii+ysi)zri]/yt;

30、z'os=[(yss+ysi)zos+(yii+ysi)zoi]/yt;

31、其中yss,yii分別表示合并兩條并聯支路的其中一個支路的自耦合導納,ysi表示兩條并聯支路的互耦合導納,zrs表示兩條ppi支路的其中一條支路與其他不參與合并ppi支路的普通支路上的耦合阻抗,zos表示其中一條支路與其他ppi支路的耦合阻抗,zri表示兩條并聯支路的另一條支路與其他不參與合并ppi支路的普通支路上的耦合阻抗、zoi表示兩條并聯支路中的另一條支路與其他ppi支路的耦合阻抗,z'rs表示合并兩條ppi支路之后與其他不參與合并ppi支路的普通支路上的耦合阻抗,z'os表示合并兩條ppi支路之后與其他ppi支路的耦合阻抗。

32、其他ppi支路與剩余電感支路之間的互阻抗為:

33、

34、其中,z'oo表示其他ppi支路合并后的自耦合,zoo表示其他ppi支路合并前的自耦合,z'or表示合并ppi支路后其他ppi支路與普通支路之間的耦合,zor表示合并ppi支路前其他ppi支路與普通支路之間的耦合,z'rr表示合并ppi支路后其他普通支路的自耦合,zrr表示合并ppi支路前其他普通支路的自耦合。

35、一種微觀電路模型區域分解建模裝置,包括:

36、子區域劃分模塊,在cpu中將大規模電磁問題的微觀等效電路模型劃分成若干個子區域,得到所述子區域對應的數據矩陣;

37、降階模塊,在gpu中創建與所述子區域對應的降階矩陣,依次對若干所述子區域進行降階,直至若干所述子區域降階完畢:將其中一所述子區域的數據矩陣傳入對應的所述降階矩陣中進行處理以實現所述子區域的模型降階;

38、更新數據模塊,模型降階完畢后生成信息數據以傳遞若干所述子區域之間的相關性,下一所述子區域的模型降階時結合所述信息數據更新其對應的所述降階矩陣中的所述數據矩陣,更新完畢后繼續吸收另一個所述子區域中的節點,以此類推。

39、由上述對本發明的描述可知,與現有技術相比,本發明具有如下有益效果:

40、1.本發明所用到的區域分解建模方法非常適用于大規模微觀電路模型的模型降解中,將大規模的微觀電路模型分解成多個條狀子區域,使其數據矩陣大小滿足gpu有限的內存大小,使得微觀電路模型降解算法的擴展性大大增強。

41、2.利用分解區域之間的對稱關系和低相關性,可以用子區域數據中的幾個向量中的子區域對應數據,去迭代更新另一個矩陣中的數據,而無需使用全區域數據計算更新,極大程度減少cpu-gpu之間數據傳輸的次數,極大程度減少算法執行總時間。有利于微觀電路模型利用高性能gpu并行計算技術解決和分析大規模互聯封裝電路降階的問題。

42、3.微觀電路模型降階從最后一個子區域,從后向前迭代進行,先更新最后一個子區域,然后更新前一個子區域,這種更新節點的方式可以最大程度保持矩陣的數據存儲位置不變,可以極大降低在驗證計算結果正確性時的復雜度,提高程序的復用性。

- 還沒有人留言評論。精彩留言會獲得點贊!