一種硬件仿真系統(tǒng)、控制方法、電子設(shè)備及存儲介質(zhì)與流程

本申請涉及仿真模擬,尤其涉及一種硬件仿真系統(tǒng)、控制方法、電子設(shè)備及存儲介質(zhì)。

背景技術(shù):

1、片上系統(tǒng)(system?on?chip,簡稱:soc)等集成電路的硬件設(shè)計較為復雜,涉及眾多功能模塊集成,所以在硬件實現(xiàn)前進行仿真模擬很有必要,可提前確認其硬件架構(gòu)合理性,以提高soc的開發(fā)效率。

2、其中,如systemc等硬件仿真進程是電子系統(tǒng)級設(shè)計(electronic?system?level,簡稱:esl)的重要工具,支持事務級建模(transaction?level?modeling,簡稱:tlm),能夠?qū)oc整個電路系統(tǒng)的功能、架構(gòu)進行描述,同時又不陷入硬件電路繁雜的信號時序、門電路之中。

3、但是,在多核處理器的場景下,硬件仿真進程只能應用于單個處理器核心,當硬件仿真進程與其他處理器核心的進程進行聯(lián)和仿真時,常常出現(xiàn)硬件仿真進程和其他處理器核心的進程之間的共享資源鎖定時間較長的情況下,降低了對集成電路的硬件仿真效率。

技術(shù)實現(xiàn)思路

1、本申請?zhí)峁┝艘环N硬件仿真系統(tǒng)、控制方法、電子設(shè)備及存儲介質(zhì),以至少解決相關(guān)技術(shù)中硬件仿真進程和其他處理器核心的進程之間的共享資源鎖定時間較長,降低了對集成電路的硬件仿真效率的問題。

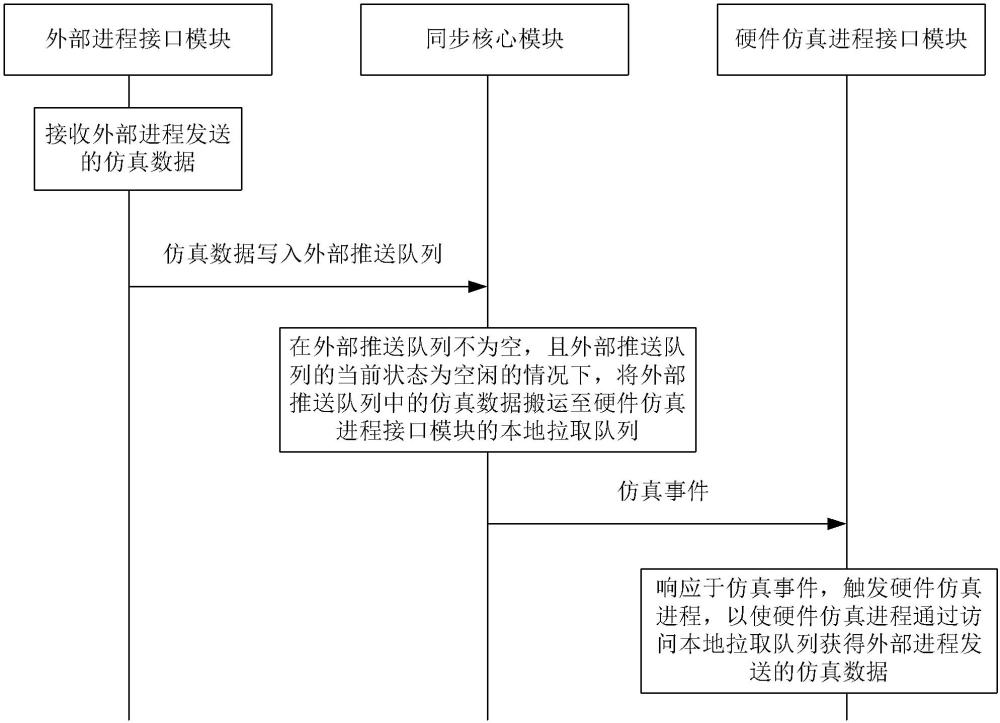

2、本申請?zhí)峁┝艘环N硬件仿真系統(tǒng),包括:外部進程接口模塊、同步核心模塊和硬件仿真進程接口模塊;

3、外部進程接口模塊用于接收外部進程發(fā)送的仿真數(shù)據(jù),并將仿真數(shù)據(jù)寫入外部推送隊列;

4、同步核心模塊用于在外部推送隊列不為空,且外部推送隊列的當前狀態(tài)為空閑的情況下,將外部推送隊列中的仿真數(shù)據(jù)搬運至硬件仿真進程接口模塊的本地拉取隊列,并向硬件仿真進程接口模塊發(fā)送仿真事件;

5、硬件仿真進程接口模塊用于接收仿真事件,并響應于仿真事件,觸發(fā)硬件仿真進程,以使硬件仿真進程通過訪問本地拉取隊列獲得外部進程發(fā)送的仿真數(shù)據(jù)。

6、本申請還提供了一種硬件仿真系統(tǒng)控制方法,應用于上述任一種硬件仿真系統(tǒng),該方法包括:

7、當?shù)玫酵獠窟M程發(fā)送的仿真數(shù)據(jù)時,控制外部進程接口模塊將仿真數(shù)據(jù)寫入外部推送隊列;

8、在外部推送隊列不為空,且外部推送隊列的當前狀態(tài)為空閑的情況下,控制同步核心模塊將外部推送隊列中的仿真數(shù)據(jù)搬運至硬件仿真進程接口模塊的本地拉取隊列;

9、控制硬件仿真進程接口模塊觸發(fā)硬件仿真進程,以使硬件仿真進程通過訪問本地拉取隊列獲得外部進程發(fā)送的仿真數(shù)據(jù)。

10、本申請還提供了一種電子設(shè)備,包括:存儲器,用于存儲計算機程序;處理器,用于執(zhí)行計算機程序時實現(xiàn)上述任一種硬件仿真系統(tǒng)控制的步驟。

11、本申請還提供了一種計算機可讀存儲介質(zhì),計算機可讀存儲介質(zhì)中存儲有計算機程序,其中,計算機程序被處理器執(zhí)行時實現(xiàn)上述任一種硬件仿真系統(tǒng)控制的步驟。

12、本申請還提供了一種計算機程序產(chǎn)品,包括計算機程序,計算機程序被處理器執(zhí)行時實現(xiàn)上述任一種硬件仿真系統(tǒng)控制的步驟。

13、通過本申請,由于外部進程接口模塊、同步核心模塊和硬件仿真進程接口模塊相互配合,外部進程接口模塊將仿真數(shù)據(jù)寫入同步核心模塊的外部推送隊列,同步核心模塊在條件滿足時將數(shù)據(jù)搬運至硬件仿真進程接口模塊的本地拉取隊列,硬件仿真進程通過訪問本地拉取隊列即可獲取數(shù)據(jù),整個過程減少了共享資源訪問沖突。因此,解決相關(guān)技術(shù)中硬件仿真進程和其他處理器核心的進程之間的共享資源鎖定時間較長的技術(shù)問題,達到提高對集成電路的硬件仿真效率的技術(shù)效果。

技術(shù)特征:

1.一種硬件仿真系統(tǒng),其特征在于,包括:外部進程接口模塊、同步核心模塊和硬件仿真進程接口模塊;

2.根據(jù)權(quán)利要求1所述的硬件仿真系統(tǒng),其特征在于,所述系統(tǒng)還包括:

3.根據(jù)權(quán)利要求2所述的硬件仿真系統(tǒng),其特征在于,所述外部進程接口模塊,用于:

4.根據(jù)權(quán)利要求3所述的硬件仿真系統(tǒng),其特征在于,所述同步核心模塊,用于:

5.根據(jù)權(quán)利要求1所述的硬件仿真系統(tǒng),其特征在于,所述同步核心模塊,還用于:

6.根據(jù)權(quán)利要求5所述的硬件仿真系統(tǒng),其特征在于,所述同步核心模塊,還用于:

7.根據(jù)權(quán)利要求1所述的硬件仿真系統(tǒng),其特征在于,所述同步核心模塊,用于:

8.根據(jù)權(quán)利要求1所述的硬件仿真系統(tǒng),其特征在于,所述同步核心模塊包括:仿真維持單元;

9.根據(jù)權(quán)利要求8所述的硬件仿真系統(tǒng),其特征在于,所述仿真維持單元,用于:

10.根據(jù)權(quán)利要求1所述的硬件仿真系統(tǒng),其特征在于,所述外部進程和所述硬件仿真進程運行在不同的處理器核心。

11.根據(jù)權(quán)利要求1所述的硬件仿真系統(tǒng),其特征在于,所述仿真數(shù)據(jù)至少包括硬件仿真事件和所述硬件仿真事件的仿真關(guān)鍵數(shù)據(jù)。

12.一種硬件仿真系統(tǒng)控制方法,應用于如權(quán)利要求1至11任一項所述的硬件仿真系統(tǒng),其特征在于,所述方法包括:

13.一種電子設(shè)備,其特征在于,包括:

14.一種計算機可讀存儲介質(zhì),其特征在于,所述計算機可讀存儲介質(zhì)中存儲有計算機程序,其中,所述計算機程序被處理器執(zhí)行時實現(xiàn)如權(quán)利要求12所述硬件仿真系統(tǒng)控制方法的步驟。

15.一種計算機程序產(chǎn)品,包括計算機程序,其特征在于,所述計算機程序被處理器執(zhí)行時實現(xiàn)如權(quán)利要求12所述硬件仿真系統(tǒng)控制方法的步驟。

技術(shù)總結(jié)

本申請公開了一種硬件仿真系統(tǒng)、控制方法、電子設(shè)備及存儲介質(zhì),涉及仿真模擬技術(shù)領(lǐng)域,由于外部進程接口模塊、同步核心模塊和硬件仿真進程接口模塊相互配合,外部進程接口模塊將仿真數(shù)據(jù)寫入同步核心模塊的外部推送隊列,同步核心模塊在條件滿足時將數(shù)據(jù)搬運至硬件仿真進程接口模塊的本地拉取隊列,硬件仿真進程通過訪問本地拉取隊列即可獲取數(shù)據(jù),整個過程減少了共享資源訪問沖突。因此,解決相關(guān)技術(shù)中硬件仿真進程和其他處理器核心的進程之間的共享資源鎖定時間較長的技術(shù)問題,達到提高對集成電路的硬件仿真效率的技術(shù)效果。

技術(shù)研發(fā)人員:姜麗云,李樹青,王江,孫華錦

受保護的技術(shù)使用者:山東云海國創(chuàng)云計算裝備產(chǎn)業(yè)創(chuàng)新中心有限公司

技術(shù)研發(fā)日:

技術(shù)公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!