多次寫入只讀存儲器陣列的制作方法

本發明屬于存儲器陣列領域,且特別關于一種多次寫入只讀存儲器陣列。

背景技術:

1、互補式金屬氧化半導體(complementary?metal?oxide?semiconductor,cmos)制程技術已成為特殊應用集成電路(application?specific?integrated?circuit,asic)的常用制造方法。在計算機信息產品發達的今天,電子式可清除程序化只讀存儲器(electricallyerasable?programmable?read?onlymemory,eeprom)由于具備有電性編寫和抹除資料的非揮發性存儲器功能,且在電源關掉后資料不會消失,所以被廣泛使用于電子產品上。

2、非揮發性存儲器是可程序化的,其用以儲存電荷以改變存儲器的晶體管的閘極電壓,或不儲存電荷以留下原存儲器的晶體管的閘極電壓。抹除操作則是將儲存在非揮發性存儲器中的所有電荷移除,使得所有非揮發性存儲器回到原存儲器的晶體管的閘極電壓。非揮發性存儲器在燒錄時,其內部的開關元件會被斷開或形成導通。為了程序化非揮發性存儲器陣列,需要施加一定的電壓和電流,這樣才能打開或關斷相對應的開關元件。為了提高只讀存儲器的穩定性、可靠性、功耗效率、儲存密度和讀取速度,閘極電容的面積通常較大。然而,閘極電容的面積愈大,成本愈高,市場上也較無競爭力。

3、因此,本發明針對上述的困擾,提出一種多次寫入只讀存儲器陣列,以解決現有技術中的問題。

技術實現思路

1、本發明提供一種多次寫入只讀存儲器陣列,其可大幅減少電容的面積。

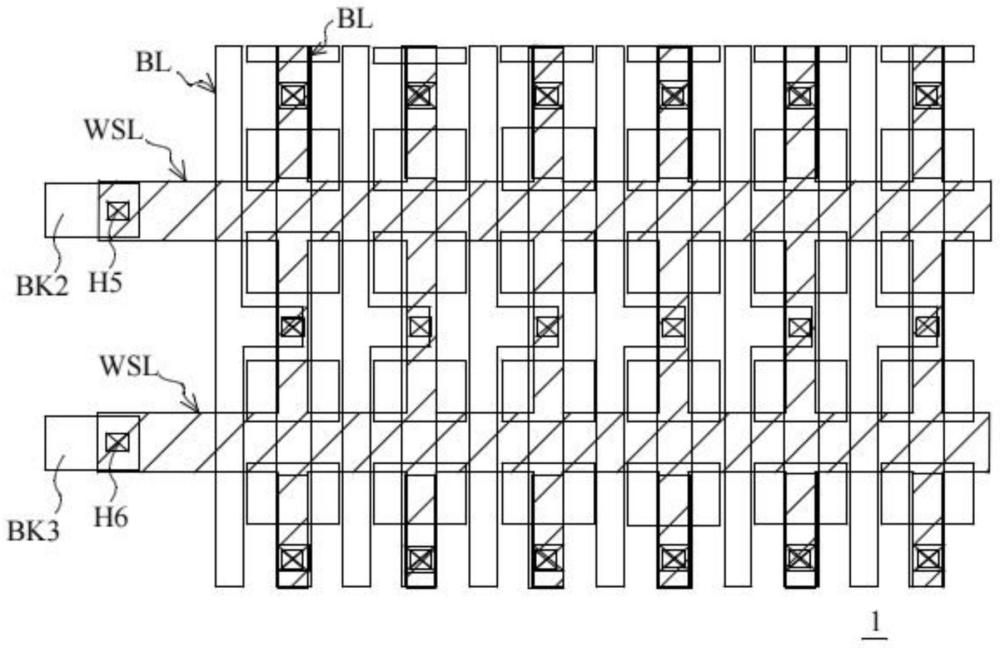

2、在本發明的一實施例中,提供一種多次寫入只讀存儲器陣列,其包括多條平行的字符共源線、多條平行的位元線與多個子存儲器陣列。字符共源線包括一第一字符共源線與一第二字符共源線,位元線與字符共源線互相垂直。位元線包括一第一位元線與一第二位元線,每一子存儲器陣列耦接兩條字符共源線與兩條位元線。每一子存儲器陣列包括一第一記憶晶胞、一第二記憶晶胞、一第三記憶晶胞與一第四記憶晶胞。第一記憶晶胞耦接第一字符共源線與第一位元線,第二記憶晶胞耦接第一字符共源線與第二位元線,第三記憶晶胞耦接第二字符共源線與第二位元線,第四記憶晶胞耦接第二字符共源線與第一位元線。

3、在本發明的一實施例中,第一記憶晶胞與第二記憶晶胞以第一字符共源線為軸對稱設置,第三記憶晶胞與第四記憶晶胞以第二字符共源線為軸對稱設置,第二記憶晶胞與第三記憶晶胞位于第一記憶晶胞與第四記憶晶胞之間。

4、在本發明的一實施例中,第一記憶晶胞、第二記憶晶胞、第三記憶晶胞與第四記憶晶胞設于具有第一導電型的一半導體區域中,第一記憶晶胞、第二記憶晶胞、第三記憶晶胞與第四記憶晶胞共同包括一第一閘極介電區塊、一第二閘極介電區塊、一第三閘極介電區塊、一第四閘極介電區塊、一第一導電閘極、一第二導電閘極、一第三導電閘極、一第四導電閘極、一第一重摻雜區、一第二重摻雜區、一第三重摻雜區、一第四重摻雜區與一第五重摻雜區。第一閘極介電區塊、第二閘極介電區塊、第三閘極介電區塊與第四閘極介電區塊分別設于半導體區域上。第一導電閘極、第二導電閘極、第三導電閘極與第四導電閘極分別設于第一閘極介電區塊、第二閘極介電區塊、第三閘極介電區塊與第四閘極介電區塊上。第一重摻雜區與第二重摻雜區設于半導體區域中,并分別位于第一導電閘極的正下方的半導體區域的相異兩側,且分別耦接第一位元線與第一字符共源線。第一重摻雜區與第二重摻雜區具有與第一導電型相反的第二導電型。第三重摻雜區設于半導體區域中,第二重摻雜區與第三重摻雜區分別位于第二導電閘極的正下方的半導體區域的相異兩側。第三重摻雜區耦接第二位元線,其中第三重摻雜區具有第二導電型。第四重摻雜區設于半導體區域中,第三重摻雜區與第四重摻雜區分別位于第三導電閘極的正下方的半導體區域的相異兩側。第四重摻雜區耦接第二字符共源線,其中第四重摻雜區具有第二導電型。第五重摻雜區設于半導體區域中,第四重摻雜區與第五重摻雜區分別位于第四導電閘極的正下方的半導體區域的相異兩側。第五重摻雜區耦接第一位元線,其中第五重摻雜區具有第二導電型。

5、在本發明的一實施例中,第一導電型為p型,第二導電型為n型。

6、在本發明的一實施例中,第一記憶晶胞被選擇進行程序化(programming)動作時,半導體區域耦合接地電壓,第一位元線耦合中電壓或接地電壓,第一字符共源線耦合中電壓或高電壓,其中高電壓大于中電壓,中電壓大于接地電壓。

7、在本發明的一實施例中,第一記憶晶胞未被選擇進行程序化(programming)動作時,半導體區域耦合接地電壓,第一位元線電性浮接或耦合低電壓,第一字符共源線耦合接地電壓,其中低電壓大于接地電壓。

8、在本發明的一實施例中,第一記憶晶胞被選擇進行抹除動作時,半導體區域耦合接地電壓,第一位元線耦合高電壓,第一字符共源線耦合接地電壓,其中高電壓大于接地電壓。

9、在本發明的一實施例中,第一記憶晶胞未被選擇進行抹除動作時,半導體區域耦合接地電壓,第一位元線電性浮接,第一字符共源線耦合低電壓或中電壓,其中中電壓大于低電壓,低電壓大于接地電壓。

10、在本發明的一實施例中,第一記憶晶胞被選擇進行讀取動作時,半導體區域與第一位元線耦合接地電壓,第一字符共源線耦合低電壓,其中低電壓大于接地電壓。

11、在本發明的一實施例中,第一記憶晶胞未被選擇進行讀取動作時,半導體區域、第一位元線與第一字符共源線耦合接地電壓。

12、在本發明的一實施例中,第一導電型為n型,第二導電型為p型。

13、在本發明的一實施例中,第一記憶晶胞被選擇進行程序化(programming)動作時,半導體區域耦合高電壓,第一位元線耦合中電壓或高電壓,第一字符共源線耦合中電壓或接地電壓,其中高電壓大于中電壓,中電壓大于接地電壓。

14、在本發明的一實施例中,第一記憶晶胞未被選擇進行程序化(programming)動作時,半導體區域耦合高電壓,第一位元線電性浮接或耦合中電壓,第一字符共源線耦合高電壓,其中高電壓大于中電壓。

15、在本發明的一實施例中,第一記憶晶胞被選擇進行抹除動作時,半導體區域耦合高電壓,第一位元線耦合接地電壓,第一字符共源線耦合高電壓,其中高電壓大于接地電壓。

16、在本發明的一實施例中,第一記憶晶胞未被選擇進行抹除動作時,半導體區域耦合高電壓,第一位元線電性浮接,第一字符共源線耦合中電壓,其中高電壓大于中電壓。

17、在本發明的一實施例中,第一記憶晶胞被選擇進行讀取動作時,半導體區域與第一位元線耦合中電壓,第一字符共源線耦合低電壓,其中中電壓大于低電壓。

18、在本發明的一實施例中,第一記憶晶胞未被選擇進行讀取動作時,半導體區域、第一位元線與第一字符共源線耦合中電壓,其中中電壓大于接地電壓。

19、在本發明的一實施例中,半導體區域為半導體基板或設于半導體基板上的磊晶層。

20、基于上述,多次寫入只讀存儲器陣列從場效晶體管的汲極提供閘極電壓,以大幅減少電容的面積。

- 還沒有人留言評論。精彩留言會獲得點贊!