一種緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法

本發(fā)明屬于阻變存儲(chǔ)器,涉及非易失性憶阻器編程方法,具體涉及一種緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法。

背景技術(shù):

1、傳統(tǒng)馮·諾伊曼計(jì)算架構(gòu)因其存儲(chǔ)單元與計(jì)算單元分離的結(jié)構(gòu),在進(jìn)行數(shù)據(jù)密集型計(jì)算任務(wù)如人工智能計(jì)算、科學(xué)數(shù)值計(jì)算等任務(wù)時(shí),面臨計(jì)算延時(shí)大和能效低的問(wèn)題。受腦啟發(fā)的存算一體架構(gòu)則在存儲(chǔ)的局部完成計(jì)算,具有高并行度,從而大幅度提高計(jì)算速度和能效。在眾多存算一體單元里,非易失性憶阻器具有集成密度高、cmos工藝兼容、操作速度快、非易失等優(yōu)勢(shì),是實(shí)現(xiàn)高效存算一體架構(gòu)強(qiáng)有力的候選器件。

2、非易失性憶阻器的電導(dǎo)狀態(tài)能夠在外加超閾值電壓的刺激下發(fā)生改變,并且在理想情況下,新的電導(dǎo)狀態(tài)在撤去電壓刺激后能夠長(zhǎng)時(shí)間保持。若需提高憶阻器的電導(dǎo),則需要進(jìn)行置位操作(set);若需降低憶阻器的電導(dǎo),則需要進(jìn)行復(fù)位操作(reset)。對(duì)于非易失性憶阻器的多值或模擬電導(dǎo)值的編程,一般常用的編程方法為寫入驗(yàn)證方法,通過(guò)反復(fù)施加set或reset的寫入脈沖來(lái)改變憶阻器電導(dǎo),并以非常小的驗(yàn)證電壓讀取當(dāng)前電導(dǎo)來(lái)判斷其是否已達(dá)到目標(biāo)電導(dǎo)。其中,在寫入過(guò)程中若經(jīng)判斷當(dāng)前的操作類型(set或reset)應(yīng)與前一次操作類型一樣,則當(dāng)前的寫入脈沖脈寬一樣、幅值增加。雖然憶阻器在這種編程方法下能夠很好地被編程到目標(biāo)電導(dǎo),但電導(dǎo)在編程后的短時(shí)間內(nèi)會(huì)發(fā)生弛豫,隨機(jī)漂移并偏離目標(biāo)電導(dǎo)。這源自于憶阻器本身工作機(jī)制,在完成編程操作后,不穩(wěn)定的導(dǎo)電細(xì)絲、氧空位的自發(fā)產(chǎn)生和遷移等會(huì)改變電導(dǎo)狀態(tài)。對(duì)于要求所存儲(chǔ)的信息非常穩(wěn)定且準(zhǔn)確的諸多應(yīng)用場(chǎng)景,如科學(xué)數(shù)值計(jì)算、基于高效時(shí)間編碼的脈沖神經(jīng)網(wǎng)絡(luò)計(jì)算等,電導(dǎo)弛豫會(huì)導(dǎo)致計(jì)算結(jié)果失真、信息丟失、系統(tǒng)計(jì)算性能下降等問(wèn)題。因此,憶阻器的電導(dǎo)弛豫效應(yīng)為亟待克服的挑戰(zhàn)。

3、已被報(bào)道的針對(duì)緩解電導(dǎo)弛豫效應(yīng)所開(kāi)發(fā)的編程策略包括寫入—延遲—驗(yàn)證、反復(fù)寫入、大脈寬寫入、外圍讀電路參考電壓校準(zhǔn)等。然而,這些技術(shù)緩解電導(dǎo)弛豫的能力仍有限,其中包括弛豫后電導(dǎo)分布仍較大、策略僅對(duì)單一方向電導(dǎo)漂移有效等問(wèn)題。此外,當(dāng)中有的策略會(huì)引入更長(zhǎng)的編程時(shí)間,有的則需要更復(fù)雜的硬件電路支持,不利于實(shí)現(xiàn)大規(guī)模憶阻器存算一體系統(tǒng)。目前,成本低且同時(shí)能非常有效緩解電導(dǎo)雙向弛豫效應(yīng)的非易失性憶阻器編程方法還未被報(bào)道。

技術(shù)實(shí)現(xiàn)思路

1、為了克服上述非易失性憶阻器電導(dǎo)弛豫的問(wèn)題,本發(fā)明提出了一種能緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,大大提高所存儲(chǔ)電導(dǎo)狀態(tài)的準(zhǔn)確度。

2、本發(fā)明提供的技術(shù)方案如下:

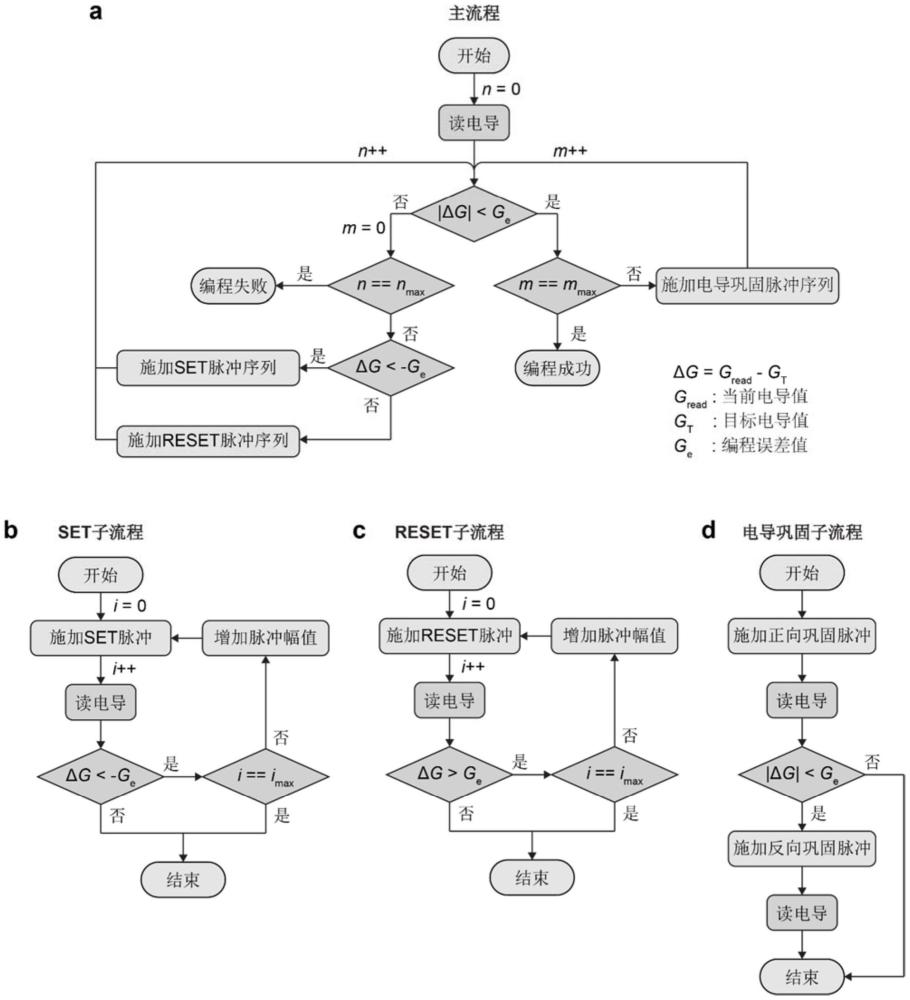

3、一種緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其中將對(duì)憶阻器進(jìn)行讀操作所得電導(dǎo)值、目標(biāo)電導(dǎo)值、可容許編程電導(dǎo)誤差分別記為gread、gt和ge,將讀操作所得電導(dǎo)值與目標(biāo)電導(dǎo)值的差距記為δg,即δg=gread-gt,總循環(huán)數(shù)記為n,電導(dǎo)鞏固循環(huán)數(shù)記為m,set或reset寫入脈沖連續(xù)施加的次數(shù)記為i,具體步驟包括如下:

4、1)編程開(kāi)始,讀取憶阻器當(dāng)前電導(dǎo)gread;

5、2)若gread處于目標(biāo)電導(dǎo)區(qū)間內(nèi)[gt-ge,gt+ge],即|δg|<ge,則直接進(jìn)入電導(dǎo)鞏固階段;否則進(jìn)行寫驗(yàn)證;其中進(jìn)行電導(dǎo)鞏固階段具體為,對(duì)m進(jìn)行判斷,若m==mmax,則編程成功;否則運(yùn)行電導(dǎo)鞏固子流程;即施加set方向亞閾值脈沖,隨后讀電導(dǎo);若此時(shí)不滿足|δg|<ge,則直接結(jié)束電導(dǎo)鞏固子流程;否則施加reset方向亞閾值脈沖,隨后讀電導(dǎo),結(jié)束電導(dǎo)鞏固子流程,并在結(jié)束電導(dǎo)鞏固子流程后,m變?yōu)閙+1,對(duì)電導(dǎo)鞏固子流程里所得gread進(jìn)行進(jìn)一步判斷;

6、3)若步驟2)中判定進(jìn)行寫驗(yàn)證,對(duì)n進(jìn)行判斷,若n==nmax,則編程失敗;否則繼續(xù)對(duì)gread進(jìn)行判斷;若gread低于目標(biāo)電導(dǎo)區(qū)間[gt-ge,gt+ge],即δg<-ge,則施加置位(set)脈沖序列;若gread高于目標(biāo)電導(dǎo)區(qū)間,即δg>ge,則施加復(fù)位(reset)脈沖序列。

7、進(jìn)一步,所述施加reset脈沖序列具體為,施加reset脈沖,i變?yōu)閕+1,隨后讀電導(dǎo);若此時(shí)仍滿足δg>ge且i≠imax,則增加reset脈沖幅值,并重復(fù)施加reset脈沖與進(jìn)行判斷;否則結(jié)束reset子流程,且n變?yōu)閚+1,重復(fù)步驟2)—3)。

8、進(jìn)一步,所述施加set脈沖序列具體為,施加set脈沖,i變?yōu)閕+1,隨后讀電導(dǎo);若此時(shí)仍滿足δg<-ge且i≠imax,則增加set脈沖幅值,并重復(fù)施加set脈沖與進(jìn)行判斷;否則結(jié)束set子流程,且n變?yōu)閚+1,重復(fù)步驟2)—3)。

9、本發(fā)明提供了能夠緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,當(dāng)器件成功被寫入到目標(biāo)電導(dǎo)區(qū)間內(nèi)時(shí),通過(guò)施加亞閾值正/反向脈沖對(duì)使電導(dǎo)狀態(tài)穩(wěn)定,若施加多次亞閾值脈沖對(duì)后且器件電導(dǎo)仍處于目標(biāo)電導(dǎo)區(qū)間內(nèi),則器件編程成功。與已有的緩解電導(dǎo)弛豫編程方案相比,本發(fā)明的編程方法操作更簡(jiǎn)單、編程速度更快,且適用于緩解電導(dǎo)雙向弛豫效應(yīng),效果也較好,對(duì)于要求能夠準(zhǔn)確存儲(chǔ)數(shù)據(jù)的應(yīng)用如魯棒的神經(jīng)網(wǎng)絡(luò)計(jì)算、數(shù)值計(jì)算等,具有頗大的價(jià)值。

技術(shù)特征:

1.一種緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其中將對(duì)憶阻器進(jìn)行讀操作所得電導(dǎo)值、目標(biāo)電導(dǎo)值、可容許編程電導(dǎo)誤差分別記為gread、gt和ge,將讀操作所得電導(dǎo)值與目標(biāo)電導(dǎo)值的差距記為δg,即δg=gread-gt,總循環(huán)數(shù)記為n,電導(dǎo)鞏固循環(huán)數(shù)記為m,set或reset寫入脈沖連續(xù)施加的次數(shù)記為i,具體步驟包括如下:

2.如權(quán)利要求1所述的緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其特征在于,所述施加reset脈沖序列具體為,施加reset脈沖,i變?yōu)閕+1,隨后讀電導(dǎo);若此時(shí)仍滿足δg>ge且i≠imax,則增加reset脈沖幅值,并重復(fù)施加reset脈沖與進(jìn)行判斷;否則結(jié)束reset子流程,且n變?yōu)閚+1,重復(fù)步驟2)—3)。

3.如權(quán)利要求1所述的緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其特征在于,所述施加set脈沖序列具體為,施加set脈沖,i變?yōu)閕+1,隨后讀電導(dǎo);若此時(shí)仍滿足δg<-ge且i≠imax,則增加set脈沖幅值,并重復(fù)施加set脈沖與進(jìn)行判斷;否則結(jié)束set子流程,且n變?yōu)閚+1,重復(fù)步驟2)—3)。

4.如權(quán)利要求1所述的緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其特征在于,所述憶阻器包括從上而下疊加的頂電極層、阻變層和底電極層,其中阻變層的材料為ta2o5、hfo2金屬氧化物。

5.如權(quán)利要求4所述的緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其特征在于,所述憶阻器中在阻變層上設(shè)置功能層,所述功能層的材料為taox、tiox、alox、siox、hfox金屬氧化物。

6.如權(quán)利要求4所述的緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,其特征在于,所述憶阻器中頂電極與底電極的材料為tin、tan、ta、ti、w、al、cu、ag、pt、ir金屬。

技術(shù)總結(jié)

本發(fā)明提出了一種緩解非易失性憶阻器電導(dǎo)弛豫效應(yīng)的編程方法,屬于阻變存儲(chǔ)器技術(shù)領(lǐng)域。本發(fā)明通過(guò)給憶阻器施加正反向亞閾值電導(dǎo)鞏固脈沖使所寫入的電導(dǎo)狀態(tài)變得穩(wěn)定,從而有效地抑制了電導(dǎo)隨時(shí)間的弛豫效應(yīng),使所寫入的信息更準(zhǔn)確。同時(shí),相比于已被報(bào)道的編程方法,大大降低了編程過(guò)程復(fù)雜度和時(shí)間成本,也不需要引入額外的硬件支持,對(duì)雙向弛豫效應(yīng)也能達(dá)到很好的抑制效果,有利于實(shí)現(xiàn)需要準(zhǔn)確存儲(chǔ)信息的應(yīng)用場(chǎng)景,包括科學(xué)數(shù)值計(jì)算、高效類腦計(jì)算等,具有頗高的應(yīng)用發(fā)展前景。

技術(shù)研發(fā)人員:楊玉超,張柏駿,余連風(fēng),張騰,袁銳,黃如

受保護(hù)的技術(shù)使用者:北京大學(xué)

技術(shù)研發(fā)日:

技術(shù)公布日:2025/4/24

- 還沒(méi)有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!