一種芯片結(jié)構(gòu)及芯片封裝方法與流程

本發(fā)明涉及集成電路,尤其涉及一種芯片結(jié)構(gòu)及芯片封裝方法。

背景技術(shù):

1、近年來(lái),半導(dǎo)體芯片市場(chǎng)競(jìng)爭(zhēng)進(jìn)入白熱化,芯片市場(chǎng)已經(jīng)逐漸轉(zhuǎn)向以產(chǎn)品質(zhì)量與價(jià)格競(jìng)爭(zhēng)并存的態(tài)勢(shì)。芯片的最終應(yīng)用形態(tài)是封裝形式,晶圓級(jí)芯片封裝作為先進(jìn)封裝的代表,與傳統(tǒng)封裝相比,具有體積小,成本低、電氣互聯(lián)路徑短等優(yōu)勢(shì),得到了廣泛應(yīng)用。

2、晶圓級(jí)芯片尺寸封裝是在整片晶圓生產(chǎn)完成后,直接在晶圓上進(jìn)行封裝,之后才切割制成單顆芯片,封裝尺寸幾乎等同于原芯片大小。焊球作為芯片與外部電路進(jìn)行電氣連接的接觸端子,將芯片焊接在pcb印刷電路板上。晶圓級(jí)芯片封裝典型封裝形式,是在芯片正面電路層進(jìn)行封裝植球,將焊球與外界電路如pcb電路板的焊盤(pán)接觸,這時(shí),封裝的重布線層的射頻布線由于接觸芯片電路層距離過(guò)近,會(huì)與芯片發(fā)生電磁強(qiáng)耦合效應(yīng),對(duì)正常信號(hào)造成干擾,甚至產(chǎn)生雜散或者自激。為了避免耦合,常規(guī)做法是,將射頻布線進(jìn)行繞行,盡量減少封裝射頻線與芯片電路布線的重合,但是這樣不僅線路設(shè)計(jì)復(fù)雜繁瑣、布線層數(shù)增加,而且增大了傳輸損耗,使封裝后的性能大打折扣。

3、可以看出,雖然目前針對(duì)上述問(wèn)題有一些常見(jiàn)的解決手段,但這些解決手段是在芯片完成后,在封裝過(guò)程中再進(jìn)行規(guī)避補(bǔ)救,拉長(zhǎng)了設(shè)計(jì)周期,存在改善效果差或設(shè)計(jì)成本高的問(wèn)題,避免電磁耦合的效果不佳。

技術(shù)實(shí)現(xiàn)思路

1、本發(fā)明實(shí)施例提供了一種芯片結(jié)構(gòu)及芯片封裝方法,以解決芯片與外界電路封裝連接時(shí)的電磁耦合,使得微波性能效果不佳的問(wèn)題。

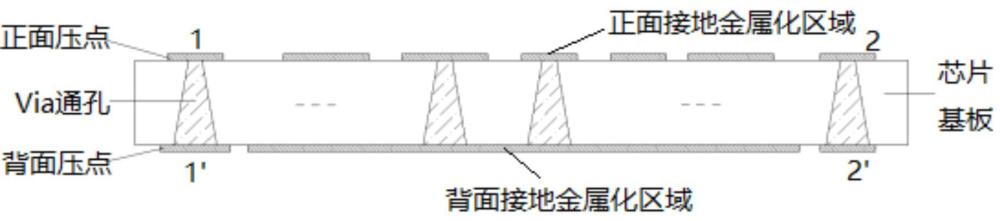

2、第一方面,本發(fā)明實(shí)施例提供了一種芯片結(jié)構(gòu),包括:

3、芯片基板;

4、芯片基板的正面設(shè)有正面金屬化層,正面金屬化層包括正面壓點(diǎn)和正面接地金屬化區(qū)域;

5、芯片基板的背面設(shè)有背面金屬化層,背面金屬化層包括背面壓點(diǎn)和背面接地金屬化區(qū)域,正面壓點(diǎn)與背面壓點(diǎn)一一對(duì)應(yīng)設(shè)置,背面接地金屬化區(qū)域與正面接地金屬化區(qū)域?qū)?yīng)設(shè)置;

6、芯片基板內(nèi)設(shè)有若干via通孔互連結(jié)構(gòu),正面壓點(diǎn)與相對(duì)應(yīng)的背面壓點(diǎn)通過(guò)via通孔互連結(jié)構(gòu)連接,正面接地金屬化區(qū)域與背面接地金屬化區(qū)域通過(guò)via通孔互連結(jié)構(gòu)連接,背面壓點(diǎn)作為與外部電路進(jìn)行信號(hào)傳輸?shù)慕佑|端子。

7、在一種可能的實(shí)現(xiàn)方式中,背面壓點(diǎn)對(duì)應(yīng)設(shè)于相對(duì)應(yīng)的正面壓點(diǎn)的正下方。

8、在一種可能的實(shí)現(xiàn)方式中,正面金屬化層還包括管芯、電容、電阻和微帶線。

9、在一種可能的實(shí)現(xiàn)方式中,正面壓點(diǎn)包括射頻輸入壓點(diǎn)、射頻輸出壓點(diǎn)、柵極電極壓點(diǎn)和漏極電極壓點(diǎn)。

10、第二方面,本發(fā)明實(shí)施例提供了一種芯片封裝方法,基于上述的芯片結(jié)構(gòu)制成的芯片實(shí)現(xiàn),包括:

11、在芯片正面電路表面形成空腔結(jié)構(gòu),并將空腔固定在芯片有源區(qū)正上方;

12、利用復(fù)合材料將整個(gè)芯片正面以及側(cè)面外圍包裹,形成第一塑封層,包裹部位涵蓋正面接地金屬化區(qū)域、空腔結(jié)構(gòu);

13、在背面壓點(diǎn)和背面接地金屬化區(qū)域設(shè)置若干第一銅柱,在芯片的背面的底部和第一塑封層的底部設(shè)置第二塑封層,將第一銅柱包裹;其中,第二塑封層與第一銅柱的底部平齊;

14、在第二塑封層的底部設(shè)置第二介質(zhì)層,在第二介質(zhì)層中設(shè)置若干第二銅柱,并使第二銅柱與第一銅柱一一對(duì)應(yīng)連接;

15、在第二介質(zhì)層的底部設(shè)置重布線層;其中,重布線層的布線與第二銅柱對(duì)應(yīng)連接;

16、在第二介質(zhì)層和重布線層的底部設(shè)置第三介質(zhì)層,在第三介質(zhì)層中設(shè)置若干第三銅柱,并使重布線層的布線與第三銅柱對(duì)應(yīng)連接;

17、第三銅柱的底部設(shè)置若干金屬化接觸焊盤(pán),在金屬化接觸焊盤(pán)的底部設(shè)置焊球。

18、在一種可能的實(shí)現(xiàn)方式中,空腔結(jié)構(gòu)通過(guò)第一介質(zhì)層構(gòu)建;

19、第一介質(zhì)層、第二介質(zhì)層和第三介質(zhì)層均為pi介質(zhì);

20、第一塑封層和第二塑封層均為環(huán)氧樹(shù)脂。

21、在一種可能的實(shí)現(xiàn)方式中,第一銅柱通過(guò)電鍍形成;

22、在第二介質(zhì)層中設(shè)置若干第二銅柱,包括:

23、在第二介質(zhì)層對(duì)應(yīng)第一銅柱的位置進(jìn)行顯影曝光,露出第一銅柱;

24、在第一銅柱的底部進(jìn)行離子濺射和金屬化填充,得到第二銅柱;

25、在第三介質(zhì)層中設(shè)置若干第三銅柱,包括:

26、在第三介質(zhì)層對(duì)應(yīng)重布線層的布線末端的位置進(jìn)行曝光顯影,露出重布線層的布線末端;

27、在重布線層的布線末端進(jìn)行離子濺射和金屬化填充,得到第三銅柱。

28、在一種可能的實(shí)現(xiàn)方式中,在第二介質(zhì)層的底部設(shè)置重布線層,包括:

29、在第二介質(zhì)層的表面進(jìn)行離子濺射,設(shè)置重布線層,在重布線層進(jìn)行布線。

30、在一種可能的實(shí)現(xiàn)方式中,第三銅柱的底部與第三介質(zhì)層平齊。

31、在一種可能的實(shí)現(xiàn)方式中,焊球包括錫球。

32、本發(fā)明實(shí)施例提供一種芯片結(jié)構(gòu)及芯片封裝方法,將芯片的正面壓點(diǎn)通過(guò)via通孔互連結(jié)構(gòu)與背面壓點(diǎn)一一對(duì)應(yīng)連接,正面接地金屬化區(qū)域通過(guò)via通孔互連結(jié)構(gòu)背面接地金屬化區(qū)域?qū)?yīng)連接,從而將正面壓點(diǎn)和正面接地金屬化區(qū)域引出至背面,其中將背面壓點(diǎn)作為與外部電路進(jìn)行信號(hào)傳輸?shù)慕佑|端子,與外界電路的封裝連接,以此增加封裝射頻線路與芯片正面的電路拓?fù)浣Y(jié)構(gòu)的距離,保證封裝射頻線路與芯片正面的電路拓?fù)浣Y(jié)構(gòu)有一定的距離,防止重布線層的線路干擾有用信號(hào),避免電磁耦合,保證微波信號(hào)的傳輸特性。

技術(shù)特征:

1.一種芯片結(jié)構(gòu),其特征在于,包括:

2.根據(jù)權(quán)利要求1所述的芯片結(jié)構(gòu),其特征在于,所述背面壓點(diǎn)對(duì)應(yīng)設(shè)于相對(duì)應(yīng)的所述正面壓點(diǎn)的正下方。

3.根據(jù)權(quán)利要求1所述的芯片結(jié)構(gòu),其特征在于,所述正面金屬化層還包括管芯、電容、電阻和微帶線。

4.根據(jù)權(quán)利要求1所述的芯片結(jié)構(gòu),其特征在于,所述正面壓點(diǎn)包括射頻輸入壓點(diǎn)、射頻輸出壓點(diǎn)、柵極電極壓點(diǎn)和漏極電極壓點(diǎn)。

5.一種芯片封裝方法,其特征在于,基于權(quán)利要求1-4任一項(xiàng)所述的芯片結(jié)構(gòu)制成的芯片實(shí)現(xiàn),包括:

6.根據(jù)權(quán)利要求5所述的芯片封裝方法,其特征在于,所述空腔結(jié)構(gòu)通過(guò)第一介質(zhì)層構(gòu)建;

7.根據(jù)權(quán)利要求5所述的芯片封裝方法,其特征在于,所述第一銅柱通過(guò)電鍍形成;

8.根據(jù)權(quán)利要求5所述的芯片封裝方法,其特征在于,所述在所述第二介質(zhì)層的底部設(shè)置重布線層,包括:

9.根據(jù)權(quán)利要求5所述的芯片封裝方法,其特征在于,所述第三銅柱的底部與所述第三介質(zhì)層平齊。

10.根據(jù)權(quán)利要求5所述的芯片封裝方法,其特征在于,所述焊球包括錫球。

技術(shù)總結(jié)

本發(fā)明提供一種芯片結(jié)構(gòu)及芯片封裝方法。該芯片結(jié)構(gòu)包括:芯片基板;芯片基板的正面設(shè)有正面金屬化層,正面金屬化層包括正面壓點(diǎn)和正面接地金屬化區(qū)域;芯片基板的背面設(shè)有背面金屬化層,背面金屬化層包括背面壓點(diǎn)和背面接地金屬化區(qū)域,正面壓點(diǎn)與背面壓點(diǎn)對(duì)應(yīng)設(shè)置,背面接地金屬化區(qū)域與正面接地金屬化區(qū)域?qū)?yīng)設(shè)置;芯片基板內(nèi)設(shè)有若干Via通孔互連結(jié)構(gòu),正面壓點(diǎn)與相對(duì)應(yīng)的背面壓點(diǎn)通過(guò)Via通孔互連結(jié)構(gòu)連接,正面接地金屬化區(qū)域與背面接地金屬化區(qū)域通過(guò)Via通孔互連結(jié)構(gòu)連接,背面壓點(diǎn)作為與外部電路進(jìn)行信號(hào)傳輸?shù)慕佑|端子。本發(fā)明能夠在芯片制作階段,將芯片正面的壓點(diǎn)引出至背面,避免后期與外界電路封裝連接時(shí)的電磁耦合產(chǎn)生。

技術(shù)研發(fā)人員:杜鵬搏,曲韓賓,崔朝探,張長(zhǎng)城,蘆雪,焦雪龍,崔寶峰

受保護(hù)的技術(shù)使用者:河北新華北集成電路有限公司

技術(shù)研發(fā)日:

技術(shù)公布日:2025/4/28

- 還沒(méi)有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!