半導體元件及其制作方法與流程

本發明涉及半導體裝置的領域,特別是涉及一種具有特定傾斜角度表面的外延層的半導體元件及其制作方法。

背景技術:

1、隨著半導體制作工藝的線寬不斷縮小,半導體制作工藝也浮現更多挑戰與瓶頸。以外延層上形成有蓋層的金屬氧化物半導體導體(metal?oxide?semiconductor,mos)晶體管為例,當蓋層的厚度較厚,相鄰元件之間易發生短路,而當蓋層的厚度較薄,在清洗過程中外延層的外壁可能一并被移除而形成孔洞,導致后續進行自對準金屬硅化物制作工藝(self-aligned?silicide?process)時,金屬硅化物容易沿著外延層的孔洞流動,而使金屬硅化物形成預定的位置之外。

2、因此,如何改良半導體元件的結構及制作方法,一方面可降低元件之間發生短路的機率,另一方面可降低金屬硅化物發生非預期流動的機率,遂為相關業者的重要課題。

技術實現思路

1、本發明的一目的在于提供一種半導體元件及其制作方法,以解決上述問題。

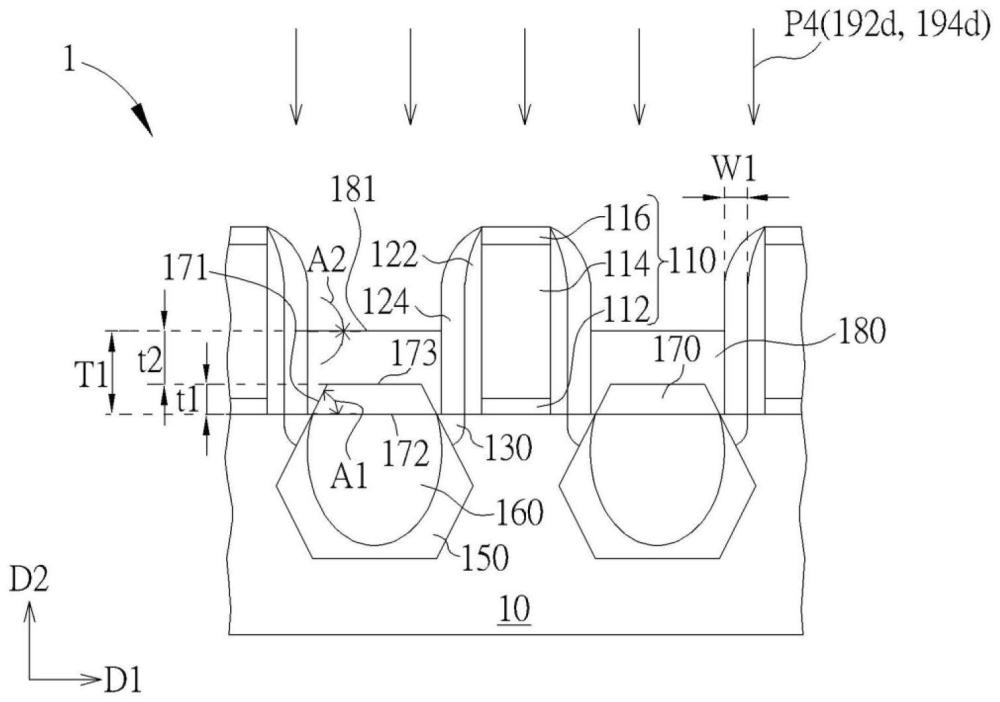

2、依據本發明一實施方式是提供一種半導體元件,包含一柵極結構、一第一外延層、一第二外延層以及一蓋層。柵極結構設置于一基底上。第一外延層設置于柵極結構二側的基底中。第二外延層設置于第一外延層上,其中第二外延層的一表面與一水平方向之間的夾角為15度至35度。蓋層設置于第二外延層上。

3、依據本發明另一實施方式是提供一種半導體元件的制作方法,包含以下步驟。形成一柵極結構于一基底上。形成二凹槽于柵極結構二側的基底中。形成一第一外延層于二凹槽中。形成一第二外延層于第一外延層上,其中第二外延層的一表面與一水平方向之間的夾角為15度至35度。形成一蓋層于第二外延層上。

4、相較于現有技術,本發明通過第二外延層的表面與水平方向之間的夾角落在特定范圍,有利于在不增加蓋層厚度的情況下,降低第二外延層的側壁在清洗過程中形成孔洞的機率,而有利于降低蓋層過厚所導致元件之間發生短路的機率,且可降低金屬硅化物發生非預期流動的機率。

技術特征:

1.一種半導體元件,包含:

2.如權利要求1所述的半導體元件,其中該蓋層的表面與該水平方向之間的夾角為0度至5度。

3.如權利要求2所述的半導體元件,其中該蓋層的材料包含硅,且該蓋層的該表面的晶面為(100)。

4.如權利要求1所述的半導體元件,其中該第二外延層于垂直于該水平方向的厚度為30埃至150埃。

5.如權利要求1所述的半導體元件,其中該蓋層于垂直于該水平方向的厚度為100埃至200埃。

6.如權利要求1所述的半導體元件,其中該第二外延層與該蓋層于垂直于該水平方向的厚度總和為130埃至350埃。

7.如權利要求1所述的半導體元件,還包含:

8.如權利要求7所述的半導體元件,其中該第二外延層與該蓋層于垂直于該水平方向的厚度總和與該間隙壁的側壁于該水平方向的厚度的比值為1至2。

9.如權利要求7所述的半導體元件,其中該間隙壁的側壁于該水平方向的厚度為150埃至200埃。

10.如權利要求1所述的半導體元件,其中該第二外延層的材料包含硅鍺,且該第二外延層的該表面的晶面為(311)。

11.一種制作半導體元件的方法,包含:

12.如權利要求11所述的方法,其中該蓋層的表面與該水平方向之間的夾角為0度至5度。

13.如權利要求11所述的方法,其中形成該第二外延層及形成該蓋層包含通入蝕刻氣體以及沉積材料氣體,形成該第二外延層時該蝕刻氣體與該沉積材料氣體的摩爾數比大于形成該蓋層時該蝕刻氣體與該沉積材料氣體的摩爾數比。

14.如權利要求13所述的方法,其中形成該第二外延層時該蝕刻氣體與該沉積材料氣體的摩爾數比為1至2。

15.如權利要求13所述的方法,其中形成該蓋層時該蝕刻氣體與該沉積材料氣體的摩爾數比為0.45至0.55。

16.如權利要求11所述的方法,其中該第二外延層于垂直于該水平方向的厚度為30埃至150埃。

17.如權利要求11所述的方法,其中該蓋層于垂直于該水平方向的厚度為100埃至200埃。

18.如權利要求11所述的方法,還包含:

19.如權利要求18所述的方法,其中該第二外延層與該蓋層于垂直于該水平方向的厚度總和與該間隙壁的側壁于該水平方向的厚度的比值為1至2。

20.如權利要求18所述的方法,其中該間隙壁的側壁于該水平方向的厚度為150埃至200埃。

技術總結

本發明公開一種半導體元件及其制作方法,其中該半導體元件包含一柵極結構、一第一外延層、一第二外延層以及一蓋層。柵極結構設置于一基底上。第一外延層設置于柵極結構二側的基底中。第二外延層設置于第一外延層上,其中第二外延層的一表面與一水平方向之間的夾角為15度至35度。蓋層設置于第二外延層上。

技術研發人員:謝勇,黃世賢,劉昇旭,高強,談文毅

受保護的技術使用者:聯芯集成電路制造(廈門)有限公司

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!