電平位移芯片及其電路的制作方法

本發明涉及芯片,具體涉及一種電平位移芯片及其電路。

背景技術:

1、電平位移芯片電路的主要功能是實現不同電壓域之間的電平轉換,在電子系統中,不同的模塊或芯片需要工作在不同的電壓下,因此需要進行電平轉換以確保信號的正確傳輸。

2、如圖1所示,現有技術中的電平位移芯片電路主要包括四個場效應管,分別為m1、m2、m3和m4,其中m1和m2的源極用于連接工作電壓,m3的柵極用于連接第一輸入端in,m4的柵極用于連接第二輸入端inb,m1和m3的。

3、假設剛開始電路中的a連接點為高電平,b連接點為低電平,那么m1導通,m2關斷,當輸入信號從低到高時,m3導通,m1關斷,此時電路的左側支路會導通,左側支路的電流由m3和m1之間的競爭關系決定,如果m3能將電流下拉,讓a連接點的電壓降低至低于vddh-vthp,此時m2導通,當b連接點的電位逐漸上升至超過vddh-vthp后,m1關斷,隨后a連接點的電位將會連續下降直到達到gnd,b連接點的電位最終也達到電源電壓,這就完成了電平轉換,另一側同理。

4、a連接點的下降延遲由以下三階段組成:初始狀態,a連接點的電壓為電源電壓,b連接點的電壓為地,m1導通,m2關斷,隨著輸入信號的升高,m3從關閉狀態變為開啟狀態,而m4則從開啟狀態變為關閉狀態。

5、第一階段,b連接點的電平不變,a連接點存在寄生電容并開始向外放電,即a連接點的電壓從vddh減少到vddh-vthp,這個過程段的持續時間如下:

6、

7、其中,

8、

9、第二階段,a連接點的電壓減少到vddh-vthp以下,m2導通,b連接點的電壓上升至vddh-vthp,這個時間段內,當a連接點的電壓下降至va。此過程中,b連接點電壓為:

10、

11、b連接點的充電電流icharge2(t)滿足以下兩個式子,分別為線性區和飽和區電流表達式:

12、

13、

14、a連接點的電壓如下:

15、

16、流過m1的電流如下:

17、

18、因此,第二階段的下降延遲時間滿足以下式子:

19、

20、第三階段,b連接點的電壓上升至vddh,m1關斷,a連接點的電壓由va繼續下降至地電平,在這個過程中,持續時間如下:

21、

22、總的下降延遲時間為上面三個時間相加,即tf=tf1+tf2+tf3。

23、a連接點的電壓上升延遲時間由兩部分組成,即當輸入由高變低時,第一階段m3關斷,m4導通,此時的m1還處于關斷狀態,m2還處于導通狀態;b連接點的寄生電容放電,放電的電流如下:

24、idischage2=i4-i2;

25、此時,a處的電壓還能保持不變。此過程的延遲時間為:

26、

27、其中,

28、

29、第二階段,b連接點的電壓下降到vddh-vthp以下時,m1導通,開始給a連接點的寄生電容充電,其充電電流大小如下:

30、idischarge2=i1;

31、此過程延遲時間為:

32、

33、其中,

34、

35、因此,總的上升延時為tr=tr1+tr2。

36、綜上所述可知,現有技術中的電平位移芯片電路不僅動態功率耗損較高,且電平轉換速率較低,已無法滿足電平位移芯片的需求。

技術實現思路

1、本發明提供了一種新的電平位移芯片及其電路,旨在解決現有技術中的電平位移芯片電路不僅動態功率耗損較高,且電平轉換速率較低的問題。

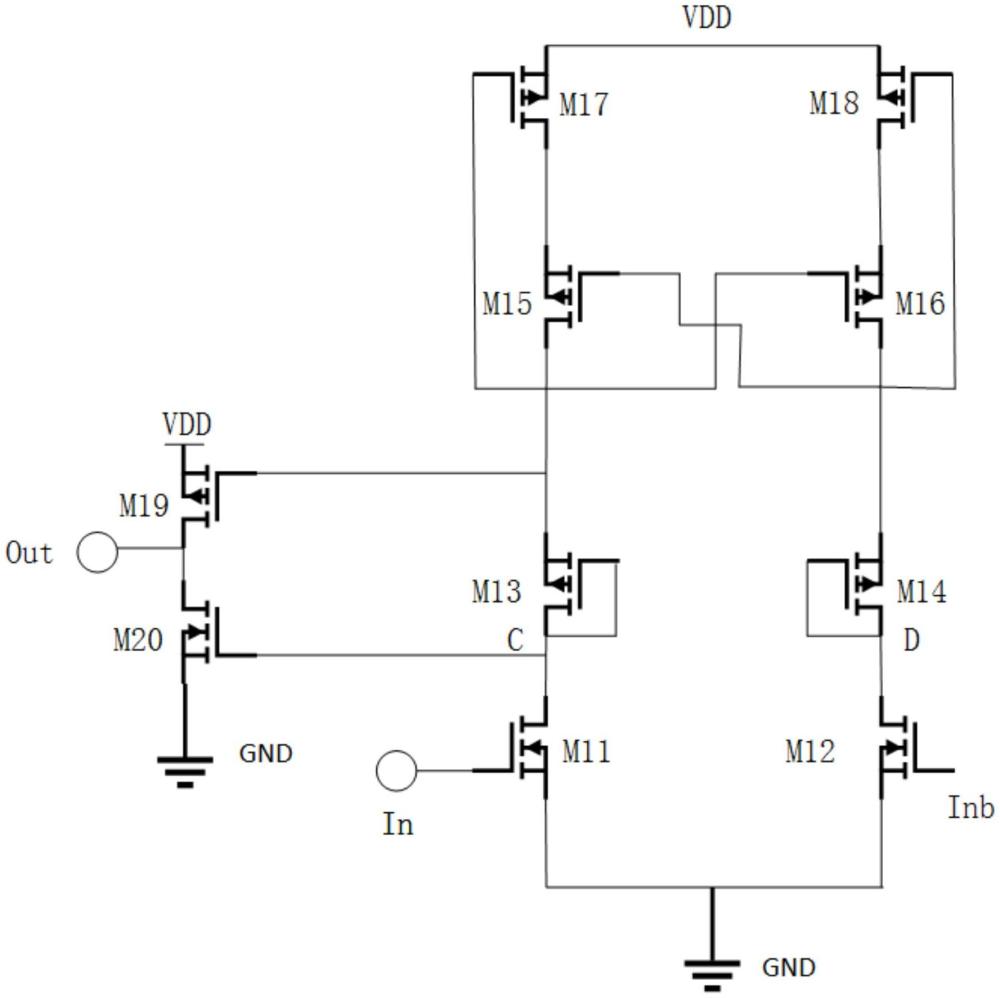

2、本發明提供了一種電平位移芯片電路,其包括第一場效應管、第二場效應管、第三場效應管、第四場效應管、第五場效應管、第六場效應管、第八場效應管、第九場效應管以及第十場效應管;

3、所述第一場效應管的柵極用于連接第一信號輸入端,所述第一場效應管的源極接地;

4、所述第二場效應管的柵極用于連接第二信號輸入端,所述第二場效應管的源極接地;

5、所述第三場效應管的柵極連接至所述第三場效應管的漏極,所述第三場效應管的漏極連接至所述第一場效應管的漏極;

6、所述第四場效應管的柵極連接至所述第四場效應管的漏極,所述第四場效應管的漏極連接至所述第二場效應管的漏極;

7、所述第五場效應管的漏極連接至所述第三場效應管的源極;

8、所述第六場效應管的漏極連接至所述第四場效應管的源極;

9、所述第七場效應管的柵極連接至所述第六場效應管的柵極,所述第七場效應管的漏極連接至所述第五場效應管的源極;

10、所述第八場效應管的柵極連接至所述第五場效應管的柵極,所述第八場效應管的漏極連接至所述第六場效應管的源極,所述第八場效應管的源極與所述第七場效應管的源極相連后用于連接工作電壓;

11、所述第九場效應管的柵極連接至所述第三場效應管的源極,所述第九場效應管的源極用于連接工作電壓;

12、所述第十場效應管的柵極連接至所述第一場效應管的源極,所述第十場效應管的源極接地,所述第十場效應管的漏極與所述第九場效應管的漏極相連并共同作為所述電平位移電路的輸出端。

13、優選的,所述第一場效應管、所述第二場效應管以及所述第十場效應管均為p型場效應管;所述第三場效應管、所述第四場效應管、所述第五場效應管、所述第六場效應管、所述第七場效應管以及所述第八場效應管均為n型場效應管。

14、優選的,所述第九場效應管和所述第十場效應管的尺寸相異。

15、本發明還提供了一種電平位移芯片,其包括如上所述的電平位移芯片電路。

16、與現有技術相比,本發明中的電平位移芯片電路通過增設第五場效應管、第六場效應管、第七場效應管、第八場效應管、第九場效應管以及第十場效應管,并限定第五場效應管、第六場效應管、第七場效應管以及第八場效應管的連接方式以使其作為交叉耦合調節模塊,這樣引入的部分通過調節上拉網絡的強度,便能減少關節內部節點的充放電時間,從而降低電平位移芯片電路的動態功率耗損,并提升其電平轉換速率,使其滿足電平位移芯片的需求。

技術特征:

1.一種電平位移芯片電路,其特征在于,所述電平位移芯片電路包括第一場效應管、第二場效應管、第三場效應管、第四場效應管、第五場效應管、第六場效應管、第八場效應管、第九場效應管以及第十場效應管;

2.如權利要求1所述的電平位移芯片電路,其特征在于,所述第一場效應管、所述第二場效應管以及所述第十場效應管均為p型場效應管;所述第三場效應管、所述第四場效應管、所述第五場效應管、所述第六場效應管、所述第七場效應管以及所述第八場效應管均為n型場效應管。

3.如權利要求1所述的電平位移芯片電路,其特征在于,所述第九場效應管和所述第十場效應管的尺寸相異。

4.一種電平位移芯片,其特征在于,所述電平位移芯片包括如權利要求1至3任意一項所述的電平位移芯片電路。

技術總結

本發明涉及芯片技術領域,提供了一種電平位移芯片及其電路,其中,所述電路包括第一場效應管、第二場效應管、第三場效應管、第四場效應管、第五場效應管、第六場效應管、第八場效應管、第九場效應管以及第十場效應管。本發明中的電平位移芯片電路不僅能降低其動態功率耗損,還能提升其電平轉換速率,以滿足電平位移芯片的需求。

技術研發人員:馮宇翔,鐘尊恒,區肇棟,尤家亮,單聯瑜,文健,謝穎熙,郭家杰

受保護的技術使用者:黑龍江匯芯半導體有限公司

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!