具有失調(diào)電壓自動校準(zhǔn)電路的高精度動態(tài)比較器的制作方法

本發(fā)明屬于電子電路設(shè)計,涉及一種具有失調(diào)電壓自動校準(zhǔn)電路的高精度動態(tài)比較器。

背景技術(shù):

1、動態(tài)高精度比較器是現(xiàn)代電子技術(shù)中的關(guān)鍵組件,尤其在adc(模擬數(shù)字轉(zhuǎn)換器)中扮演著至關(guān)重要的角色,動態(tài)比較器是一種比較電壓大小的一種電路,利用輸入信號不同時,使得輸出級電路放電速度不一樣,并且引入一個正反饋,使得放電速度進一步加快從而達(dá)到比較的效果,但是由于制造過程中存在的失配,不可避免的會出現(xiàn)比較器比較閾值出現(xiàn)偏差的問題,這在高精度比較器中是無法接受的,因此,如何實現(xiàn)高精度且具備失調(diào)電壓自校準(zhǔn)功能的動態(tài)比較器成為了待解決的技術(shù)問題。

技術(shù)實現(xiàn)思路

1、針對上述傳統(tǒng)技術(shù)中存在的問題,本發(fā)明提出了一種具有失調(diào)電壓自動校準(zhǔn)電路的高精度動態(tài)比較器,能夠?qū)崿F(xiàn)高精度且具備失調(diào)電壓自校準(zhǔn)功能的動態(tài)比較器。

2、為了實現(xiàn)上述目的,本發(fā)明實施例采用以下技術(shù)方案:

3、提供一種具有失調(diào)電壓自動校準(zhǔn)電路的高精度動態(tài)比較器,包括信號采樣電路、前置放大器和動態(tài)鎖存器,信號采樣電路基于柵壓自舉電路btsp并采用襯底電壓偏置技術(shù)設(shè)計,動態(tài)鎖存器包括鎖存器lat、失調(diào)電壓自動校準(zhǔn)電路acc和動態(tài)比較器;

4、信號采樣電路的采樣輸入端用于接入待采樣的輸入信號和參考信號,信號采樣電路的輸出端連接前置放大器的輸入端,前置放大器的輸出端連接動態(tài)比較器的輸入端,動態(tài)比較器的輸出端分別連接鎖存器lat的輸入端和失調(diào)電壓自動校準(zhǔn)電路acc的輸入端,失調(diào)電壓自動校準(zhǔn)電路acc的輸出端連接動態(tài)比較器的校準(zhǔn)輸入端;

5、信號采樣電路用于對輸入信號和參考信號進行采樣,前置放大器用于對信號采樣電路的采樣輸出進行前置放大,失調(diào)電壓自動校準(zhǔn)電路acc用于根據(jù)制造過程中的工藝誤差自適應(yīng)的減小動態(tài)比較器的失調(diào)電壓,動態(tài)比較器用于進行數(shù)據(jù)比較,鎖存器lat用于控制動態(tài)比較器的輸出信號是否隨輸入信號的變化而變化。

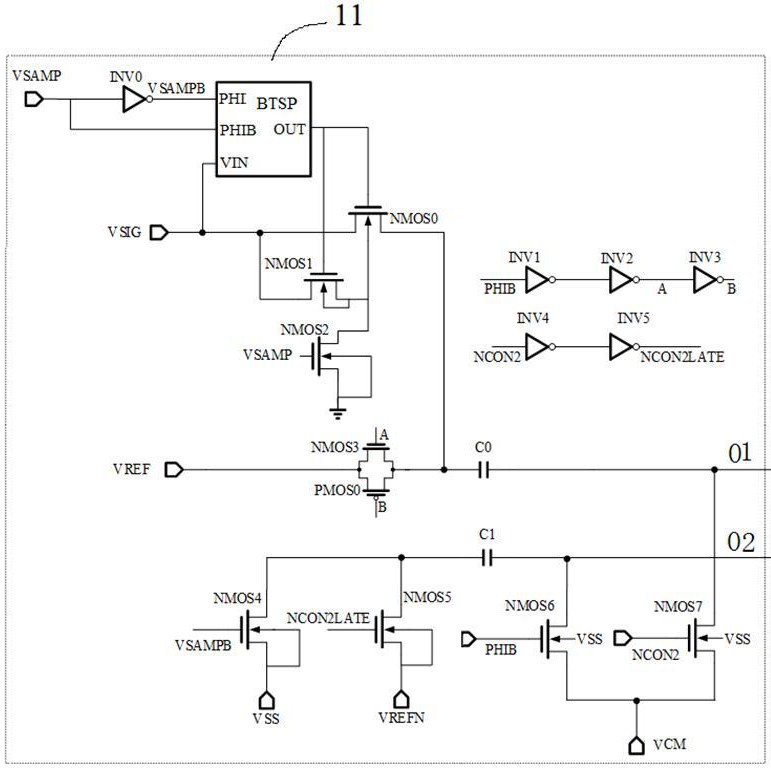

6、在其中一個實施例中,信號采樣電路包括反相器inv0、反相器inv1、反相器inv2、反相器inv3、反相器inv4、反相器inv5、柵壓自舉電路btsp、晶體管nmos0、晶體管nmos1、晶體管nmos2、晶體管nmos3、晶體管nmos4、晶體管nmos5、晶體管nmos6、晶體管nmos7、晶體管pmos0、電容c0和電容c1;

7、柵壓自舉電路btsp的phi端用于通過反相器inv0接入控制信號vsamp,柵壓自舉電路btsp的phib端用于接入控制信號vsamp,柵壓自舉電路btsp的vin端用于接入輸入信號vsig,柵壓自舉電路btsp的out端分別連接晶體管nmos0的柵極和晶體管nmos1的柵極;

8、晶體管nmos0的漏極和晶體管nmos1的漏極相連并用于接入輸入信號vsig,晶體管nmos0的襯底極分別連接晶體管nmos1的源極和晶體管nmos2的漏極,晶體管nmos0的源極連接電容c0的一端,晶體管nmos2的柵極用于接入控制信號vsamp,晶體管nmos2的源極接地,晶體管nmos3的漏極和晶體管pmos0的漏極相連并用于接入?yún)⒖夹盘杤ref,晶體管nmos3的源極和晶體管pmos0的源極相連并連接電容c0的一端,電容c0的另一端連接前置放大器的第一輸入端,反相器inv1、反相器inv2和反相器inv3依次串聯(lián),反相器inv1輸入端用于接入輸入信號phib,反相器inv3的輸出端連接晶體管pmos0的柵極,晶體管nmos3的柵極連接反相器inv2的輸出端;

9、反相器inv4和反相器inv5串聯(lián),反相器inv4的輸入端用于接入輸入信號ncon2,反相器inv5的輸出端連接晶體管nmos5的柵極,晶體管nmos4的漏極和晶體管nmos5的漏極均連接電容c1的一端,晶體管nmos6的漏極連接電容c1的另一端,電容c1的另一端連接前置放大器的第二輸入端,晶體管nmos4的柵極連接反相器inv0的輸出端,晶體管nmos4的源極用于接入信號vss,晶體管nmos5的源極用于接入?yún)⒖夹盘杤refn,晶體管nmos6的柵極用于接入輸入信號phib,晶體管nmos6的襯底極用于接入信號vss,晶體管nmos6的源極和晶體管nmos7的源極均用于接入信號vcm,晶體管nmos7的漏極連接電容c0的另一端,晶體管nmos7的襯底極用于接入信號vss,晶體管nmos7的柵極用于接入輸入信號ncon2。

10、在其中一個實施例中,前置放大器包括晶體管nmos8、晶體管nmos9、晶體管nmos10、晶體管nmos11和晶體管nmos12;

11、晶體管nmos8的柵極用于接入偏置電壓vbias,晶體管nmos8的源極接地,晶體管nmos8的漏極分別連接晶體管nmos9的源極和晶體管nmos10的源極,晶體管nmos9的襯底極連接晶體管nmos10的襯底極并用于接入信號vss,晶體管nmos9的柵極連接信號采樣電路的第一輸出端,晶體管nmos10的柵極連接信號采樣電路的第二輸出端,晶體管nmos9的漏極連接晶體管nmos11的漏極并連接至動態(tài)比較器的第一輸入端,晶體管nmos10的漏極連接晶體管nmos12的漏極并連接至動態(tài)比較器的第二輸入端,晶體管nmos11的源極和晶體管nmos12的源極相連并用于接入電源電壓vdd,晶體管nmos11的柵極和晶體管nmos12的柵極相連并用于接入電源電壓vdd。

12、在其中一個實施例中,動態(tài)鎖存器中的動態(tài)比較器包括反相器inv6、反相器inv7、或非門nor1、或非門nor2、晶體管nmos13、晶體管nmos14、晶體管nmos15、晶體管nmos16、晶體管nmos17、晶體管pmos1、晶體管pmos2、晶體管pmos3、晶體管pmos4、晶體管pmos5、晶體管pmos6、晶體管pmos7、晶體管pmos8、晶體管pmos9、晶體管pmos10、晶體管pmos11、晶體管pmos12、晶體管pmos13和晶體管pmos14;

13、晶體管nmos17的柵極用于接入時鐘信號clk,晶體管nmos17的源極接地,晶體管nmos17的漏極分別連接晶體管nmos13的源極和晶體管nmos14的源極,晶體管nmos13的柵極連接前置放大器的第二輸出端,晶體管nmos14的柵極連接前置放大器的第一輸出端,晶體管nmos13的襯底極和晶體管nmos14的襯底極均用于接入信號vss,晶體管nmos13的漏極連接晶體管nmos15的漏極,晶體管nmos14的漏極連接晶體管nmos16的漏極,晶體管nmos15的襯底極和晶體管nmos16的襯底極均用于接入信號vss;

14、晶體管nmos15的源極、晶體管pmos2的漏極、晶體管pmos1的漏極、晶體管pmos3的柵極和晶體管nmos16的柵極相連,晶體管nmos16的源極、晶體管pmos3的漏極、晶體管pmos4的漏極、晶體管pmos2的柵極和晶體管nmos15的柵極相連,晶體管pmos1的源極、晶體管pmos2的源極、晶體管pmos3的源極和晶體管pmos4的源極均用于接入電源電壓vdd,晶體管pmos1的柵極和晶體管pmos4的柵極均用于接入時鐘信號clk,反相器inv6的輸入端連接晶體管pmos2的漏極、反相器inv7輸入端連接晶體管pmos3的漏極,反相器inv6的輸出端連接或非門nor1的第一輸入端,反相器inv7的輸出端連接或非門nor2的第二輸入端,或非門nor1的輸出端連接或非門nor2的第一輸入端,或非門nor2的輸出端分別連接或非門nor1的第二輸入端、鎖存器lat的輸入端和失調(diào)電壓自動校準(zhǔn)電路acc的輸入端;

15、晶體管pmos5至晶體管pmos9的柵極相連并連接至晶體管nmos15的漏極,晶體管pmos10至晶體管pmos14的柵極相連并連接至晶體管nmos16的漏極,晶體管pmos5至晶體管pmos14的襯底極均用于接入電源電壓vdd,晶體管pmos5的源極和漏極相連,晶體管pmos6的源極和漏極相連,晶體管pmos7的源極和漏極相連,晶體管pmos9的源極和漏極相連,晶體管pmos5至晶體管pmos9的源極分別連接至失調(diào)電壓自動校準(zhǔn)電路acc的右輸出端,晶體管pmos10的源極和漏極相連,晶體管pmos11的源極和漏極相連,晶體管pmos12的源極和漏極相連,晶體管pmos13的源極和漏極相連,晶體管pmos14的源極和漏極相連,晶體管pmos10至晶體管pmos14的源極分別連接至失調(diào)電壓自動校準(zhǔn)電路acc的左輸出端。

16、在其中一個實施例中,失調(diào)電壓自動校準(zhǔn)電路acc包括incndec單元0至incndec單元9、d觸發(fā)器0至d觸發(fā)器9、左輸出門電路和右輸出門電路,incndec單元與d觸發(fā)器9一一對應(yīng);

17、各d觸發(fā)器的時鐘端均用于接入失調(diào)電壓校準(zhǔn)時鐘信號,各d觸發(fā)器的復(fù)位端均用于接入失調(diào)電壓自動校準(zhǔn)復(fù)位信號,每一d觸發(fā)器的d端連接相應(yīng)incndec單元的s端,每一d觸發(fā)器的q端連接相應(yīng)incndec單元的b端,incndec單元0至incndec單元4的dec端均連接至或非門nor2的輸出端,incndec單元0至incndec單元4之間依次通過cb端與cin端級聯(lián),incndec單元4的cb端懸空;

18、incndec單元5至incndec單元9的dec端均通過反相器inv12連接至或非門nor2的輸出端,incndec單元5至incndec單元9之間依次通過cb端與cin端級聯(lián),incndec單元9的cb端懸空;

19、左輸出門電路的輸出端連接incndec單元0的cin端,左輸出門電路的輸入端分別連接晶體管pmos10、晶體管pmos11、晶體管pmos12、晶體管pmos13和晶體管pmos14的源極,右輸出門電路的輸出端連接incndec單元5的cin端,右輸出門電路的輸入端分別連接晶體管pmos5、晶體管pmos6、晶體管pmos7、晶體管pmos8和晶體管pmos9的漏極。

20、在其中一個實施例中,右輸出門電路包括反相器inv8、反相器inv9、與非門nand1、與非門nand2、與非門nand3、與非門nand4、與非門nand5、與非門nand6、或非門nor3、或非門nor4、或非門nor5和或非門nor6,左輸出門電路包括反相器inv10、反相器inv11、與非門nand7、與非門nand8、與非門nand9、與非門nand10、與非門nand11、與非門nand12、或非門nor7、或非門nor8、或非門nor9和或非門nor10;

21、與非門nand1、與非門nand2、或非門nor3和或非門nor4的輸入端作為右輸出門電路的輸入端,或非門nor5的兩個輸入端分別連接與非門nand1的輸出端和與非門nand2的輸出端,或非門nor5的輸出端連接與非門nand4的第一輸入端,與非門nand3的兩個輸入端分別連接或非門nor3和或非門nor4的輸出端,與非門nand3的另一個輸入端連接d觸發(fā)器9的q反端,與非門nand3的輸出端分別連接或非門nor6的一個輸入端和與非門nand11的一個輸入端,或非門nor6的另一個輸入端連接至或非門nor2的輸出端,或非門nor6的輸出端連接反相器inv8的輸入端,與非門nand5的一個輸入端連接至或非門nor2的輸出端,與非門nand5的另一個輸入端連接與非門nand9的輸出端,與非門nand4的第二輸入端連接d觸發(fā)器9的q端,與非門nand4的第三輸入端連接至或非門nor2的輸出端,與非門nand6的三個輸入端分別連接與非門nand4、與非門nand5和反相器inv8的輸出端,與非門nand6的輸出端通過反相器inv9連接incndec單元5的cin端;

22、與非門nand7、與非門nand8、或非門nor7和或非門nor8的輸入端作為左輸出門電路的輸入端,或非門nor9的兩個輸入端分別連接與非門nand7的輸出端和與非門nand8的輸出端,或非門nor9的輸出端連接與非門nand10的第一輸入端,與非門nand9的兩個輸入端分別連接或非門nor7和或非門nor8的輸出端,與非門nand9的另一個輸入端連接d觸發(fā)器4的q反端,與非門nand9的輸出端分別連接或非門nor10的一個輸入端,或非門nor10的另一個輸入端連接至反相器inv12的輸出端,或非門nor10的輸出端連接反相器inv10的輸入端,與非門nand11的另一個輸入端連接至反相器inv12的輸出端,與非門nand10的第二輸入端連接d觸發(fā)器4的q端,與非門nand10的第三輸入端連接至反相器inv12的輸出端,與非門nand12的三個輸入端分別連接與非門nand10、與非門nand11和反相器inv10的輸出端,與非門nand12的輸出端通過反相器inv11連接incndec單元0的cin端。

23、在其中一個實施例中,incndec單元包括異或門xor0、異或門xor1、與非門nand13、反相器inv13,異或門xor0的第一輸入端用于作為dec端,異或門xor0的第二輸入端和異或門xor1的第二輸入端相連作為b端,異或門xor0的輸出端連接與非門nand13的第一輸入端,與非門nand13的第二輸入端和異或門xor1的第一輸入端相連作為cin端,與非門nand13的輸出端連接反相器inv13的輸入端,反相器inv13的輸出端作為cb端,異或門xor1的輸出端作為s端。

24、上述技術(shù)方案中的一個技術(shù)方案具有如下優(yōu)點和有益效果:

25、上述具有失調(diào)電壓自動校準(zhǔn)電路的高精度動態(tài)比較器,通過采用了開關(guān)電容前置放大器,使得應(yīng)用于flash(閃存)adc中的比較器時不會因為共模電壓的不同而導(dǎo)致dc參數(shù)不同,從而減小了不同比較器之間的失調(diào)電壓;并且采用了襯底電壓偏置技術(shù),使得采樣開關(guān)在導(dǎo)通時電阻更小,截止時電阻更大。采用了失調(diào)電壓自動校準(zhǔn)電路acc使得電路能夠根據(jù)制造過程中的工藝誤差自適應(yīng)的調(diào)節(jié)失調(diào)電壓。與傳統(tǒng)比較器相比,采用了開關(guān)電容比較器的設(shè)計形式,使得比較器輸入信號在共模電壓vcm附近,保證了每個比較器不會因為共模電壓不同而導(dǎo)致的dc參數(shù)不同引起的失調(diào)電壓誤差,并且采取了失調(diào)電壓自動校準(zhǔn)電路acc,使得比較器的失調(diào)電壓更加小。

- 還沒有人留言評論。精彩留言會獲得點贊!