一種半導體功率器件靜態測試漏電流抑制方法與流程

本發明涉及半導體功率器件靜態測試,特別涉及一種半導體功率器件靜態測試漏電流抑制方法。

背景技術:

1、半導體功率器件靜態測試漏電流抑制方法是一種進行半導體功率器件靜態測試的方法,半導體功率器件的漏電流通常指的是在沒有外加信號或在截止狀態下器件內部由于材料的不完美性,如晶體缺陷、雜質、界面態等而產生的非預期微小電流,漏電流的存在可能會導致功率器件產生額外的功耗,在功率器件的靜態測試中,漏電流的準確測量對于評估器件的絕緣性能至關重要,隨著科技的不斷發展,人們對于半導體功率器件靜態測試漏電流抑制方法的要求也越來越高。

2、現有的半導體功率器件靜態測試方法在使用時存在一定的弊端,盡管現有的漏電流測試方法能夠在一定程度上抑制漏電流,然而測試電路中的其他部分如連接線、測試夾具和輔助設備,產生的非目標漏電流可能會干擾測試結果導致測量誤差,因此,在進行半導體功率器件漏電流測試時,有效抑制被測功率器件之外的電路部分產生的漏電流是很有必要的,為此,我們提出一種半導體功率器件靜態測試漏電流抑制方法。

技術實現思路

1、解決的技術問題:針對現有技術的不足,本發明提供了一種半導體功率器件靜態測試漏電流抑制方法,利用三同軸接口的guard線,實現對連接線、測試夾具和輔助設備上漏電流的抑制,有效提高功率器件靜態測試中漏電流測試的精確度,增強了系統的可靠性,可以有效解決背景技術中的問題。

2、技術方案:為實現上述目的,本發明采取的技術方案為:一種半導體功率器件靜態測試漏電流抑制方法,包括以下操作步驟:

3、s1:配合三同軸接口進行pcb設計,在pcb設計階段,采用guard線技術進行優化設計,guard線把高壓線即hi線和sense?hi線全部圍起來,同時避免與低壓線即lo線和senselo線接觸,實現對輸入信號線的等電位環繞保護,同時實現抑制連接線、測試夾具和輔助設備的漏電流;

4、s2:儀表通過雙端三同軸接口和pcb相連,將儀表的三同軸接口與pcb板上的三同軸接口相連接,避免接觸不良引入額外的噪聲或誤差;

5、s3:將待測的mos管插入插座,將待測半導體功率器件mos管插入pcb板上的專用測試插座中,確保mos管與測試系統的電氣連接正確無誤,為接下來的漏電流測試做好準備;

6、s4:開始漏電流靜態測試,漏電流測試所需的實驗環境已經搭建完成,可以開始mos管的漏電流靜態測試;

7、s5:儀表的hi端輸出高電平、lo端輸出低電平是指儀表的hi端口、lo端口分別輸出設置的高電平和低電平,電壓從雙端口三同軸連接線傳送到pcb板的hi端和lo端,并通過專用測試插座加到待測半導體功率器件mos管的d端和s端;

8、s6:儀表顯示mos管的漏電流,由于pcb板上guard線的電平和hi端一致,實現抑制被測功率器件之外的電路部分產生的漏電流,使儀表測量出的漏電流就是mos管本身的漏電流;

9、s7:漏電流靜態測試結束,mos管漏電流靜態測試已完成,并通過該方法提升了漏電流測試的準確性。

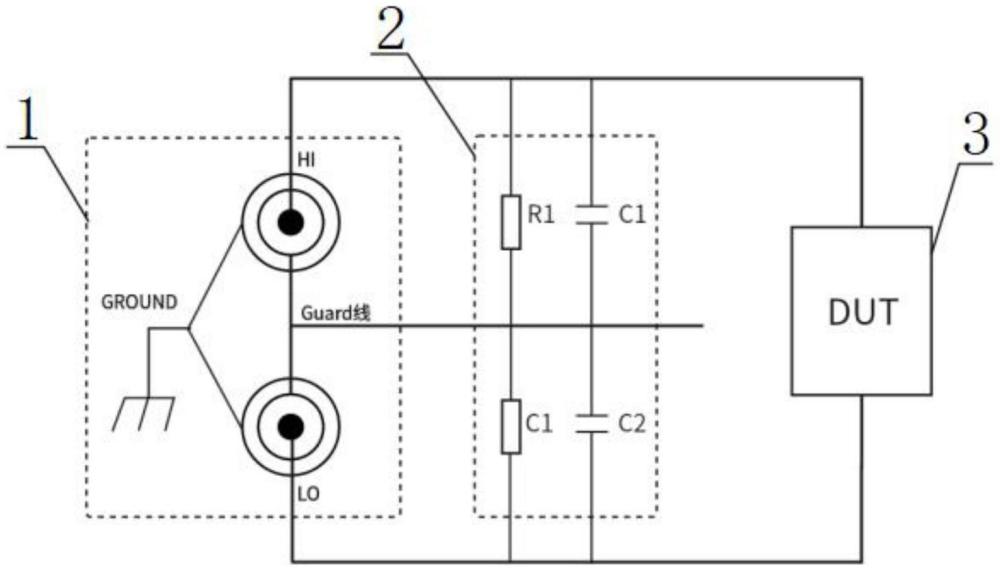

10、作為本申請一種優選的技術方案,三同軸接口、泄露電阻和泄露電容、被測半導體功率器件dut與pcb板,所述pcb板上設置hi線、sense?hi線、guard線、lo線與sense?lo線,所述三同軸接口用于給被測半導體功率器件dut提供高低電平,并測量被測半導體功率器件dut的漏電流,所述三同軸接口包括中心信號線、guard線和ground線。

11、作為本申請一種優選的技術方案,所述中心信號線處于三同軸接口的中心,目的是給被測半導體功率器件dut提供高低電平并測量被測半導體功率器件dut的漏電流,高電平通過三同軸接口中的hi線傳輸,低電平通過三同軸接口中的lo線傳輸,增強了信號的穩定性和抗干擾能力,提高漏電流測試的準確性。

12、作為本申請一種優選的技術方案,所述guard線在三同軸接口的中間層,分別環繞在中心信號線的hi線和lo線周圍,其中guard線的電位和hi線的電位相等,這種電位匹配確保了hi線上的電流不會通過guard線泄露,實現對輸入信號線的等電位環繞保護。

13、作為本申請一種優選的技術方案,所述ground線在三同軸接口的最外層,所述hi線最外層的ground線和lo線最外層的ground線被連接在一起,為所述三同軸接口中的中心信號線提供共同的參考電位,確保信號的準確性和穩定性。

14、作為本申請一種優選的技術方案,所述泄露電阻和泄露電容來自從hi線、guard線到lo線的漏電流測試回路中的連接線、測試夾具和輔助設備,包括hi線到guard線之間泄露電阻r和泄露電容c與lo線和guard線之間的泄露電阻r和泄露電容c。

15、作為本申請一種優選的技術方案,所述泄露電阻r和泄露電容c不存在泄漏電流,由于hi線電位與guard線的電位相等,所述hi線的電流則不會通過泄露電阻r和泄露電容c泄露到guard線。

16、作為本申請一種優選的技術方案,所述泄露電阻r和泄露電容c存在泄漏電流,由于所述guard線的電位與hi線的電位相等,所述guard線的泄露電流將通過泄露電阻r和泄露電容c流向lo線,并且不會通過被測半導體功率器件dut,所述guard線到lo線的泄露電流是由guard線電壓提供的,所述guard線電壓是hi線通過電壓跟隨器后得到,由于電壓跟隨器為高阻抗輸入,所述guard線的電流對hi線電流沒有影響,因此流過被測半導體功率器件dut的漏電流就是儀表在hi線輸出的電流。

17、有益效果:與現有技術相比,本發明提供了一種半導體功率器件靜態測試漏電流抑制方法,具備以下有益效果:該一種半導體功率器件靜態測試漏電流抑制方法,利用三同軸接口的guard線,實現對連接線、測試夾具和輔助設備上漏電流的抑制,有效提高功率器件靜態測試中漏電流測試的精確度,增強了系統的可靠性;本方法簡單易行,配合pcb設計就可以實現高精度的漏電流測試,降低了操作難度,減少了額外的設備投入和維護成本,提高了測試的經濟性;本方法不僅適用于半導體功率器件漏電流測試,還可以推廣到其他電子測試和測量領域,提高電子系統的性能和可靠性,整個半導體功率器件靜態測試漏電流抑制方法結構簡單,操作方便,使用的效果相對于傳統方式更好。

技術特征:

1.一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:包括以下操作步驟:

2.根據權利要求1所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:三同軸接口(1)、泄露電阻和泄露電容(2)、被測半導體功率器件dut(3)與pcb板,所述pcb板上設置hi線(4)、sense?hi線(5)、guard線(6)、lo線(7)與sense?lo線(8),所述三同軸接口(1)用于給被測半導體功率器件dut(3)提供高低電平,并測量被測半導體功率器件dut(3)的漏電流,所述三同軸接口(1)包括中心信號線、guard線(6)和ground線。

3.根據權利要求2所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:所述中心信號線處于三同軸接口(1)的中心,目的是給被測半導體功率器件dut(3)提供高低電平并測量被測半導體功率器件dut(3)的漏電流,高電平通過三同軸接口(1)中的hi線(4)傳輸,低電平通過三同軸接口(1)中的lo線(7)傳輸,增強了信號的穩定性和抗干擾能力,提高漏電流測試的準確性。

4.根據權利要求2所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:所述guard線(6)在三同軸接口(1)的中間層,分別環繞在中心信號線的hi線(4)和lo線(7)周圍,其中guard線(6)的電位和hi線(4)的電位相等,這種電位匹配確保了hi線(4)上的電流不會通過guard線(6)泄露,實現對輸入信號線的等電位環繞保護。

5.根據權利要求2所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:所述ground線在三同軸接口(1)的最外層,所述hi線(4)最外層的ground線和lo線(7)最外層的ground線被連接在一起,為所述三同軸接口(1)中的中心信號線提供共同的參考電位,確保信號的準確性和穩定性。

6.根據權利要求2所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:所述泄露電阻和泄露電容(2)來自從hi線(4)、guard線(6)到lo線(7)的漏電流測試回路中的連接線、測試夾具和輔助設備,包括hi線(4)到guard線(6)之間泄露電阻r1和泄露電容c1與lo線(7)和guard線(6)之間的泄露電阻r2和泄露電容c2。

7.根據權利要求6所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:所述泄露電阻r1和泄露電容c1不存在泄漏電流,由于hi線(4)電位與guard線(6)的電位相等,所述hi線(4)的電流則不會通過泄露電阻r1和泄露電容c1泄露到guard線(6)。

8.根據權利要求6所述的一種半導體功率器件靜態測試漏電流抑制方法,其特征在于:所述泄露電阻r2和泄露電容c2存在泄漏電流,由于所述guard線(6)的電位與hi線(4)的電位相等,所述guard線(6)的泄露電流將通過泄露電阻r2和泄露電容c2流向lo線(7),并且不會通過被測半導體功率器件dut,所述guard線(6)到lo線(7)的泄露電流是由guard線(6)電壓提供的,所述guard線(6)電壓是hi線(4)通過電壓跟隨器后得到,由于電壓跟隨器為高阻抗輸入,所述guard線(6)的電流對hi線(4)電流沒有影響,因此流過被測半導體功率器件dut的漏電流就是儀表在hi線(4)輸出的電流。

技術總結

本發明公開了一種半導體功率器件靜態測試漏電流抑制方法,包括以下操作步驟:配合三同軸接口進行PCB設計,在PCB設計階段,采用Guard線技術進行優化設計,Guard線把高壓線即Hi線和SENSE?Hi線全部圍起來,同時避免與低壓線即Lo線和SENSE?Lo線接觸,實現對輸入信號線的等電位環繞保護,同時實現抑制連接線、測試夾具和輔助設備的漏電流;儀表通過雙端三同軸接口和PCB相連,將儀表的三同軸接口與PCB板上的三同軸接口相連接。本發明所述的一種半導體功率器件靜態測試漏電流抑制方法,利用三同軸接口的Guard線,實現對連接線、測試夾具和輔助設備上漏電流的抑制,有效提高功率器件靜態測試中漏電流測試的精確度,增強了系統的可靠性。

技術研發人員:梁光勝,于躍,寧軍偉,陳冕

受保護的技術使用者:北京海瑞克科技發展有限公司

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!