晶體管布局方法、裝置、存儲介質(zhì)及電子設(shè)備與流程

本申請實施例涉及集成電路,具體涉及一種晶體管布局方法、裝置、存儲介質(zhì)及電子設(shè)備。

背景技術(shù):

1、在集成電路設(shè)計中,隨著器件密度的不斷提升,如何在有限的布局面積內(nèi)實現(xiàn)高性能、高效率的電路設(shè)計成為一項關(guān)鍵技術(shù)挑戰(zhàn)。標準單元作為集成電路的基本組成模塊,其布局優(yōu)化直接影響芯片的整體性能、功耗和制造成本。

2、晶體管折疊是一種用于優(yōu)化大尺寸晶體管布局的關(guān)鍵技術(shù)。大尺寸晶體管通常會占用較大的版圖面積,并增加布線的復(fù)雜性,從而對信號傳輸速度和功耗產(chǎn)生不利影響。通過將大尺寸晶體管拆分為若干個小尺寸晶體管可以減少單個晶體管的擴散區(qū)域、優(yōu)化布線結(jié)構(gòu)、提高布局的緊湊性和電路性能。

3、然而,晶體管折疊后的布局需要解決多個小晶體管的連接和排列問題,晶體管的布局復(fù)雜度較高。

技術(shù)實現(xiàn)思路

1、本申請實施例提供了一種晶體管布局方法、裝置、存儲介質(zhì)及電子設(shè)備,可以降低晶體管的布局復(fù)雜度。

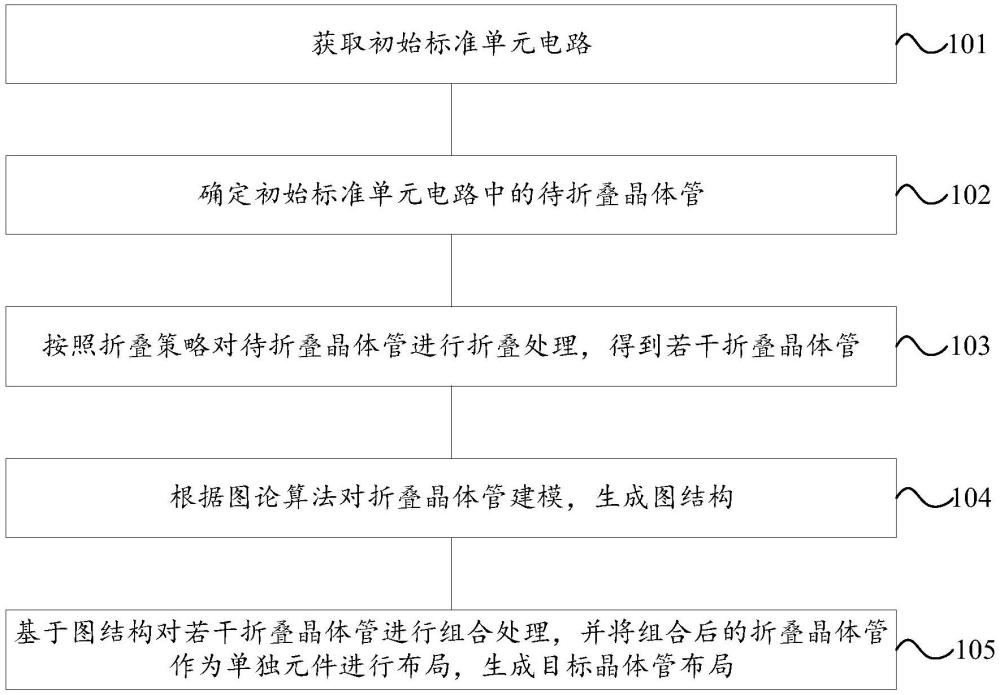

2、第一方面,本申請實施例提供了一種晶體管布局方法,包括:

3、獲取初始標準單元電路;

4、確定所述初始標準單元電路中的待折疊晶體管;

5、按照折疊策略對所述待折疊晶體管進行折疊處理,得到若干折疊晶體管;

6、根據(jù)圖論算法對所述折疊晶體管建模,生成圖結(jié)構(gòu);

7、基于所述圖結(jié)構(gòu)對若干所述折疊晶體管進行組合處理,并將組合后的所述折疊晶體管作為單獨元件進行布局,生成目標晶體管布局。

8、在本申請實施例提供的晶體管布局方法中,所述根據(jù)圖論算法對所述折疊晶體管建模,生成圖結(jié)構(gòu),包括:

9、根據(jù)晶體管類型對若干所述折疊晶體管進行分類,分為第一折疊晶體管和第二折疊晶體管;

10、基于圖論算法對所述第一折疊晶體管和所述第二折疊晶體管建模,得到圖結(jié)構(gòu),所述圖結(jié)構(gòu)包括第一子圖結(jié)構(gòu)和第二子圖結(jié)構(gòu)。

11、在本申請實施例提供的晶體管布局方法中,所述基于所述圖結(jié)構(gòu)對若干所述折疊晶體管進行組合處理,包括:

12、基于所述第一子圖結(jié)構(gòu)確定每個所述第一折疊晶體管中若干第一子晶體管的第一目標組合方式,并根據(jù)所述第一目標組合方式對每個所述第一折疊晶體管中若干第一子晶體管進行組合;

13、基于所述第二子圖結(jié)構(gòu)確定每個所述第二折疊晶體管中若干第二子晶體管的第二目標組合方式,并根據(jù)所述第二目標組合方式對每個所述第二折疊晶體管中若干第二子晶體管進行組合。

14、在本申請實施例提供的晶體管布局方法中,所述基于所述第一子圖結(jié)構(gòu)確定每個所述第一折疊晶體管中若干第一子晶體管的第一目標組合方式,包括:

15、確定所述第一子圖結(jié)構(gòu)中的奇數(shù)度點數(shù)量;

16、基于所述奇數(shù)度點數(shù)量和所述第一子圖結(jié)構(gòu)的連通性,對每個所述第一折疊晶體管中若干第一子晶體管的組合方式進行遍歷,確定第一目標組合方式。

17、在本申請實施例提供的晶體管布局方法中,所述基于所述第二子圖結(jié)構(gòu)確定每個所述第二折疊晶體管中若干第二子晶體管的第二目標組合方式,包括:

18、確定所述第二子圖結(jié)構(gòu)中的奇數(shù)度點數(shù)量;

19、基于所述奇數(shù)度點數(shù)量和所述第二子圖結(jié)構(gòu)的連通性,對每個所述第二折疊晶體管中若干第二子晶體管的組合方式進行遍歷,確定第二目標組合方式。

20、在本申請實施例提供的晶體管布局方法中,所述基于圖論算法分別對所述第一折疊晶體管和所述第二折疊晶體管建模,得到第一子圖結(jié)構(gòu)和第二子圖結(jié)構(gòu),包括:

21、將所述第一折疊晶體管中每個第一子晶體管的源極和漏極表示為節(jié)點,將每個所述第一子晶體管表示為連接節(jié)點的邊,形成第一子圖結(jié)構(gòu);

22、將所述第二折疊晶體管中每個第二子晶體管的源極和漏極表示為節(jié)點,將每個所述第二子晶體管表示為連接節(jié)點的邊,形成第二子圖結(jié)構(gòu)。

23、在本申請實施例提供的晶體管布局方法中,所述將組合后的所述折疊晶體管作為單獨元件進行布局,生成目標晶體管布局,包括:

24、基于所述第一折疊晶體管和所述第二折疊晶體管的對稱性,對所述第一折疊晶體管和/或所述第二折疊晶體的組合方式進行微調(diào),得到第一組合晶體管和第二組合晶體管;

25、將所述第一組合晶體管和所述第二組合晶體管作為單獨元件進行布局,生成目標晶體管布局。

26、第二方面,本申請實施例提供了一種晶體管布局裝置,包括:

27、獲取單元,用于獲取初始標準單元電路;

28、確定單元,用于確定所述初始標準單元電路中的待折疊晶體管;

29、折疊單元,用于按照折疊策略對所述待折疊晶體管進行折疊處理,得到若干折疊晶體管;

30、建模單元,用于根據(jù)圖論算法對所述折疊晶體管建模,生成圖結(jié)構(gòu);

31、組合單元,用于基于所述圖結(jié)構(gòu)對若干所述折疊晶體管進行組合處理,并將組合后的所述折疊晶體管作為單獨元件進行布局,生成目標晶體管布局。

32、第三方面,本申請?zhí)峁┝艘环N存儲介質(zhì),所述存儲介質(zhì)存儲有多條指令,所述指令適于處理器進行加載,以執(zhí)行上述任一項所述的晶體管布局方法。

33、第四方面,本申請?zhí)峁┝艘环N電子設(shè)備,包括存儲器,處理器及存儲在存儲器上并可在處理器上運行的計算機程序,其中,所述處理器執(zhí)行所述計算機程序時實現(xiàn)上述任一項所述的晶體管布局方法。

34、綜上所述,本申請實施例提供的晶體管布局方法包括獲取初始標準單元電路;確定所述初始標準單元電路中的待折疊晶體管;按照折疊策略對所述待折疊晶體管進行折疊處理,得到若干折疊晶體管;根據(jù)圖論算法對所述折疊晶體管建模,生成圖結(jié)構(gòu);基于所述圖結(jié)構(gòu)對若干所述折疊晶體管進行組合處理,并將組合后的所述折疊晶體管作為單獨元件進行布局,生成目標晶體管布局。本方案通過將晶體管折疊與圖論算法相結(jié)合,從而降低晶體管的布局復(fù)雜度。

技術(shù)特征:

1.一種晶體管布局方法,其特征在于,包括:

2.如權(quán)利要求1所述的晶體管布局方法,其特征在于,所述根據(jù)圖論算法對所述折疊晶體管建模,生成圖結(jié)構(gòu),包括:

3.如權(quán)利要求2所述的晶體管布局方法,其特征在于,所述基于所述圖結(jié)構(gòu)對若干所述折疊晶體管進行組合處理,包括:

4.如權(quán)利要求3所述的晶體管布局方法,其特征在于,所述基于所述第一子圖結(jié)構(gòu)確定每個所述第一折疊晶體管中若干第一子晶體管的第一目標組合方式,包括:

5.如權(quán)利要求3所述的晶體管布局方法,其特征在于,所述基于所述第二子圖結(jié)構(gòu)確定每個所述第二折疊晶體管中若干第二子晶體管的第二目標組合方式,包括:

6.如權(quán)利要求2所述的晶體管布局方法,其特征在于,所述基于圖論算法分別對所述第一折疊晶體管和所述第二折疊晶體管建模,得到第一子圖結(jié)構(gòu)和第二子圖結(jié)構(gòu),包括:

7.如權(quán)利要求2所述的晶體管布局方法,其特征在于,所述將組合后的所述折疊晶體管作為單獨元件進行布局,生成目標晶體管布局,包括:

8.一種晶體管布局裝置,其特征在于,包括:

9.一種存儲介質(zhì),其特征在于,所述存儲介質(zhì)存儲有多條指令,所述指令適于處理器進行加載,以執(zhí)行權(quán)利要求1-7任一項所述的晶體管布局方法。

10.一種電子設(shè)備,其特征在于,包括存儲器、處理器及存儲在存儲器上并可在處理器上運行的計算機程序,其中,所述處理器執(zhí)行所述計算機程序時實現(xiàn)如權(quán)利要求1-7任一項所述的晶體管布局方法。

技術(shù)總結(jié)

本申請公開了一種晶體管布局方法、裝置、存儲介質(zhì)及電子設(shè)備,其中,該晶體管布局方法包括獲取初始標準單元電路;確定初始標準單元電路中的待折疊晶體管;按照折疊策略對待折疊晶體管進行折疊處理,得到若干折疊晶體管;根據(jù)圖論算法對折疊晶體管建模,生成圖結(jié)構(gòu);基于圖結(jié)構(gòu)對若干折疊晶體管進行組合處理,并將組合后的折疊晶體管作為單獨元件進行布局,生成目標晶體管布局。本方案可以降低晶體管的布局復(fù)雜度。

技術(shù)研發(fā)人員:李旭,楊澤澄

受保護的技術(shù)使用者:上海概倫電子股份有限公司

技術(shù)研發(fā)日:

技術(shù)公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!