邏輯級數估算方法、裝置、電子設備及存儲介質與流程

本技術涉及數字電路的,具體而言,涉及一種邏輯級數估算方法、裝置、電子設備及存儲介質。

背景技術:

1、目前,在確定邏輯路徑的邏輯級數時,通常是先分析邏輯路徑包括的所有計算單元,然后根據預先配置的每種計算單元對應的邏輯級數,確定邏輯路徑包括的每一個計算單元對應的邏輯級數。最后將邏輯路徑包括的所有計算單元對應的邏輯級數求和,得到該邏輯路徑對應的總的邏輯級數。但是,此種方式估計得到的結果與實際結果往往存在較大差異。

技術實現思路

1、本技術提供一種邏輯級數估算方法、裝置、電子設備及存儲介質,以提高估算邏輯路徑的邏輯級數的準確性。

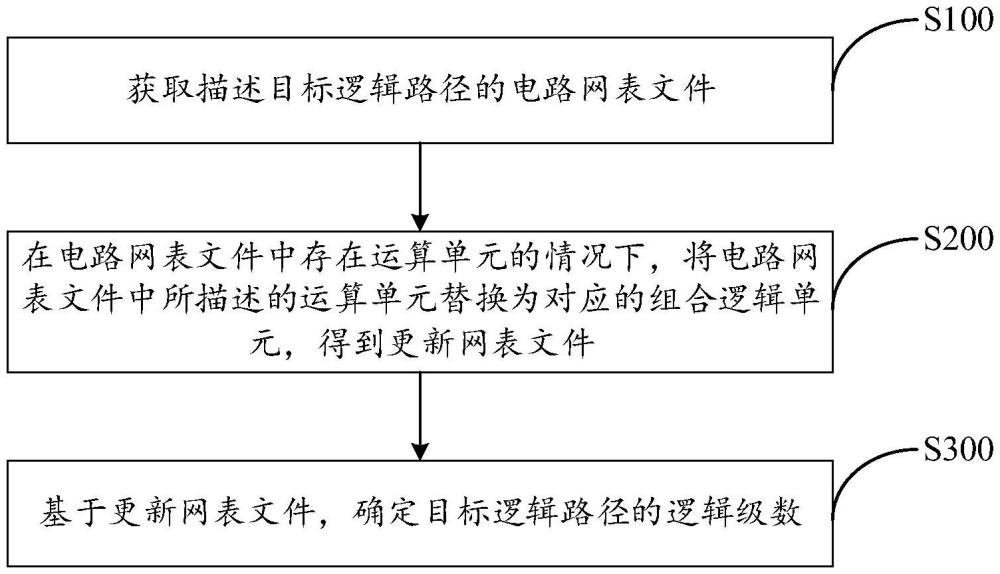

2、第一方面,本技術提供一種邏輯級數估算方法,包括:獲取描述目標邏輯路徑的電路網表文件,所述目標邏輯路徑為待估算邏輯級數的邏輯路徑;在所述電路網表文件中存在運算單元的情況下,將所述電路網表文件中所描述的運算單元替換為對應的組合邏輯單元,得到更新網表文件;其中,所述組合邏輯單元包括至少兩級基礎邏輯門電路;基于所述更新網表文件,確定所述目標邏輯路徑的邏輯級數;其中,所述目標邏輯路徑的邏輯級數與所述目標邏輯路徑包括的基礎邏輯門電路的數量有關。

3、本技術實施例中,通過將運算單元替換為其對應的組合邏輯單元,從而在進行邏輯級數的計算時,能考慮到運算單元的內部的具體邏輯結構。因此,即使有不同的邏輯路徑均經過了該運算單元,也能夠根據該運算單元對應的組合邏輯單元分別計算不同邏輯路徑對應的邏輯級數。而非是如同現有技術直接籠統的將該運算單元對應的邏輯級數設置為固定值,因此,通過本方案能更加準確的估計邏輯路徑的邏輯級數。

4、結合上述第一方面提供的技術方案,在一些可能的實施方式中,所述將所述電路網表文件中所描述的運算單元替換為對應的組合邏輯單元,得到更新網表文件,包括:確定出所述電路網表文件中的所有所述運算單元;從預設的組合邏輯單元庫中獲取各所述運算單元對應的組合邏輯單元;將每一所述運算單元分別替換為該運算單元對應的組合邏輯單元,得到所述更新網表文件。

5、本技術實施例中,通過將電路網表文件中的所有運算單元均替換為對應的組合邏輯單元,從而在需要對該待估算網表文件中的多條邏輯路徑分別進行邏輯級數估算時,無需針對該電路網表文件中包括的每一條邏輯路徑,重復進行該替換過程,減少了計算量。

6、結合上述第一方面提供的技術方案,在一些可能的實施方式中,所述將所述電路網表文件中所描述的運算單元替換為對應的運算單元網表文件,得到更新網表文件,包括:確定出所述電路網表文件中的所述目標邏輯路徑的所有所述運算單元;從預設的組合邏輯單元庫中獲取各所述運算單元對應的組合邏輯單元;將所述目標邏輯路徑中的每一所述運算單元分別替換為該運算單元對應的組合邏輯單元,得到所述更新網表文件。

7、本技術實施例中,通過將電路網表文件中目標邏輯路徑的所有運算單元均替換為對應的組合邏輯單元,從而在僅需要對目標邏輯路徑進行邏輯計算估算時,可以減少無關的運算單元的替換操作,減少工作量,提高了估算效率。

8、結合上述第一方面提供的技術方案,在一些可能的實施方式中,若所述組合邏輯單元庫中不存在所述運算單元對應的組合邏輯單元,所述方法還包括:獲取所述運算單元的硬件描述語言文件;將所述運算單元的硬件描述語言文件進行綜合,得到所述運算單元對應的組合邏輯單元;將所述目標邏輯路徑中的所述運算單元替換為該運算單元對應的組合邏輯單元,得到所述更新網表文件。

9、本技術實施例中,通過運算單元的硬件描述語言來得到對應的組合邏輯單元,從而可以簡單便捷的得到運算單元對應的組合邏輯單元。

10、結合上述第一方面提供的技術方案,在一些可能的實施方式中,在基于所述運算單元的硬件描述語言文件,得到所述運算單元對應的組合邏輯單元后,所述方法還包括:將所述運算單元對應的組合邏輯單元存儲至所述組合邏輯單元庫中。

11、本技術實施例中,通過將得到的組合邏輯單元存儲至組合邏輯單元庫中,從而在后續過程中,可以無需每次都去獲取硬件描述語言,并基于硬件描述語言文件得到運算單元對應的組合邏輯單元的操作,提高了獲取運算單元對應的組合邏輯單元的效率。

12、結合上述第一方面提供的技術方案,在一些可能的實施方式中,所述獲取描述目標邏輯路徑的電路網表文件,包括:獲取描述所述目標邏輯路徑的待估算rtl(寄存器傳輸級代碼)代碼以及sdc(synopsys?design?constraints,一種用于對數字電路設計進行約束的文件格式)約束文件;根據所述rtl代碼以及所述sdc約束文件,編譯得到所述電路網表文件。

13、結合上述第一方面提供的技術方案,在一些可能的實施方式中,基于所述更新網表文件,確定目標邏輯路徑的邏輯級數,包括:判斷所述目標邏輯路徑中多級基礎邏輯門電路包括的任意相鄰的多個基礎邏輯門電路是否可以合并為一個基礎邏輯門電路;將所述更新網表文件中可以合并的多個所述基礎邏輯門電路合并為一個基礎邏輯門電路;其中,被合并的多個基礎邏輯門電路與合并后的基礎邏輯門電路實現相同的功能;基于合并了多個所述基礎邏輯門電路后的更新網表文件,確定所述目標邏輯路徑的邏輯級數。

14、本技術實施例中,通過將多個可以合并的基礎邏輯門電路合并為一個基礎邏輯門電路,從而來模擬實際的電路設計過程中的將多個邏輯門電路進行合并的操作,從而使得通過本方案來進行的邏輯級數的估算結果更加貼合實際情況,提高估算結果的準確性。

15、結合上述第一方面提供的技術方案,在一些可能的實施方式中,基于所述更新網表文件,確定目標邏輯路徑的邏輯級數,包括:針對所述目標邏輯路徑中的第i個基礎邏輯門電路:以所述第i個基礎邏輯門電路為起點,判斷連續的n個基礎邏輯門電路是否可以合并為一個基礎邏輯門電路;若不可以合并,將n的值減1,并再次判斷連續的n個基礎邏輯門電路是否可以合并為一個基礎邏輯門電路;重復該步驟,直至連續的n個基礎邏輯門電路可以合并為一個基礎邏輯門電路,或者n的值減1后等于1;若前n個基礎邏輯門電路可以合并為一個基礎邏輯門電路,則:將該n個基礎邏輯門電路合并為一個基礎邏輯門電路,然后初始化n的值,若i+n小于m,則以第i+n個基礎邏輯門電路為起點,再次進行上述的判斷步驟;若i+n等于m,結束合并流程;m為未進行合并操作前的所述目標邏輯路徑包括的所有基礎邏輯門電路的數量;若n的值減1后等于1,則:初始化n的值,若i+1小于m,則以第i+1個基礎邏輯門電路為起點,再次進行上述的判斷步驟;若i+1等于m,結束合并流程;當結束合并流程后,基于完成合并流程后的目標邏輯路徑,確定所述目標邏輯路徑的邏輯級數。

16、本技術實施例中,通過判斷連續的n個基礎邏輯門電路是否可以合并為一個基礎邏輯門電路,從而將所有的可以合并的n個基礎邏輯門電路,均合并為一個基礎邏輯門電路。從而來模擬實際的電路設計過程中的將多個邏輯門電路進行合并的操作,使得通過本方案來進行的邏輯級數的估算結果更加貼合實際情況,提高估算結果的準確性。

17、結合上述第一方面提供的技術方案,在一些可能的實施方式中,基于所述更新網表文件,確定目標邏輯路徑的邏輯級數,包括:判斷當前的起點基礎邏輯門電路與所述起點基礎邏輯門電路之后連續的2個基礎邏輯門電路之間是否可以合并為一個基礎邏輯門電路;其中,所述起點基礎邏輯門電路為:所述更新網表文件中描述的所述目標邏輯路徑包括的基礎邏輯門電路;若當前的起點基礎邏輯門電路與所述起點基礎邏輯門電路之后連續的2個基礎邏輯門電路之間可以合并為一個基礎邏輯門電路,則:將當前的起點基礎邏輯門電路與所述起點基礎邏輯門電路之后連續的2個基礎邏輯門電路合并為一個基礎邏輯門電路,并以該起點基礎邏輯門電路之后連續的第3個基礎邏輯門電路作為新的起點基礎邏輯門電路,并重復上述操作;若當前的起點基礎邏輯門電路與所述起點基礎邏輯門電路之后連續的2個基礎邏輯門電路之間不可以合并為一個基礎邏輯門電路,則:判斷當前的起點基礎邏輯門電路與所述起點基礎邏輯門電路之后連續的1個基礎邏輯門電路之間是否可以合并為一個基礎邏輯門電路;若可以,將當前的起點基礎邏輯門電路與所述起點基礎邏輯門電路之后連續的1個基礎邏輯門電路合并為一個基礎邏輯門電路,并以該起點基礎邏輯門電路之后連續的第2個基礎邏輯門電路作為新的起點基礎邏輯門電路,并重復上述操作;若不可以,以所述當前的起點基礎邏輯門電路的下一個基礎邏輯門電路作為新的起點基礎邏輯門電路,并重復上述操作;在起點基礎邏輯門電路為所述目標邏輯路徑的最后一個基礎邏輯門電路,或最后一個基礎邏輯門電路被合并為一個新的基礎邏輯門電路的情況下,結束合并流程,基于完成合并流程后的目標邏輯路徑,確定所述目標邏輯路徑的邏輯級數。

18、本技術實施例中,通過將可以合并的連續的3個基礎邏輯門電路以及可以合并的連續的2個基礎邏輯門電路合并為一個基礎邏輯門電路,從而可以使得合并后的一個基礎邏輯門電路的輸入引腳數量小于等于4,進而使得合并后的一個基礎邏輯門電路能滿足工藝要求,提高本方案的實用性。

19、第二方面,本技術提供一種邏輯級數估算裝置,包括:獲取模塊和處理模塊。獲取模塊,用于獲取描述目標邏輯路徑的電路網表文件,所述目標邏輯路徑為待估算邏輯級數的邏輯路徑;處理模塊,用于在所述電路網表文件中存在運算單元的情況下,將所述電路網表文件中所描述的運算單元替換為對應的組合邏輯單元,得到更新網表文件;其中,所述組合邏輯單元包括至少兩級基礎邏輯門電路;所述處理模塊,還用于基于所述更新網表文件,確定所述目標邏輯路徑的邏輯級數;其中,所述目標邏輯路徑的邏輯級數與所述目標邏輯路徑包括的基礎邏輯門電路的數量有關。

20、第三方面,本技術提供一種電子設備,包括:存儲器和處理器,所述存儲器和所述處理器連接;所述存儲器,用于存儲程序;所述處理器,用于調用存儲于所述存儲器中的程序,以執行上述第一方面和/或結合上述第一方面任一可能的實施方式所述的方法。

21、第四方面,本技術提供一種計算機可讀存儲介質,其上存儲有計算機程序,所述計算機程序被計算機運行時,執行上述第一方面和/或結合上述第一方面任一可能的實施方式所述的方法。

- 還沒有人留言評論。精彩留言會獲得點贊!