一種神經(jīng)元計(jì)算機(jī)的芯片拓?fù)渚W(wǎng)絡(luò)的制作方法

本技術(shù)涉及神經(jīng)元計(jì)算機(jī),特別是涉及一種神經(jīng)元計(jì)算機(jī)的芯片拓?fù)渚W(wǎng)絡(luò)。

背景技術(shù):

1、神經(jīng)元計(jì)算機(jī)是指基于神經(jīng)形態(tài)硬件的新型計(jì)算機(jī)系統(tǒng),通常由多塊神經(jīng)形態(tài)硬件組成。

2、stdp(spike?time-dependent?plasticity)是脈沖神經(jīng)網(wǎng)絡(luò)中最為廣泛的學(xué)習(xí)算法之一,多數(shù)神經(jīng)形態(tài)芯片的計(jì)算需要考慮映射真實(shí)時(shí)間約束的時(shí)間步概念,因此,神經(jīng)網(wǎng)絡(luò)應(yīng)用所涉及的所有神經(jīng)元須在特定時(shí)間步時(shí)間內(nèi)完成脈沖數(shù)據(jù)計(jì)算,在眾核架構(gòu)中的形式普遍為所有涉及的神經(jīng)形態(tài)核心須在特定時(shí)間步時(shí)間內(nèi)完成脈沖計(jì)算,時(shí)間步的迭代過(guò)程在時(shí)間步同步模塊的控制下完成。

3、一般神經(jīng)形態(tài)硬件的時(shí)間步同步功能集成在片上網(wǎng)絡(luò)中,然而對(duì)于大規(guī)模芯片集成的神經(jīng)形態(tài)硬件系統(tǒng),芯片間的時(shí)間步同步必須考慮片內(nèi)和片外的數(shù)據(jù)傳輸和計(jì)算效率問(wèn)題,因此,如何優(yōu)化時(shí)間步同步的設(shè)計(jì)成為了研究者們所探究的目標(biāo)之一。

技術(shù)實(shí)現(xiàn)思路

1、基于此,有必要針對(duì)上述技術(shù)問(wèn)題,提供一種能夠讓時(shí)間步同步信號(hào)在大規(guī)模神經(jīng)形態(tài)硬件系統(tǒng)中有序傳遞和被識(shí)別,從而實(shí)現(xiàn)可擴(kuò)展、高可用大規(guī)模神經(jīng)形態(tài)硬件級(jí)聯(lián)運(yùn)行的神經(jīng)元芯片拓?fù)渚W(wǎng)絡(luò)。

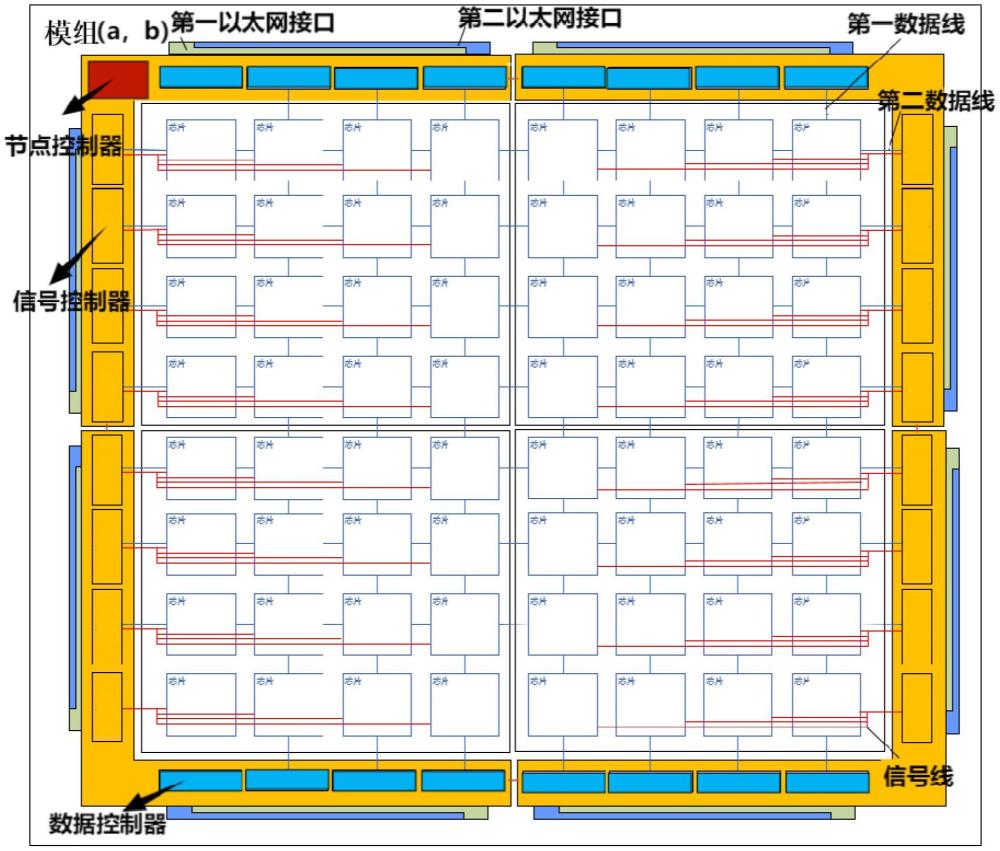

2、第一方面,本技術(shù)提供了一種神經(jīng)元計(jì)算機(jī)的芯片拓?fù)渚W(wǎng)絡(luò),所述神經(jīng)元芯片拓?fù)渚W(wǎng)絡(luò)包括m行×n列的模組,相鄰的模組之間通過(guò)第一以太網(wǎng)接口互聯(lián),每個(gè)模組由q×k個(gè)節(jié)點(diǎn)組成,每個(gè)節(jié)點(diǎn)由m×n個(gè)芯片組成,相鄰的每個(gè)芯片之間通過(guò)gpio接口互聯(lián);

3、每個(gè)節(jié)點(diǎn)設(shè)置有節(jié)點(diǎn)控制器、m個(gè)數(shù)據(jù)控制器以及n個(gè)信號(hào)控制器,所述節(jié)點(diǎn)控制器與各所述數(shù)據(jù)控制器、所述信號(hào)控制器通信連接;

4、每個(gè)節(jié)點(diǎn)還設(shè)置有沿芯片列方向排布且與所在列芯片電連接的m個(gè)第一數(shù)據(jù)線、沿芯片行方向排布且與所在行芯片電連接的n個(gè)第二數(shù)據(jù)線和n個(gè)信號(hào)線,所述第一數(shù)據(jù)線與數(shù)據(jù)控制器相連,所述第二數(shù)據(jù)線和所述信號(hào)線與信號(hào)控制器連接;所述數(shù)據(jù)控制器用于將接收到的第一以太網(wǎng)發(fā)送的第一對(duì)端模組傳輸?shù)牡谝幻}沖數(shù)據(jù),通過(guò)所述第一數(shù)據(jù)線發(fā)送給對(duì)應(yīng)的待同步芯片;

5、所述信號(hào)控制器用于將接收到的第一以太網(wǎng)發(fā)送的第二對(duì)端模組傳輸?shù)牡诙}沖數(shù)據(jù),通過(guò)所述第二數(shù)據(jù)線發(fā)送給對(duì)應(yīng)的待同步芯片,且響應(yīng)于所述節(jié)點(diǎn)控制器發(fā)送的時(shí)間步同步信號(hào),通過(guò)所述信號(hào)線控制對(duì)應(yīng)的待同步芯片進(jìn)行時(shí)間步同步計(jì)算。

6、在其中一個(gè)實(shí)施例中,所述相鄰的模組之間設(shè)置有第二以太網(wǎng)接口,所述第二以太網(wǎng)接口與外部軟件系統(tǒng)的通信接口互聯(lián),用于將接收到的所述外部軟件系統(tǒng)通過(guò)第二以太網(wǎng)發(fā)送的第三脈沖數(shù)據(jù),通過(guò)第一數(shù)據(jù)線或第二數(shù)據(jù)線傳輸至所述模組內(nèi)的待同步芯片。

7、在其中一個(gè)實(shí)施例中,所述信號(hào)控制器,還用于響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)牡谝煌脚渲眯畔ⅲO(jiān)聽(tīng)所述第二數(shù)據(jù)線上對(duì)應(yīng)的待同步芯片的同步特征信號(hào),若監(jiān)聽(tīng)到所述同步特征信號(hào),則響應(yīng)于所述節(jié)點(diǎn)控制器發(fā)送的時(shí)間步同步信號(hào),通過(guò)所述信號(hào)線控制所述對(duì)應(yīng)的待同步芯片進(jìn)行時(shí)間步同步計(jì)算。

8、在其中一個(gè)實(shí)施例中,所述第一同步配置信息包括主通道配置信息和從通道配置信息;

9、第一信號(hào)控制器,用于響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)闹魍ǖ琅渲眯畔ⅲO(jiān)聽(tīng)第二信號(hào)控制器上報(bào)的第一ready信號(hào),若監(jiān)聽(tīng)到所述第一ready信號(hào),則觸發(fā)所述第二信號(hào)控制器的時(shí)間步同步信號(hào);所述二信號(hào)控制器響應(yīng)于所述時(shí)間步同步信號(hào),通過(guò)所述信號(hào)線控制所述對(duì)應(yīng)的待同步芯片進(jìn)行時(shí)間步同步計(jì)算;

10、其中,所述第二信號(hào)控制器與所述第一信號(hào)控制器處于同一節(jié)點(diǎn)內(nèi)且響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)膹耐ǖ琅渲眯畔ⅲ?/p>

11、所述第一ready信號(hào)為所述第二信號(hào)控制器監(jiān)聽(tīng)到與其連接的待同步芯片的所述同步特征信號(hào)后生成。

12、在其中一個(gè)實(shí)施例中,第一節(jié)點(diǎn)控制器,用于響應(yīng)于第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)闹鞴?jié)點(diǎn)配置信息,監(jiān)聽(tīng)第二節(jié)點(diǎn)控制器上報(bào)的第二ready信號(hào),若監(jiān)聽(tīng)到所述第二ready信號(hào),則觸發(fā)所述第二節(jié)點(diǎn)控制器的時(shí)間步同步信號(hào);所述第二節(jié)點(diǎn)控制器響應(yīng)于所述時(shí)間步同步信號(hào),觸發(fā)與其通信連接的第三信號(hào)控制器的時(shí)間步同步信號(hào);

13、其中,所述第二節(jié)點(diǎn)控制器與所述第一節(jié)點(diǎn)控制器處于同一模組內(nèi)且響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)膹墓?jié)點(diǎn)配置信息;

14、所述第三信號(hào)控制器與所述第二節(jié)點(diǎn)控制器通信連接且響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)乃鲋魍ǖ琅渲眯畔ⅲ?/p>

15、所述第二ready信號(hào)為所述第二節(jié)點(diǎn)控制器監(jiān)聽(tīng)到所述第三信號(hào)控制器上報(bào)的第三ready信號(hào)后生成;所述第三ready信號(hào)為所述第三信號(hào)控制器監(jiān)聽(tīng)到與其連接的待同步芯片的同步特征信號(hào)以及第四信號(hào)控制器上報(bào)的第四ready信號(hào)后生成;

16、所述第四信號(hào)控制器與所述第三信號(hào)控制器處于同一節(jié)點(diǎn)內(nèi)且響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)乃鰪耐ǖ琅渲眯畔ⅲ凰龅谒膔eady信號(hào)為所述第四信號(hào)控制器監(jiān)聽(tīng)到與其連接的待同步芯片的同步特征信號(hào)后生成。

17、在其中一個(gè)實(shí)施例中,所述第一節(jié)點(diǎn)控制器,還用于響應(yīng)于第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)闹鞴?jié)點(diǎn)配置信息,監(jiān)聽(tīng)與其通信連接的第五信號(hào)控制器上報(bào)的第五ready信號(hào),若監(jiān)聽(tīng)到所述第五ready信號(hào),則觸發(fā)所述第五信號(hào)控制器的時(shí)間步同步信號(hào);所述第五信號(hào)控制器響應(yīng)于所述時(shí)間步同步信號(hào),通過(guò)所述信號(hào)線控制對(duì)應(yīng)的待同步芯片進(jìn)行時(shí)間步同步計(jì)算以及觸發(fā)所述第六信號(hào)控制器的時(shí)間步同步信號(hào);

18、其中,所述第五信號(hào)控制器與所述第一節(jié)點(diǎn)控制器處于同一節(jié)點(diǎn)內(nèi)且響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)乃鲋魍ǖ琅渲眯畔ⅲ?/p>

19、所述第六信號(hào)控制器與所述第一節(jié)點(diǎn)控制器處于同一個(gè)節(jié)點(diǎn)內(nèi)且響應(yīng)于所述第一以太網(wǎng)或第二以太網(wǎng)傳輸?shù)乃鰪耐ǖ琅渲眯畔ⅲ?/p>

20、所述第五ready信號(hào)為所述第五信號(hào)控制器監(jiān)聽(tīng)到與其連接的待同步芯片上報(bào)的所述同步特征信號(hào)以及所述第六信號(hào)控制器上報(bào)的第六ready信號(hào)后生成;

21、所述第六ready信號(hào)為所述第六信號(hào)控制器監(jiān)聽(tīng)到與其連接的待同步芯片上報(bào)的所述同步特征信號(hào)后生成。

22、在其中一個(gè)實(shí)施例中,所述同步特征信號(hào)包括時(shí)間步固定周期信號(hào)、待機(jī)信號(hào),第一時(shí)間步分隔信號(hào),

23、所述時(shí)間步固定周期信號(hào)為所述待同步芯片接收到所述第一數(shù)據(jù)線或所述第二數(shù)據(jù)線傳輸?shù)牡谝幻}沖數(shù)據(jù)或第二脈沖數(shù)據(jù)或第三脈沖數(shù)據(jù)后,生成的時(shí)間步周期預(yù)估結(jié)果;

24、所述待機(jī)信號(hào)為所述待同步芯片完成上一時(shí)間步的第一脈沖數(shù)據(jù)或第二脈沖數(shù)據(jù)或第三脈沖數(shù)據(jù)后,生成的待機(jī)信號(hào);

25、所述第一時(shí)間步分隔信號(hào)用于分隔所述第三脈沖數(shù)據(jù)的每個(gè)時(shí)間步的計(jì)算數(shù)據(jù)。

26、在其中一個(gè)實(shí)施例中,所述同步特征信號(hào)還包括:第二時(shí)間步分隔信號(hào),用于分隔所述第一脈沖數(shù)據(jù)或第二脈沖數(shù)據(jù)的每個(gè)時(shí)間步的計(jì)算數(shù)據(jù)。

27、在其中一個(gè)實(shí)施例中,所述同步特征信號(hào)還包括:時(shí)序延遲信號(hào),

28、所述時(shí)序延遲信號(hào)為所述待同步芯片通過(guò)第一數(shù)據(jù)線或第二數(shù)據(jù)線延遲接收到的所述第一脈沖數(shù)據(jù)或第二脈沖數(shù)據(jù)產(chǎn)生的信號(hào)。

29、在其中一個(gè)實(shí)施例中,所述q=k,所述m=n。

30、上述神經(jīng)元計(jì)算機(jī)的芯片拓?fù)渚W(wǎng)絡(luò)中,通過(guò)在每個(gè)模組內(nèi)設(shè)置節(jié)點(diǎn)控制器、數(shù)據(jù)控制器以及信號(hào)控制器,將所述節(jié)點(diǎn)控制器與各所述數(shù)據(jù)控制器、所述信號(hào)控制器通信連接;每個(gè)節(jié)點(diǎn)還設(shè)置有沿芯片列方向排布且與所在列芯片電連接的m個(gè)第一數(shù)據(jù)線、沿芯片行方向排布且與所在行芯片電連接的n個(gè)第二數(shù)據(jù)線和n個(gè)信號(hào)線,所述第一數(shù)據(jù)線與數(shù)據(jù)控制器相連,所述第二數(shù)據(jù)線和所述信號(hào)線與信號(hào)控制器連接;所述數(shù)據(jù)控制器用于將接收到的第一以太網(wǎng)發(fā)送的第一對(duì)端模組傳輸?shù)牡谝幻}沖數(shù)據(jù),通過(guò)所述第一數(shù)據(jù)線發(fā)送給對(duì)應(yīng)的待同步芯片;所述信號(hào)控制器用于將接收到的第一以太網(wǎng)發(fā)送的第二對(duì)端模組傳輸?shù)牡诙}沖數(shù)據(jù),通過(guò)所述第二數(shù)據(jù)線發(fā)送給對(duì)應(yīng)的待同步芯片,且響應(yīng)于所述節(jié)點(diǎn)控制器發(fā)送的時(shí)間步同步信號(hào),通過(guò)所述信號(hào)線控制對(duì)應(yīng)的待同步芯片進(jìn)行時(shí)間步同步計(jì)算,構(gòu)造了神經(jīng)元計(jì)算機(jī)硬件的新型芯片拓?fù)渚W(wǎng)絡(luò),具備高可擴(kuò)展性,同時(shí)實(shí)現(xiàn)了多模組芯片陣列高效的互聯(lián)運(yùn)行。

- 基于持續(xù)性數(shù)據(jù)學(xué)習(xí)的城市產(chǎn)業(yè)...

- 基于收件地匹配最近倉(cāng)庫(kù)、最經(jīng)...

- 基于多維度數(shù)據(jù)的片區(qū)建站評(píng)估...

- 一種基于產(chǎn)業(yè)大數(shù)據(jù)的智能決策...

- 一種視頻搜索方法、電子設(shè)備、...

- 基于LAB顏色空間的彩色圖像...

- 一種數(shù)字記憶互聯(lián)黑板與顯示屏...

- 基于大語(yǔ)言模型的多智能體城市...

- 血管分割模型、模型訓(xùn)練方法、...

- 一種工程設(shè)計(jì)項(xiàng)目流程管理系統(tǒng)...

- 還沒(méi)有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!