電平位移電路的制作方法

本發明涉及微電子、半導體及通信技術,尤其涉及一種電平位移電路。

背景技術:

1、近年來隨著射頻芯片設計技術的快速發展,射頻開關、衰減器、移相器等控制類芯片的設計和使用愈發成熟,單一功能的器件也逐漸無法滿足市場的需求。多位數控電路隨之誕生,控制電路的加入使得開關、衰減器、移相器等器件的設計變得復雜多樣,但同時也實現了豐富的控制邏輯,進而為用戶提供更加先進且寬泛的應用場景。

2、邏輯控制電路常會使用非門、或門、與非門、或非門等數字電路,其中使用頻次較多的組合邏輯電路有二四譯碼器,它集成了非門和或非門電路。在數字電路中,該電路的使用非常廣泛且成熟,但是在gaas工藝中,由于工藝原因,其數字電路建模難度較大,模型建立不準確。在電路仿真中使用的邏輯管存在閾值電壓波動,進而導致數字電路電平誤翻轉、不翻轉的現象。這就導致工藝本身可以實現的電路,在特定工藝條件下模型仿真時卻無法實現。該現象弱化了電路模型仿真的準確性,也打擊了設計人員的自信心。

技術實現思路

1、基于此,有必要針對現有技術的gaas工藝電平位移電路效果較差的技術問題,提出了一種電平位移電路,所述電路包括:

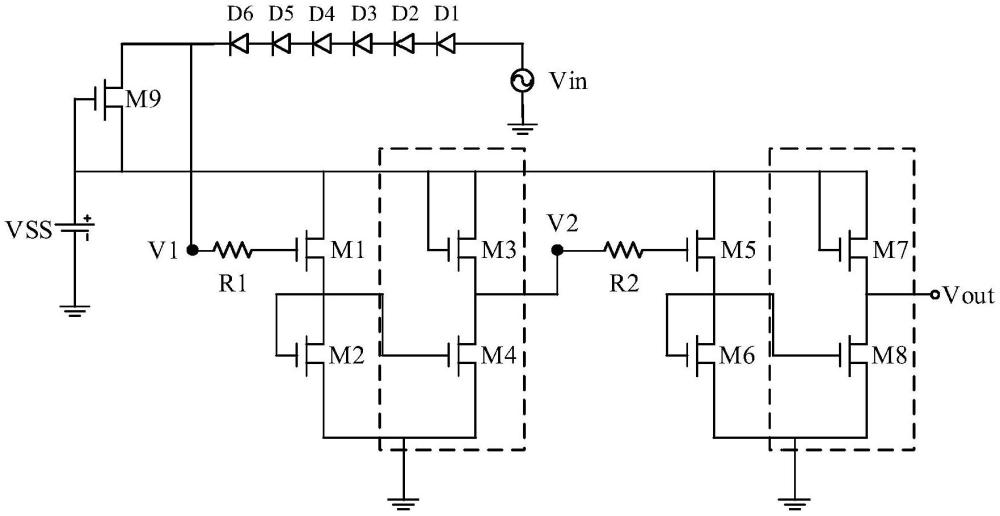

2、二極管d1、二極管d2、二極管d3、二極管d4、二極管d5、二極管d6、晶體管m1、晶體管m2、晶體管m3、晶體管m4、晶體管m5、晶體管m6、晶體管m7、晶體管m8、電阻r1、電阻r2;

3、二極管d1的陽極連接交流信號源,二極管d1的陰極連接所述二極管d2的陽極,二極管d2的陰極連接所述二極管d3的陽極,二極管d3的陰極連接所述二極管d4的陽極,二極管d4的陰極連接所述二極管d5的陽極,二極管d5的陰極連接所述二極管d6的陽極,二極管d6的陰極分別連接所述電阻r1的一端、晶體管m9的漏極,晶體管m9的源極以及柵極接vss;

4、電阻r1的另一端連接晶體管m1的柵極,晶體管m1的漏極接vss,所述晶體管m1的源極分別連接晶體管m2的柵極以及漏極,晶體管m2的源極接地,晶體管m2的柵極連接晶體管m4的柵極,晶體管m4的源極接地,晶體管m4的漏極分別連接晶體管m3的源極以及電阻r2的一端,晶體管m3的柵極以及漏極連接vss,電阻r2的另一端連接晶體管m5的柵極,晶體管m5的漏極接vss,晶體管m5的源極分別連接晶體管m6的漏極以及柵極,晶體管m6的源極接地,晶體管m6的柵極連接晶體管m8的柵極,晶體管m8的源極接地,晶體管m8的漏極分別接輸出端口以及晶體管m7的源極,晶體管m7的柵極以及漏極接vss。

5、本發明提出的電平位移電路二極管d1、二極管d2、二極管d3、二極管d4、二極管d5、二極管d6、晶體管m1、晶體管m2、晶體管m3、晶體管m4、晶體管m5、晶體管m6、晶體管m7、晶體管m8、電阻r1、電阻r2,二極管d1的陽極連接交流信號源,二極管d1的陰極連接所述二極管d2的陽極,二極管d2的陰極連接所述二極管d3的陽極,二極管d3的陰極連接所述二極管d4的陽極,二極管d4的陰極連接所述二極管d5的陽極,二極管d5的陰極連接所述二極管d6的陽極,二極管d6的陰極分別連接所述電阻r1的一端、晶體管m9的漏極,晶體管m9的源極以及柵極接vss;電阻r1的另一端連接晶體管m1的柵極,晶體管m1的漏極接vss,所述晶體管m1的源極分別連接晶體管m2的柵極以及漏極,晶體管m2的源極接地,晶體管m2的柵極連接晶體管m4的柵極,晶體管m4的源極接地,晶體管m4的漏極分別連接晶體管m3的源極以及電阻r2的一端,晶體管m3的柵極以及漏極連接vss,電阻r2的另一端連接晶體管m5的柵極,晶體管m5的漏極接vss,晶體管m5的源極分別連接晶體管m6的漏極以及柵極,晶體管m6的源極接地,晶體管m6的柵極連接晶體管m8的柵極,晶體管m8的源極接地,晶體管m8的漏極分別接輸出端口以及晶體管m7的源極,晶體管m7的柵極以及漏極接vss。本發明圍繞電平翻轉這一方向去進行電路優化改進,由于本電平位移電路中的反相器由4個晶體管組成使輸出端高阻抗更加穩定,故受級聯影響較小,提高了電路仿真和實測的一致性,從而提高設計的一次性成功率。

技術特征:

1.一種電平位移電路,其特征在于,所述電平位移電路包括:二極管d1、二極管d2、二極管d3、二極管d4、二極管d5、二極管d6、晶體管m1、晶體管m2、晶體管m3、晶體管m4、晶體管m5、晶體管m6、晶體管m7、晶體管m8、電阻r1、電阻r2;

技術總結

本申請涉及微電子、半導體及通信技術技術領域,揭示了一種電平位移電路,所述電路包括:二極管D1、二極管D2、二極管D3、二極管D4、二極管D5、二極管D6、晶體管M1、晶體管M2、晶體管M3、晶體管M4、晶體管M5、晶體管M6、晶體管M7、晶體管M8、電阻R1、電阻R2。本發明圍繞電平翻轉這一方向去進行電路優化改進,由于本電平位移電路中的反相器由4個晶體管組成使輸出端高阻抗更加穩定,故受級聯影響較小,提高了電路仿真和實測的一致性,從而提高設計的一次性成功率。

技術研發人員:王東東,張健鑫,張博

受保護的技術使用者:博瑞集信(西安)電子科技股份有限公司

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!