一種用于光通信的數據處理方法及相關裝置與流程

本技術實施例涉及光通信領域,尤其涉及一種用于光通信的數據處理方法及相關裝置。

背景技術:

1、在5g、云計算、大數據、人工智能等持續推動下,高速光傳輸網絡正朝著大容量、分組化、智能化的方向發展。相干光通信系統利用光波的幅度,相位,偏振和頻率來承載信息。為了對抗在傳輸過程中因色散、偏振相關損傷、噪聲、非線性效應及其它因素引起的光信號失真并保持長距離傳輸,相干光通信系統通常需要采用高效的前向糾錯(forward?errorcorrection,fec)碼來對抗光傳輸過程中的光學損傷,以保持長距離傳輸時其誤比特率足夠低。在400g?zr場景中,光模塊采用cfec級聯編碼,其中外碼采用階梯(staircase,sc)碼,內碼采用雙比特擴展漢明(hamming)碼,級聯編碼冗余約為14.8%,糾錯能力為糾前誤比特率1.25e-2。

2、對于未來城域電信傳輸和城域數據中心互聯(data?center?interconnect,dci)場景,如1.6t-zr場景,在考慮16進制的雙偏振正交振幅調制(dual?polarization?16-state?quadrature?amplitude?modulation,dp-16qam)的情況下,其波特率在約240gb甚至以上;又如,考慮雙偏振正交相移鍵控(dual?polarization?quadrature?phase?shiftkeying,dp-qpsk)調制的800g速率場景長距離傳輸,其波特率在約240gb甚至以上。一方面,現有的采用cfec編碼的數據處理和傳輸方法無法適用未來具有高波特率的場景,另一方面,現有cfec編碼的數據處理和傳輸方法在兼容dp-qpsk調制方面適配性較差,這是未來亟需解決的問題。

技術實現思路

1、申請實施例提供了一種用于光通信的數據處理方法及相關裝置,通過采用增益更高的內碼編碼提升了級聯編碼的性能,同時,通過設計具體的數據處理方法,使得更好地兼容dp-16qam和dp-qpsk調制,有利于應用在未來采用dp-16qam的1.6t-zr的場景和采用dp-qpsk的800g等高波特率長距離傳輸場景。

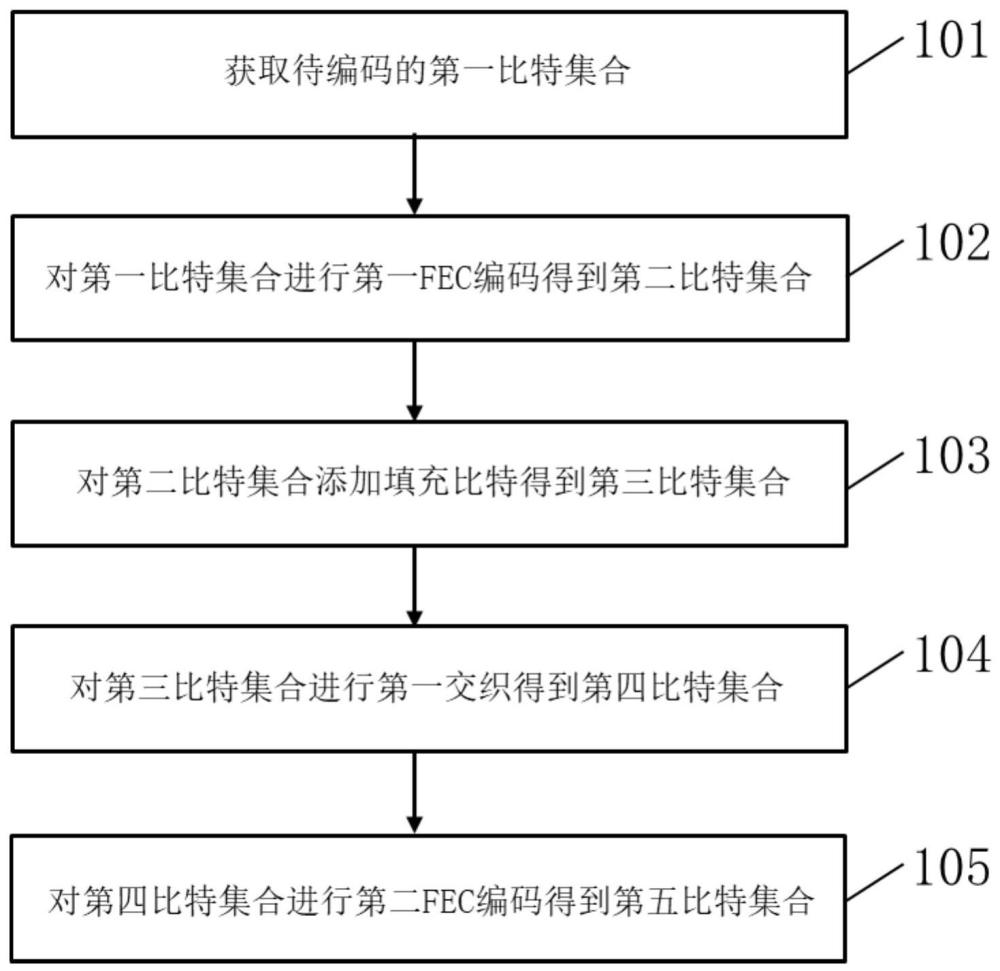

2、第一方面,本技術實施例提供了一種用于光通信的數據處理方法。首先,獲取第一比特集合,其中,第一比特集合包括d1個比特,d1=244664×l,l為正整數。之后,對所述第一比特集合進行第一前向糾錯(forward?error?correction,fec)編碼得到第二比特集合,其中,所述第二比特集合包括d2個比特,所述第一比特集合中的每244664個比特經過所述第一fec編碼得到所述第二比特集合中的每261086個比特,d2=261086×l。接下來,對所述第二比特集合添加dpad個填充比特得到第三比特集合,dpad為大于或等于0的整數。進而,對所述第三比特集合進行第二fec編碼得到第四比特集合。

3、在該實施方式中,是以244664個比特為粒度進行第一fec編碼(外碼編碼),獲取第一比特集合中的比特個數d1=244664×l也是244664的倍數,使得具有更好的實現效果,便于硬件實現,復雜度更低。在此基礎上,通過采用增益更高的內碼編碼提升了級聯編碼的性能,同時,通過設計具體的數據處理方法,使得更好地兼容dp-16qam和dp-qpsk調制,有利于應用在未來采用dp-16qam的1.6t-zr的場景和采用dp-qpsk的800g等高波特率長距離傳輸場景。

4、在一些可能的實施方式中,所述第一比特集合中的d1個比特分布為r行2056列,r=119×l,待編碼的比特采用行列分布的比特矩陣具有較好的實用效果。采用2056列分布,比現有的10280列更小,更有利于未來方案的擴展。

5、在一些可能的實施方式中,所述第二比特集合中的每261086個比特分布為119行2194列,所述2194列中的前2056列用于承載所述第一比特集合中的244664個比特。由于每119行中的前2056列總共2056×119=244664個比特剛好承載外碼編碼中的244664個載荷比特,因此,這種處理方法具有更好的數據匹配性,使得硬件實現簡單,復雜度較低。

6、在一些可能的實施方式中,所述第二比特集合中的每261086個比特包括所述第一比特集合中的244664個比特、所述32個第一類型比特、所述6個第二類型比特和16384個第一fec編碼的校驗比特。在一些具體應用中,32個第一類型比特是通過將244664個載荷(payload)比特進行循環冗余校驗(cyclic?redundancy?check,crc)獲得。典型的,crc采用crc-32校驗。在另一些具體應用中,32個第一類型比特是32個保留比特,簡稱為res。6個第二類型比特是多分組對齊信號(multi?block?alignment?signal,mbas)。

7、在一些可能的實施方式中,對所述第二比特集合添加dpad個填充比特得到第三比特集合之后,對所述第三比特集合進行第二fec編碼得到第四比特集合之前,所述方法還包括:對所述第三比特集合進行第一交織。可以減小內碼編碼與外碼編碼之間錯誤相關性的傳遞,更有效的抵抗突發錯誤。

8、在一些可能的實施方式中,對所述第三比特集合進行第一交織包括:根據p條延遲線對來自所述第三比特集合中的比特進行延遲。所述p為大于1的整數,每條延遲線包括的存儲單元數量各不相同,存儲單元數量最小的延遲線包括0個存儲單元,每相鄰兩條延遲線的存儲單元數量的差值為q。每個存儲單元用于存儲d個比特,輸入的比特按照所述p條延遲線的序號依次輸入所述p條延遲線,每條延遲線單次輸入d個比特且單次輸出d個比特,經過卷積交織后輸出的連續p×d個比特包括每條延遲線輸出的d個比特,q和d均為大于或等于1的整數。該實施方式提供了一種第一交織的具體實現方式,即采用卷積交織的方式實現,具有較好的實用效果。

9、在一些可能的實施方式中,所述第四比特集合包括r個碼字,每個所述碼字的長度為n個比特,所述每個碼字包括k個信息比特,r、n和k均為大于1的整數,n大于k,所述第三比特集合包括r×k個比特,r×k=261086×l+dpad,k是d的整數倍,p×d是k的整數倍,是p的整數倍。該實施方式中,第三比特集合的長度是內碼編碼的信息比特長度k的整數倍,便于內碼同步后快速進行外碼同步,使得硬件實現簡單,復雜度較低。

10、在一些可能的實施方式中,所述第一交織后的第三比特集合包括r行k列個比特,所述第一交織后的第三比特集合中每行的k個比特為條延遲線輸出的k個比特。對第三比特集合進行第二fec編碼得到第四比特集合包括:對所述第一交織后的第三比特集合中每行的k個比特進行所述第二fec編碼得到所述第四比特集合中每個所述碼字的n個比特。采用此種方式,在對第三比特集合中的數據進行卷積交織前,卷積交織器輸入和輸出的開關初始化到延遲線0,當第三比特集合中的數據全部輸入卷積交織器后,卷積交織器的輸入和輸出的開關重新回到延遲線0,此便于收端進行解卷積交織器的同步,使得硬件實現簡單。典型的,所述k=d,r是p的整數倍,使得數據處理流程更簡單,硬件實現復雜度低。

11、在一些可能的實施方式中,所述第二fec編碼采用bch編碼或擴展bch編碼,提升了級聯編碼的性能。

12、在一些可能的實施方式中,對所述第二比特集合添加dpad個填充比特得到第三比特集合之后,對所述第三比特集合進行第二fec編碼得到第四比特集合之前,所述方法還包括:對所述第三比特集合進行加擾。使得加擾后的比特數據中0和1更趨向于等概率,使得直流平衡,利于收端接收。

13、在一些可能的實施方式中,對所述第三比特集合進行第二fec編碼得到第四比特集合之后,所述方法還包括:對所述第四比特集合進行數據處理。所述數據處理包括符號映射、第二交織、偏振劃分和成幀處理。

14、在一些可能的實施方式中,所述第四比特集合包括r個碼字,每個所述碼字的長度為n個比特,所述每個碼字包括k個信息比特,r、n和k均為大于1的整數,n大于k。k=113,n=127,或者,k=113,n=128,或者,k=112,n=128,或者,k=110,n=126,或者,k=119,n=136,或者,k=119,n=135。該實施方式提供的幾種內碼編碼方案,采用的有限域的階數較低,便于硬件實現。

15、在一些可能的實施方式中,k=113,n=127,r和dpad滿足如下其中一個條件:

16、r=119,dpad=1074;

17、r=238,dpad=340;

18、r=357,dpad=1414;

19、r=476,dpad=680;

20、r=595,dpad=1754;

21、r=714,dpad=1020;

22、r=833,dpad=286;

23、r=952,dpad=1360;

24、r=1071,dpad=626;

25、r=1190,dpad=1700;

26、r=1309,dpad=966;

27、r=1428,dpad=232;

28、r=1547,dpad=1306;

29、r=1666,dpad=572;

30、r=1785,dpad=1646;

31、r=1904,dpad=912;

32、r=2023,dpad=178;

33、r=2142,dpad=1252;

34、r=2261,dpad=518;

35、r=2380,dpad=1592。

36、在一些可能的實施方式中,k=113,n=128,r和dpad滿足如下其中一個條件:r=119,dpad=1074;

37、r=238,dpad=340;

38、r=357,dpad=1414;

39、r=476,dpad=680;

40、r=595,dpad=1754;

41、r=714,dpad=1020;

42、r=833,dpad=286;

43、r=952,dpad=1360;

44、r=1071,dpad=626;

45、r=1190,dpad=1700;

46、r=1309,dpad=966;

47、r=1428,dpad=232;

48、r=1547,dpad=1306;

49、r=1666,dpad=572;

50、r=1785,dpad=1646;

51、r=1904,dpad=912;

52、r=2023,dpad=178;

53、r=2142,dpad=1252;

54、r=2261,dpad=518;

55、r=2380,dpad=1592。

56、在一些可能的實施方式中,k=112,n=128,r和dpad滿足如下其中一個條件:r=119,dpad=546;

57、r=238,dpad=1092;

58、r=357,dpad=1638;

59、r=476,dpad=392;

60、r=595,dpad=938;

61、r=714,dpad=1484;

62、r=833,dpad=238;

63、r=952,dpad=784;

64、r=1071,dpad=1330;

65、r=1190,dpad=84;

66、r=1309,dpad=630;

67、r=1428,dpad=1176;

68、r=1547,dpad=1722;

69、r=1666,dpad=476;

70、r=1785,dpad=1022;

71、r=1904,dpad=1568;

72、r=2023,dpad=322;

73、r=2142,dpad=868;

74、r=2261,dpad=1414;

75、r=2380,dpad=168。

76、在一些可能的實施方式中,k=110,n=126,r和dpad滿足如下其中一個條件:r=119,dpad=1154;

77、r=238,dpad548;

78、r=357,dpad=1702;

79、r=476,dpad=1096;

80、r=595,dpad=490;

81、r=714,dpad=1644;

82、r=833,dpad=1038;

83、r=952,dpad=432;

84、r=1071,dpad=1586;

85、r=1190,dpad=980;

86、r=1309,dpad=374;

87、r=1428,dpad=1528;

88、r=1547,dpad=922;

89、r=1666,dpad=316;

90、r=1785,dpad=1470;

91、r=1904,dpad=864;

92、r=2023,dpad=258;

93、r=2142,dpad=1412;

94、r=2261,dpad=806;

95、r=2380,dpad=200。

96、在一些可能的實施方式中,k=119,n=136,r和dpad滿足如下其中一個條件:r=119,dpad=1666;

97、r=238,dpad=1428;

98、r=357,dpad=1190;

99、r=476,dpad=952;

100、r=595,dpad=714;

101、r=714,dpad=476;

102、r=833,dpad=238;

103、r=952,dpad=1904;

104、r=1071,dpad=1666;

105、r=1190,dpad=1428;

106、r=1309,dpad=1190;

107、r=1428,dpad=952;

108、r=1547,dpad=714;

109、r=1666,dpad=476;

110、r=1785,dpad=238;

111、r=1904,dpad=0;

112、r=2023,dpad=1666;

113、r=2142,dpad=1428;

114、r=2261,dpad=1190;

115、r=2380,dpad=952。

116、在一些可能的實施方式中,k=119,n=135,r和dpad滿足如下其中一個條件:r=119,dpad=1666;

117、r=238,dpad=1428;

118、r=357,dpad=1190;

119、r=476,dpad=952;

120、r=595,dpad=714;

121、r=714,dpad=476;

122、r=833,dpad=238;

123、r=952,dpad=1904;

124、r=1071,dpad=1666;

125、r=1190,dpad=1428;

126、r=1309,dpad=1190;

127、r=1428,dpad=952;

128、r=1547,dpad=714;

129、r=1666,dpad=476;

130、r=1785,dpad=238;

131、r=1904,dpad=0;

132、r=2023,dpad=1666;

133、r=2142,dpad=1428;

134、r=2261,dpad=1190;

135、r=2380,dpad=952。

136、第二方面,本技術實施例提供了一種數據處理裝置。該數據處理裝置包括:獲取單元、第一編碼單元、填充單元和第二編碼單元。所述獲取單元用于:獲取第一比特集合,所述第一比特集合包括d1個比特,d1=244664×l,l為正整數。所述第一編碼單元用于:對所述第一比特集合進行第一前向糾錯fec編碼得到第二比特集合,所述第二比特集合包括d2個比特,所述第一比特集合中的每244664個比特經過所述第一fec編碼得到所述第二比特集合中的每261086個比特,d2=261086×l。所述填充單元用于:對所述第二比特集合添加dpad個填充比特得到第三比特集合,dpad為大于或等于0的整數。所述第二編碼單元用于:對所述第三比特集合進行第二fec編碼得到第四比特集合。

137、在該實施方式中,是以244664個比特為粒度進行第一fec編碼(外碼編碼),獲取第一比特集合中的比特個數d1=244664×l也是244664的倍數,使得具有更好的實現效果,便于硬件實現,復雜度更低。在此基礎上,通過采用增益更高的內碼編碼提升了級聯編碼的性能,同時,通過設計具體的數據處理方法,使得更好地兼容dp-16qam和dp-qpsk調制,有利于應用在未來采用dp-16qam的1.6t-zr的場景和采用dp-qpsk的800g等高波特率長距離傳輸場景。

138、在一些可能的實施方式中,所述第一比特集合中的d1個比特分布為r行2056列,r=119×l,待編碼的比特采用行列分布的比特矩陣具有較好的實用效果。采用2056列分布,比現有的10280列更小,更有利于未來方案的擴展。

139、在一些可能的實施方式中,所述第二比特集合中的每261086個比特分布為119行2194列,所述2194列中的前2056列用于承載所述第一比特集合中的244664個比特。由于每119行中的前2056列總共2056×119=244664個比特剛好承載外碼編碼中的244664個載荷比特,因此,這種處理方法具有更好的數據匹配性,使得硬件實現簡單,復雜度較低。

140、在一些可能的實施方式中,所述第二比特集合中的每261086個比特包括所述第一比特集合中的244664個比特、所述32個第一類型比特、所述6個第二類型比特和16384個第一fec編碼的校驗比特。在一些具體應用中,32個第一類型比特是通過將244664個載荷(payload)比特進行crc獲得。典型的,crc采用crc-32校驗。在另一些具體應用中,32個第一類型比特是32個保留比特,簡稱為res。6個第二類型比特是mbas。

141、在一些可能的實施方式中,所述數據處理裝置還包括交織單元,對所述第二比特集合添加dpad個填充比特得到第三比特集合之后,對所述第三比特集合進行第二fec編碼得到第四比特集合之前,交織單元用于:對所述第三比特集合進行第一交織。可以減小內碼編碼與外碼編碼之間錯誤相關性的傳遞,更有效的抵抗突發錯誤。

142、在一些可能的實施方式中,所述交織單元具體用于:根據p條延遲線對來自所述第三比特集合中的比特進行延遲。所述p為大于1的整數,每條延遲線包括的存儲單元數量各不相同,存儲單元數量最小的延遲線包括0個存儲單元,每相鄰兩條延遲線的存儲單元數量的差值為q。每個存儲單元用于存儲d個比特,輸入的比特按照所述p條延遲線的序號依次輸入所述p條延遲線,每條延遲線單次輸入d個比特且單次輸出d個比特,經過卷積交織后輸出的連續p×d個比特包括每條延遲線輸出的d個比特,q和d均為大于或等于1的整數。該實施方式提供了一種第一交織的具體實現方式,即采用卷積交織的方式實現,具有較好的實用效果。

143、在一些可能的實施方式中,所述第四比特集合包括r個碼字,每個所述碼字的長度為n個比特,所述每個碼字包括k個信息比特,r、n和k均為大于1的整數,n大于k,所述第三比特集合包括r×k個比特,r×k=261086×l+dpad,k是d的整數倍,p×d是k的整數倍,是p的整數倍。該實施方式中,第三比特集合的長度是內碼編碼的信息比特長度k的整數倍,便于內碼同步后快速進行外碼同步,使得硬件實現簡單,復雜度較低。

144、在一些可能的實施方式中,所述第一交織后的第三比特集合包括r行k列個比特,所述第一交織后的第三比特集合中每行的k個比特為條延遲線輸出的k個比特。對第三比特集合進行第二fec編碼得到第四比特集合包括:對所述第一交織后的第三比特集合中每行的k個比特進行所述第二fec編碼得到所述第四比特集合中每個所述碼字的n個比特。采用此種方式,在對第三比特集合中的數據進行卷積交織前,卷積交織器輸入和輸出的開關初始化到延遲線0,當第三比特集合中的數據全部輸入卷積交織器后,卷積交織器的輸入和輸出的開關重新回到延遲線0,此便于收端進行解卷積交織器的同步,使得硬件實現簡單。典型的,所述k=d,r是p的整數倍,使得數據處理流程更簡單,硬件實現復雜度低。

145、在一些可能的實施方式中,所述第二fec編碼采用bch編碼或擴展bch編碼,提升了級聯編碼的性能。

146、在一些可能的實施方式中,數據處理裝置還包括加擾單元,對所述第二比特集合添加dpad個填充比特得到第三比特集合之后,對所述第三比特集合進行第二fec編碼得到第四比特集合之前,加擾單元用于對所述第三比特集合進行加擾,使得加擾后的比特數據中0和1更趨向于等概率,使得直流平衡,利于收端接收。

147、在一些可能的實施方式中,數據處理裝置還包括數據處理單元,對所述第三比特集合進行第二fec編碼得到第四比特集合之后,數據處理單元用于對所述第四比特集合進行數據處理。所述數據處理包括符號映射、第二交織、偏振劃分和成幀處理。

148、在一些可能的實施方式中,所述第四比特集合包括r個碼字,每個所述碼字的長度為n個比特,所述每個碼字包括k個信息比特,r、n和k均為大于1的整數,n大于k。k=113,n=127,或者,k=113,n=128,或者,k=112,n=128,或者,k=110,n=126,或者,k=119,n=136,或者,k=119,n=135。該實施方式提供的幾種內碼編碼方案,采用的有限域的階數較低,便于硬件實現。

149、在一些可能的實施方式中,k=113,n=127,r和dpad滿足如下其中一個條件:

150、r=119,dpad=1074;

151、r=238,dpad=340;

152、r=357,dpad=1414;

153、r=476,dpad=680;

154、r=595,dpad=1754;

155、r=714,dpad=1020;

156、r=833,dpad=286;

157、r=952,dpad=1360;

158、r=1071,dpad=626;

159、r=1190,dpad=1700;

160、r=1309,dpad=966;

161、r=1428,dpad=232;

162、r=1547,dpad=1306;

163、r=1666,dpad=572;

164、r=1785,dpad=1646;

165、r=1904,dpad=912;

166、r=2023,dpad=178;

167、r=2142,dpad=1252;

168、r=2261,dpad=518;

169、r=2380,dpad=1592。

170、在一些可能的實施方式中,k=113,n=128,r和dpad滿足如下其中一個條件:

171、r=119,dpad=1074;

172、r=238,dpad=340;

173、r=357,dpad=1414;

174、r=476,dpad=680;

175、r=595,dpad=1754;

176、r=714,dpad=1020;

177、r=833,dpad=286;

178、r=952,dpad=1360;

179、r=1071,dpad=626;

180、r=1190,dpad=1700;

181、r=1309,dpad=966;

182、r=1428,dpad=232;

183、r=1547,dpad=1306;

184、r=1666,dpad=572;

185、r=1785,dpad=1646;

186、r=1904,dpad=912;

187、r=2023,dpad=178;

188、r=2142,dpad=1252;

189、r=2261,dpad=518;

190、r=2380,dpad=1592。

191、在一些可能的實施方式中,k=112,n=128,r和dpad滿足如下其中一個條件:r=119,dpad=546;

192、r=238,dpad=1092;

193、r=357,dpad=1638;

194、r=476,dpad=392;

195、r=595,dpad=938;

196、r=714,dpad=1484;

197、r=833,dpad=238;

198、r=952,dpad=784;

199、r=1071,dpad=1330;

200、r=1190,dpad=84;

201、r=1309,dpad=630;

202、r=1428,dpad=1176;

203、r=1547,dpad=1722;

204、r=1666,dpad=476;

205、r=1785,dpad=1022;

206、r=1904,dpad=1568;

207、r=2023,dpad=322;

208、r=2142,dpad=868;

209、r=2261,dpad=1414;

210、r=2380,dpad=168。

211、在一些可能的實施方式中,k=110,n=126,r和dpad滿足如下其中一個條件:r=119,dpad=1154;

212、r=238,dpad548;

213、r=357,dpad=1702;

214、r=476,dpad=1096;

215、r=595,dpad=490;

216、r=714,dpad=1644;

217、r=833,dpad=1038;

218、r=952,dpad=432;

219、r=1071,dpad=1586;

220、r=1190,dpad=980;

221、r=1309,dpad=374;

222、r=1428,dpad=1528;

223、r=1547,dpad=922;

224、r=1666,dpad=316;

225、r=1785,dpad=1470;

226、r=1904,dpad=864;

227、r=2023,dpad=258;

228、r=2142,dpad=1412;

229、r=2261,dpad=806;

230、r=2380,dpad=200。

231、在一些可能的實施方式中,k=119,n=136,r和dpad滿足如下其中一個條件:

232、r=119,dpad=1666;

233、r=238,dpad=1428;

234、r=357,dpad=1190;

235、r=476,dpad=952;

236、r=595,dpad=714;

237、r=714,dpad=476;

238、r=833,dpad=238;

239、r=952,dpad=1904;

240、r=1071,dpad=1666;

241、r=1190,dpad=1428;

242、r=1309,dpad=1190;

243、r=1428,dpad=952;

244、r=1547,dpad=714;

245、r=1666,dpad=476;

246、r=1785,dpad=238;

247、r=1904,dpad=0;

248、r=2023,dpad=1666;

249、r=2142,dpad=1428;

250、r=2261,dpad=1190;

251、r=2380,dpad=952。

252、在一些可能的實施方式中,k=119,n=135,r和dpad滿足如下其中一個條件:

253、r=119,dpad=1666;

254、r=238,dpad=1428;

255、r=357,dpad=1190;

256、r=476,dpad=952;

257、r=595,dpad=714;

258、r=714,dpad=476;

259、r=833,dpad=238;

260、r=952,dpad=1904;

261、r=1071,dpad=1666;

262、r=1190,dpad=1428;

263、r=1309,dpad=1190;

264、r=1428,dpad=952;

265、r=1547,dpad=714;

266、r=1666,dpad=476;

267、r=1785,dpad=238;

268、r=1904,dpad=0;

269、r=2023,dpad=1666;

270、r=2142,dpad=1428;

271、r=2261,dpad=1190;

272、r=2380,dpad=952。

273、第三方面,本技術實施例提供了一種數據處理裝置,該數據處理裝置包括處理器。處理器用于執行如下操作。首先,獲取第一比特集合,其中,第一比特集合包括d1個比特,d1=244664×l,l為正整數。之后,對所述第一比特集合進行第一前向糾錯(forward?errorcorrection,fec)編碼得到第二比特集合,其中,所述第二比特集合包括d2個比特,所述第一比特集合中的每244664個比特經過所述第一fec編碼得到所述第二比特集合中的每261086個比特,d2=261086×l。接下來,對所述第二比特集合添加dpad個填充比特得到第三比特集合,dpad為大于或等于0的整數。進而,對所述第三比特集合進行第二fec編碼得到第四比特集合。

274、在該實施方式中,是以244664個比特為粒度進行第一fec編碼(外碼編碼),獲取第一比特集合中的比特個數d1=244664×l也是244664的倍數,使得具有更好的實現效果,便于硬件實現,復雜度更低。在此基礎上,通過采用增益更高的內碼編碼提升了級聯編碼的性能,同時,通過設計具體的數據處理方法,使得更好地兼容dp-16qam和dp-qpsk調制,有利于應用在未來采用dp-16qam的1.6t-zr的場景和采用dp-qpsk的800g等高波特率長距離傳輸場景。

275、在一些可能的實施方式中,所述第一比特集合中的d1個比特分布為r行2056列,r=119×l,待編碼的比特采用行列分布的比特矩陣具有較好的實用效果。采用2056列分布,比現有的10280列更小,更有利于未來方案的擴展。

276、在一些可能的實施方式中,所述第二比特集合中的每261086個比特分布為119行2194列,所述2194列中的前2056列用于承載所述第一比特集合中的244664個比特。由于每119行中的前2056列總共2056×119=244664個比特剛好承載外碼編碼中的244664個載荷比特,因此,這種處理方法具有更好的數據匹配性,使得硬件實現簡單,復雜度較低。

277、在一些可能的實施方式中,所述第二比特集合中的每261086個比特包括所述第一比特集合中的244664個比特、所述32個第一類型比特、所述6個第二類型比特和16384個第一fec編碼的校驗比特。在一些具體應用中,32個第一類型比特是通過將244664個載荷(payload)比特進行crc獲得。典型的,crc采用crc-32校驗。在另一些具體應用中,32個第一類型比特是32個保留比特,簡稱為res。6個第二類型比特是mbas。

278、在一些可能的實施方式中,對所述第二比特集合添加dpad個填充比特得到第三比特集合之后,對所述第三比特集合進行第二fec編碼得到第四比特集合之前,所述處理器還用于:對所述第三比特集合進行第一交織。可以減小內碼編碼與外碼編碼之間錯誤相關性的傳遞,更有效的抵抗突發錯誤。

279、在一些可能的實施方式中,處理器具體用于:根據p條延遲線對來自所述第三比特集合中的比特進行延遲。所述p為大于1的整數,每條延遲線包括的存儲單元數量各不相同,存儲單元數量最小的延遲線包括0個存儲單元,每相鄰兩條延遲線的存儲單元數量的差值為q。每個存儲單元用于存儲d個比特,輸入的比特按照所述p條延遲線的序號依次輸入所述p條延遲線,每條延遲線單次輸入d個比特且單次輸出d個比特,經過卷積交織后輸出的連續p×d個比特包括每條延遲線輸出的d個比特,q和d均為大于或等于1的整數。該實施方式提供了一種第一交織的具體實現方式,即采用卷積交織的方式實現,具有較好的實用效果。

280、在一些可能的實施方式中,所述第四比特集合包括r個碼字,每個所述碼字的長度為n個比特,所述每個碼字包括k個信息比特,r、n和k均為大于1的整數,n大于k,所述第三比特集合包括r×k個比特,r×k=261086×l+dpad,k是d的整數倍,p×d是k的整數倍,是p的整數倍。該實施方式中,第三比特集合的長度是內碼編碼的信息比特長度k的整數倍,便于內碼同步后快速進行外碼同步,使得硬件實現簡單,復雜度較低。

281、在一些可能的實施方式中,所述第一交織后的第三比特集合包括r行k列個比特,所述第一交織后的第三比特集合中每行的k個比特為條延遲線輸出的k個比特。對第三比特集合進行第二fec編碼得到第四比特集合包括:對所述第一交織后的第三比特集合中每行的k個比特進行所述第二fec編碼得到所述第四比特集合中每個所述碼字的n個比特。采用此種方式,在對第三比特集合中的數據進行卷積交織前,卷積交織器輸入和輸出的開關初始化到延遲線0,當第三比特集合中的數據全部輸入卷積交織器后,卷積交織器的輸入和輸出的開關重新回到延遲線0,此便于收端進行解卷積交織器的同步,使得硬件實現簡單。典型的,所述k=d,r是p的整數倍,使得數據處理流程更簡單,硬件實現復雜度低。

282、在一些可能的實施方式中,所述第二fec編碼采用bch編碼或擴展bch編碼,提升了級聯編碼的性能。

283、在一些可能的實施方式中,對所述第二比特集合添加dpad個填充比特得到第三比特集合之后,對所述第三比特集合進行第二fec編碼得到第四比特集合之前,處理器還用于:對所述第三比特集合進行加擾。使得加擾后的比特數據中0和1更趨向于等概率,使得直流平衡,利于收端接收。

284、在一些可能的實施方式中,對所述第三比特集合進行第二fec編碼得到第四比特集合之后,處理器還用于:對所述第四比特集合進行數據處理。所述數據處理包括符號映射、第二交織、偏振劃分和成幀處理。其中,數據處理裝置還包括接口電路,接口電路用于發送對第四比特集合進行數據處理后得到的數據幀。

285、在一些可能的實施方式中,所述第四比特集合包括r個碼字,每個所述碼字的長度為n個比特,所述每個碼字包括k個信息比特,r、n和k均為大于1的整數,n大于k。k=113,n=127,或者,k=113,n=128,或者,k=112,n=128,或者,k=110,n=126,或者,k=119,n=136,或者,k=119,n=135。該實施方式提供的幾種內碼編碼方案,采用的有限域的階數較低,便于硬件實現。

286、在一些可能的實施方式中,k=113,n=127,r和dpad滿足如下其中一個條件:

287、r=119,dpad=1074;

288、r=238,dpad=340;

289、r=357,dpad=1414;

290、r=476,dpad=680;

291、r=595,dpad=1754;

292、r=714,dpad=1020;

293、r=833,dpad=286;

294、r=952,dpad=1360;

295、r=1071,dpad=626;

296、r=1190,dpad=1700;

297、r=1309,dpad=966;

298、r=1428,dpad=232;

299、r=1547,dpad=1306;

300、r=1666,dpad=572;

301、r=1785,dpad=1646;

302、r=1904,dpad=912;

303、r=2023,dpad=178;

304、r=2142,dpad=1252;

305、r=2261,dpad=518;

306、r=2380,dpad=1592。

307、在一些可能的實施方式中,k=113,n=128,r和dpad滿足如下其中一個條件:

308、r=119,dpad=1074;

309、r=238,dpad=340;

310、r=357,dpad=1414;

311、r=476,dpad=680;

312、r=595,dpad=1754;

313、r=714,dpad=1020;

314、r=833,dpad=286;

315、r=952,dpad=1360;

316、r=1071,dpad=626;

317、r=1190,dpad=1700;

318、r=1309,dpad=966;

319、r=1428,dpad=232;

320、r=1547,dpad=1306;

321、r=1666,dpad=572;

322、r=1785,dpad=1646;

323、r=1904,dpad=912;

324、r=2023,dpad=178;

325、r=2142,dpad=1252;

326、r=2261,dpad=518;

327、r=2380,dpad=1592。

328、在一些可能的實施方式中,k=112,n=128,r和dpad滿足如下其中一個條件:r=119,dpad=546;

329、r=238,dpad=1092;

330、r=357,dpad=1638;

331、r=476,dpad=392;

332、r=595,dpad=938;

333、r=714,dpad=1484;

334、r=833,dpad=238;

335、r=952,dpad=784;

336、r=1071,dpad=1330;

337、r=1190,dpad=84;

338、r=1309,dpad=630;

339、r=1428,dpad=1176;

340、r=1547,dpad=1722;

341、r=1666,dpad=476;

342、r=1785,dpad=1022;

343、r=1904,dpad=1568;

344、r=2023,dpad=322;

345、r=2142,dpad=868;

346、r=2261,dpad=1414;

347、r=2380,dpad=168。

348、在一些可能的實施方式中,k=110,n=126,r和dpad滿足如下其中一個條件:r=119,dpad=1154;

349、r=238,dpad548;

350、r=357,dpad=1702;

351、r=476,dpad=1096;

352、r=595,dpad=490;

353、r=714,dpad=1644;

354、r=833,dpad=1038;

355、r=952,dpad=432;

356、r=1071,dpad=1586;

357、r=1190,dpad=980;

358、r=1309,dpad=374;

359、r=1428,dpad=1528;

360、r=1547,dpad=922;

361、r=1666,dpad=316;

362、r=1785,dpad=1470;

363、r=1904,dpad=864;

364、r=2023,dpad=258;

365、r=2142,dpad=1412;

366、r=2261,dpad=806;

367、r=2380,dpad=200。

368、在一些可能的實施方式中,k=119,n=136,r和dpad滿足如下其中一個條件:r=119,dpad=1666;

369、r=238,dpad=1428;

370、r=357,dpad=1190;

371、r=476,dpad=952;

372、r=595,dpad=714;

373、r=714,dpad=476;

374、r=833,dpad=238;

375、r=952,dpad=1904;

376、r=1071,dpad=1666;

377、r=1190,dpad=1428;

378、r=1309,dpad=1190;

379、r=1428,dpad=952;

380、r=1547,dpad=714;

381、r=1666,dpad=476;

382、r=1785,dpad=238;

383、r=1904,dpad=0;

384、r=2023,dpad=1666;

385、r=2142,dpad=1428;

386、r=2261,dpad=1190;

387、r=2380,dpad=952。

388、在一些可能的實施方式中,k=119,n=135,r和dpad滿足如下其中一個條件:

389、r=119,dpad=1666;

390、r=238,dpad=1428;

391、r=357,dpad=1190;

392、r=476,dpad=952;

393、r=595,dpad=714;

394、r=714,dpad=476;

395、r=833,dpad=238;

396、r=952,dpad=1904;

397、r=1071,dpad=1666;

398、r=1190,dpad=1428;

399、r=1309,dpad=1190;

400、r=1428,dpad=952;

401、r=1547,dpad=714;

402、r=1666,dpad=476;

403、r=1785,dpad=238;

404、r=1904,dpad=0;

405、r=2023,dpad=1666;

406、r=2142,dpad=1428;

407、r=2261,dpad=1190;

408、r=2380,dpad=952。

409、第四方面,本技術實施例提供了一種光模塊,該光模塊包括處理器,處理器用于執行如第一方面任一實施方式介紹的方法。

410、在一些可能的實施方式中,光模塊還包括接口電路,處理器對第四比特集合進行包括符號映射、第二交織、偏振劃分和成幀處理的數據處理得到數據幀,再通過接口電路發送數據幀。

411、第五方面,本技術實施例提供了一種芯片,該芯片包括處理器,處理器用于執行如第一方面任一實施方式介紹的方法。

412、第六方面,本技術實施例提供了一種數據傳輸系統,該數據傳輸系統包括數據發送設備和數據接收設備,其中,數據發送設備用于執行如第一方面任一實施方式介紹的方法并將數據發送至數據接收設備,數據接收設備用于對接收到的數據進行譯碼等操作。

413、第七方面,本技術實施例提供了一種計算機可讀存儲介質,計算機可讀存儲介質上存儲有計算機程序,計算機程序被計算機執行時,以使得實現如第一方面任一實施方式介紹的方法。

414、從以上技術方案可以看出,本技術實施例具有以下優點:

415、在該實施方式中,是以244664個比特為粒度進行第一fec編碼(外碼編碼),獲取第一比特集合中的比特個數d1=244664×l也是244664的倍數,使得具有更好的實現效果,便于硬件實現,復雜度更低。在此基礎上,通過采用增益更高的內碼編碼提升了級聯編碼的性能,同時,通過設計具體的數據處理方法,使得更好地兼容dp-16qam和dp-qpsk調制,有利于應用在未來采用dp-16qam的1.6t-zr的場景和采用dp-qpsk的800g等高波特率長距離傳輸場景。

- 還沒有人留言評論。精彩留言會獲得點贊!