移位寄存器、柵極驅動電路及顯示裝置的制作方法

本公開屬于顯示,具體涉及一種移位寄存器、柵極驅動電路及顯示裝置。

背景技術:

1、隨著顯示技術的不斷發展,近些年的顯示器發展逐漸呈現出了高集成度,低成本的發展趨勢。其中一項非常重要的技術就是goa(gate?driver?on?array,陣列基板行驅動)技術的量產化的實現。利用goa技術將tft(thin?film?transistor,薄膜場效應晶體管)柵極開關電路集成在顯示面板的陣列基板上以形成對顯示面板的掃描驅動,從而可以省掉柵極驅動集成電路部分,其不僅可以從材料成本和制作工藝兩方面降低產品成本,而且顯示面板可以做到兩邊對稱和窄邊框的美觀設計。同時由于可以省去gate方向綁定bonding的工藝,對產能和良率提升也較有利。這種利用goa技術集成在陣列基板上的柵極開關電路也稱為goa電路或移位寄存器電路。

技術實現思路

1、本發明旨在至少解決現有技術中存在的技術問題之一,提供一種移位寄存器、柵極驅動電路及顯示裝置。

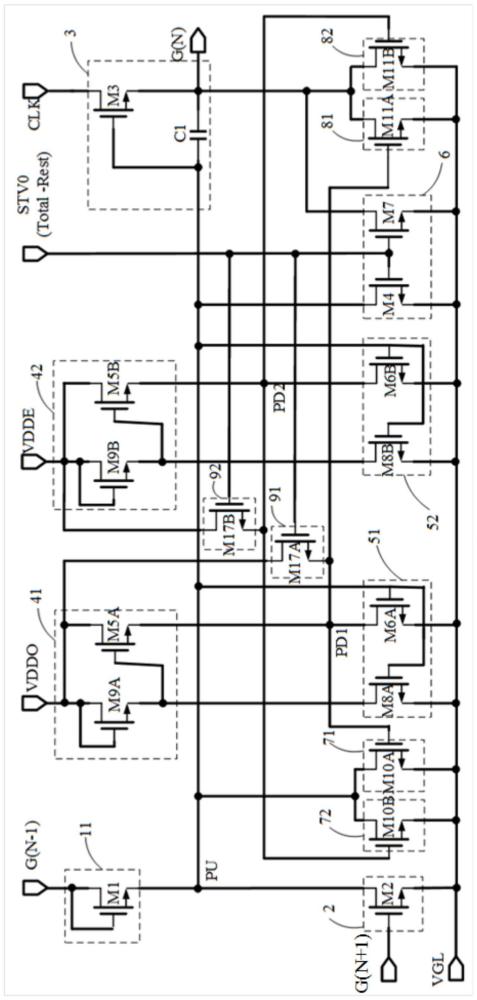

2、本公開實施例提供一種移位寄存器,其包括:第一輸入子電路、輸出子電路、第一下拉控制子電路、第二下拉控制子電路、第一下拉子電路和第二下拉子電路;

3、所述第一輸入子電路,被配置為響應于第一輸入信號,通過第一掃描信號對上拉節點進行預充電;

4、所述輸出子電路,被配置為響應于所述上拉節點的電位,將時鐘信號通過信號輸出端輸出;

5、所述第一下拉控制子電路,被配置為響應于第一電源電壓,并通過所述第一電源電壓控制第一下拉節點的電位;

6、所述第二下拉控制子電路,被配置為響應于第二電源電壓,并通過第二電源電壓控制第二下拉節點的電位;

7、第一下拉子電路,響應于所述上拉節點的電位,對所述第一下拉節點進行下拉;

8、所述第二下拉子電路,響應于所述上拉節點的電位,對所述第二下拉節點進行下拉;其中,

9、所述移位寄存器還包括:第一輔助子電路和第二輔助子電路;

10、所述第一輔助子電路,被配置為在第二電源電壓為工作電平信號時,將第一下拉節點的電位下拉至非工作電平信號;

11、所述第二輔助子電路,被配置為在所述第一電源電壓為工作電平信號,將第二下拉節點的電位下拉至非工作電平信號。

12、其中,所述移位寄存器還包括全局復位子電路,被配置為響應于全局復位信號,通過非工作電平信號對所述上拉節點和所述信號輸出端的輸出進行全局復位。

13、其中,所述第一輔助子電路,具體被配置為響應于所述全局復位信號,在第二電源電壓為工作電平信號時,通過第一電源電壓將非工作電平信號;

14、所述第二輔助子電路,具體被配置為響應于所述全局復位信號,在第一電源電壓為工作電平信號時,通過第二電源電壓將第二下拉節點的電位下拉至非工作電平信號。

15、其中,所述第一輔助子電路和第二輔助子電路均包括第十七晶體管;

16、所述第一輔助子電路中的第十七晶體管的第一極連接第一電源電壓端,第二極連接所述第一下拉節點,控制極連接全局復位信號端;

17、所述第二輔助子電路中的第十七晶體管的第一極連接第二電源電壓端,第二極連接所述第二下拉節點,控制極連接所述全局復位信號端。

18、其中,所述全局復位子電路包括第四晶體管和第七晶體管;

19、所述第四晶體管的第一極連接所述上拉節點,第二極連接非工作電平信號端,控制極連接全局復位信號端;

20、所述第七晶體管的第一極連接所述信號輸出端,第二極連接非工作電平信號端,控制極連接全局復位信號端。

21、其中,所述第一輔助子電路,具體被配置為在第二電源電壓為工作電平信號時,響應于幀開啟信號,通過第一電源電壓將第一下拉節點下拉至非工作電壓;

22、所述第二輔助子電路,具體被配置為在第一電源電壓為工作電平信號時,響應于幀開啟信號,通過第二電源電壓將第二下拉節點下拉至非工作電壓。

23、其中,所述第一輔助子電路和第二輔助子電路均包括第十七晶體管;

24、所述第一輔助子電路中的第十七晶體管的第一極連接第一電源電壓端,第二極連接所述第一下拉節點,控制極連接幀開啟信號端;

25、所述第二輔助子電路中的第十七晶體管的第一極連接第二電源電壓端,第二極連接所述第二下拉節點,控制極連接所述幀開啟信號端。

26、其中,所述第一輔助子電路,具體被配置為在第二電源電壓為工作電平信號時,響應于所述第二電源電壓,通過非工作電平信號下拉所述第一下拉節點;

27、所述第二輔助子電路,具體被配置為在第一電源電壓為工作電平信號時,響應于所述第一電源電壓,通過非工作電平信號下拉所述第二下拉節點。

28、其中,所述第一輔助子電路和第二輔助子電路均包括第十七晶體管;

29、所述第一輔助子電路中的第十七晶體管的第一極連接所述第一下拉節點,第二極連接非工作電平信號端,控制極連接第二電源電壓端;

30、所述第二輔助子電路中的第十七晶體管的第一極連接第二下拉節點,第二極連接非工作電平信號端,控制極連接第一電源電壓端。

31、其中,所述第一輔助子電路,具體被配置為在第二電源電壓為工作電平信號時,響應于所述第二下拉節點的電位,通過非工作電平信號下拉所述第一下拉節點的電位;

32、所述第二輔助子電路,具體被配置為在第一電源電壓為工作電平信號時,響應于所述第一下拉節點的電位,通過非工作電平信號下拉所述第二下拉節點的電位。

33、其中,所述第一輔助子電路和第二輔助子電路均包括第十七晶體管;

34、所述第一輔助子電路中的第十七晶體管的第一極連接所述第一下拉節點,第二極連接非工作電平信號端,控制極連接所述第二下拉節點;

35、所述第二輔助子電路中的第十七晶體管的第一極連接第二下拉節點,第二極連接非工作電平信號端,控制極連接所述第一下拉節點。

36、其中,所述移位寄存器還包括上拉復位子電路,被配置為響應于上拉復位信號,通過非工作電平信號對所述上拉節點的輸出進行復位。

37、其中,所述上拉復位子電路包括第二晶體管,所述第二晶體管的第一極連接所述上拉節點,第二極連接非工作電平信號端,控制極連接上拉復位信號端。

38、其中,所述第一輸入信號復用為所述第一掃描信號;所述第一輸入子電路包括第一晶體管;

39、所述第一晶體管的第一極和控制極連接所述第一輸入信號端,第二極連接所述上拉節點。

40、其中,所述移位寄存器還包括第二輸入子電路,被配置為響應于第二輸入信號,通過第二掃描信號對所述上拉節點進行預充電。

41、其中,所述第二輸入子電路包括第二晶體管;

42、所述第二晶體管的第一極連接所述上拉節點,第二極連接第二掃描信號端,控制極連接第二輸入信號端。

43、其中,所述第一輸入子電路包括第一晶體管;

44、所述第一晶體管的第一極連接第一掃描信號端,第二極連接所述上拉節點,控制極連接第一輸入信號端。

45、其中,所述移位寄存器還包括兩個第一降噪子電路和兩個第二降噪子電路;

46、所述兩個第一降噪子電路中的一者被配置響應于所述第一下拉節點的電位,通過非工作電平信號對所述上拉節點的輸出進行降噪,另一者被配置響應于所述第二下拉節點的電位,通過非工作電平信號對所述上拉節點的輸出進行降噪;

47、所述兩個第二降噪子電路中的一者被配置響應于所述第一下拉節點的電位,通過非工作電平信號對所述信號輸出端的輸出進行降噪,另一者被配置響應于所述第二下拉節點的電位,通過非工作電平信號對所述信號輸出端的輸出進行降噪。

48、其中,所述兩個第一降噪子電路均包括第十晶體管;

49、其中一個所述第一降噪子電路中的第十晶體管的第一極連接所述上拉節點,第二極連接非工作電壓端,控制極連接所述第一下拉節點;另一個所述第一降噪子電路中的第十晶體管的第一極連接所述上拉節點,第二極連接非工作電壓端,控制極連接所述第二下拉節點。

50、其中,所述兩個第二降噪子電路均包括第十一晶體管;

51、其中一個所述第二降噪子電路中的第十一晶體管的第一極連接所述信號輸出端,第二極連接非工作電壓端,控制極連接所述第一下拉節點;另一個所述第二降噪子電路中的第十一晶體管的第一極連接所述上拉節點,第二極連接非工作電壓端,控制極連接所述信號輸出端。

52、其中,所述移位寄存器還包括級聯子電路,被配置為響應于所述上拉節點的電位,將時鐘信號通過級聯信號端進行輸出。

53、其中,所述級聯子電路包括第十三晶體管;

54、所述第十三晶體管的第一極連接時鐘信號端,第二極連接級聯信號端,控制極連接所述上拉節點。

55、其中,所述移位寄存器還包括兩個第三降噪子電路;

56、所述兩個第三降噪子電路中的一者被配置為響應于所述第一下拉節點的控制下,通過非工作電平信號對所述級聯信號端的輸出進行降噪;另一者被配置為響應于所述第二下拉節點的控制下,通過非工作電平信號對所述級聯信號端的輸出進行降噪。

57、其中,所述第一下拉控制子電路和第二下拉控制子電路均包括第五晶體管和第九晶體管;

58、對于所述第一下拉控制子電路,其中的所述第五晶體管的第一極連接第九晶體管的第一極、第九晶體管的控制極和第一電源電壓端,第二極連接所述第一下拉節點;

59、對于第二下拉控制子電路,其中的所述第五晶體管的第一極連接第九晶體管的第一極、第九晶體管的控制極和第二電源電壓端,第二極連接所述第二下拉節點。

60、其中,所述第一下拉子電路和所述第二下拉子電路均包括第六晶體管和第八晶體管;

61、對于第一下拉子電路,其中的所述第六晶體管的第一極連接所述第一下拉節點,第二極連接所述非工作電平信號端,控制極連接所述上拉節點;所述第八晶體管的第一極連接所述第五晶體管的控制極和所述第九晶體管的第一極,第二極連接所述非工作電平信號端,控制極連接所述上拉節點;

62、對于第二下拉子電路,其中的所述第六晶體管的第一極連接所述第二下拉節點,第二極連接所述非工作電平信號端,控制極連接所述上拉節點;所述第八晶體管的第一極連接所述第五晶體管的控制極和所述第九晶體管的第一極,第二極連接所述非工作電平信號端,控制極連接所述上拉節點。

63、其中,所述第一下拉控制子電路和第二下拉控制子電路均包括第五晶體管;

64、對于第一下拉控制子電路,其中的第五晶體管的第一極和控制極連接第一電源電壓端,第二極連接所述第一下拉節點;

65、對于第一下拉控制子電路,其中的第五晶體管的第一極和控制極連接第二電源電壓端,第二極連接所述第二下拉節點。

66、其中,所述第一下拉子電路和所述第二下拉子電路均包括第六晶體管;

67、所述第六晶體管的第一極連接所述第一下拉節點,第二極連接所述非工作電平信號端,控制極連接所述上拉節點;

68、所述第六晶體管的第一極連接所述第二下拉節點,第二極連接所述非工作電平信號端,控制極連接所述上拉節點。

69、本公開實施例提供一種柵極驅動電路,其包括多個級聯的移位寄存器,所述移位寄存器采用上述任一所述的移位寄存器。

70、本公開實施例提供一種顯示裝置,其包括上述的柵極驅動電路。

- 還沒有人留言評論。精彩留言會獲得點贊!