顯示基板及顯示裝置的制作方法

本文涉及但不限于顯示,尤指一種顯示基板及顯示裝置。

背景技術:

1、有機發光二極管(oled,organic?light?emitting?diode)和量子點發光二極管(qled,quantum-dot?light?emitting?diode)為主動發光顯示器件,具有自發光、廣視角、高對比度、低耗電、極高反應速度、輕薄、可彎曲和成本低等優點。

技術實現思路

1、以下是對本文詳細描述的主題的概述。本概述并非是為了限制權利要求的保護范圍。

2、本實施例提供一種顯示基板及顯示裝置。

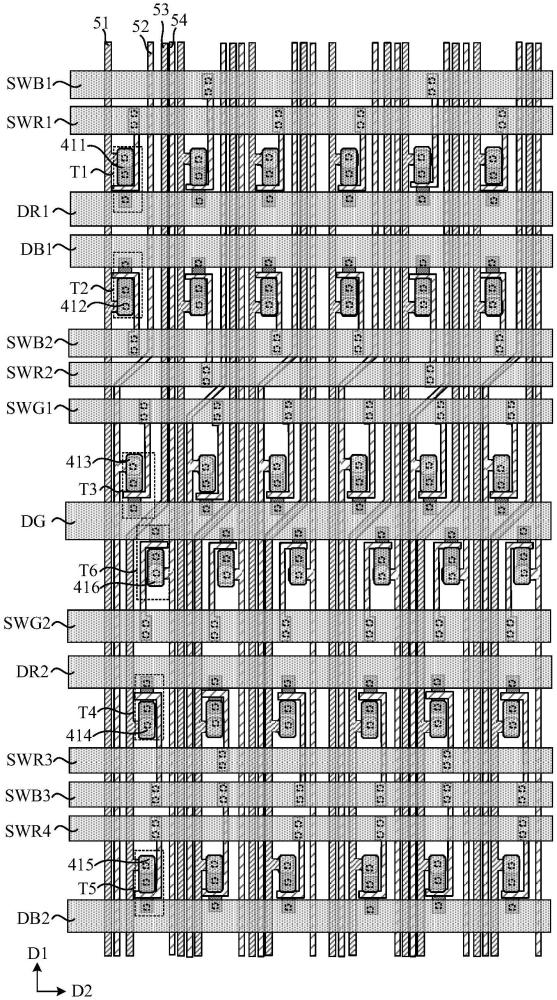

3、一方面,本實施例提供一種顯示基板,包括:襯底、多個像素單元、多條數據線、多條數據引出線和多個第一類測試電路組。襯底包括:顯示區域和沿第一方向位于所述顯示區域一側的第一邊框區域。多個像素單元和多條數據線設置在所述襯底上且位于所述顯示區域,所述多個像素單元與所述多條數據線電連接,所述像素單元包括多個子像素。多條數據引出線位于所述第一邊框區域,所述多條數據引出線與所述多條數據線電連接。多個第一類測試電路組位于所述第一邊框區域并與所述多條數據引出線連接。所述多個第一類測試電路組中的至少一個第一類測試電路組包括沿所述第一方向排布的至少一個第一類測試電路;所述第一類測試電路包括沿所述第一方向排布的多個晶體管,所述第一類測試電路配置為給一列像素單元提供第一類測試數據信號,所述一列像素單元包括沿所述第一方向排布的多個像素單元。

4、在一些示例性實施方式中,所述像素單元的多個子像素包括:一個出射第一顏色光的第一子像素、一個出射第二顏色光的第二子像素、以及兩個出射第三顏色光的第三子像素。所述第一類測試電路包括:第一測試電路、第二測試電路、第三測試電路和第四測試電路;所述第一測試電路、所述第二測試電路、所述第三測試電路和所述第四測試電路各自包括至少一個晶體管。所述第一測試電路配置為在第一時段給所述一列像素單元中的第e行像素單元的第一子像素提供第一類測試數據信號,在第二時段給所述一列像素單元中的第e+1行像素單元的第二子像素提供第一類測試數據信號;所述第二測試電路配置為給所述一列像素單元中的一列第三子像素提供第一類測試數據信號;所述第三測試電路配置為在所述第一時段給所述一列像素單元中的第e+1行像素單元的第一子像素提供第一類測試數據信號,在所述第二時段給所述一列像素單元中的第e行像素單元的第二子像素提供第一類測試數據信號;其中,e為正整數;所述第四測試電路配置為給所述一列像素單元中的另一列第三子像素提供第一類測試數據信號。

5、在一些示例性實施方式中,所述至少一個第一類測試電路組的所述第一測試電路、所述第二測試電路、所述第四測試電路和所述第三測試電路沿所述第一方向依次排布。

6、在一些示例性實施方式中,所述顯示基板還包括:位于所述第一邊框區域的多條第一測試控制線、多條第二測試控制線、多條第三測試控制線、多條第一測試數據線、多條第二測試數據線和至少一條第三測試數據線。所述第一測試電路包括:至少一個第一測試晶體管和至少一個第二測試晶體管,所述至少一個第一測試晶體管的柵極與所述多條第一測試控制線中的一條第一測試控制線連接,所述至少一個第一測試晶體管的第一極與所述多條第一測試數據線中的一條第一測試數據線連接,所述至少一個第二測試晶體管的柵極與所述多條第二測試控制線中的一條第二測試控制線連接,所述至少一個第二測試晶體管的第一極與所述多條第二測試數據線中的一條第二測試數據線連接,所述至少一個第一測試晶體管的第二極和所述至少一個第二測試晶體管的第二極與所述多條數據引出線中的同一條數據引出線連接。所述第二測試電路包括:至少一個第三測試晶體管,所述至少一個第三測試晶體管的柵極與所述多條第三測試控制線中的一條第三測試控制線連接,所述至少一個第三測試晶體管的第一極與所述至少一條第三測試數據線連接,所述至少一個第三測試晶體管的第二極與所述多條數據引出線中的一條數據引出線連接。所述第三測試電路包括:至少一個第四測試晶體管和至少一個第五測試晶體管,所述至少一個第四測試晶體管的柵極與所述多條第二測試控制線中的另一條第二測試控制線連接,所述至少一個第四測試晶體管的第一極與所述多條第一測試數據線中的另一條第一測試數據線連接,所述至少一個第五測試晶體管的柵極與所述多條第一測試控制線中的另一條第一測試控制線連接,所述至少一個第五測試晶體管的第一極與所述多條第二測試數據線中的另一條第二測試數據線連接,所述至少一個第四測試晶體管的第二極和所述至少一個第五測試晶體管的第二極與所述多條數據引出線中的同一條數據引出線連接;所述第四測試電路包括:至少一個第六測試晶體管,所述至少一個第六測試晶體管的柵極與所述多條第三測試控制線中的另一條第三測試控制線連接,所述至少一個第六測試晶體管的第一極與所述至少一條第三測試數據線連接,所述第六測試晶體管的第二極與所述多條數據引出線中的一條數據引出線連接;所述第一測試電路、所述第二測試電路、所述第三測試電路和所述第四測試電路所連接的數據引出線不同。

7、在一些示例性實施方式中,所述顯示基板包括:四條第一測試控制線、三條第二測試控制線、兩條第三測試控制線、兩條第一測試數據線、兩條第二測試數據線和一條第三測試數據線;第一條第二測試控制線、第一條第一測試控制線、第一條第一測試數據線、第一條第二測試數據線、第二條第二測試控制線、第二條第一測試控制線、第一條第三測試控制線、所述第三測試數據線、第二條第三測試控制線、第二條第一測試數據線、第三條第一測試控制線、第三條第二測試控制線、第四條第一測試控制線和第二條第二測試數據線沿所述第一方向依次排布;所述至少一個第一類測試電路組的第一類測試電路包括:一個第一測試晶體管、一個第二測試晶體管、一個第三測試晶體管、一個第四測試晶體管、一個第五測試晶體管和一個第六測試晶體管;所述第一測試晶體管與所述第一條第一測試控制線和所述第一條第一測試數據線連接,且在所述第一方向上位于所述第一條第一測試控制線和所述第一條第一測試數據線之間;所述第二測試晶體管與所述第一條第二測試數據線和所述第二條第二測試控制線連接,且在所述第一方向上位于所述第一條第二測試數據線和所述第二條第二測試控制線之間;所述第三測試晶體管與所述第一條第三測試控制線和所述第三測試數據線連接,且在所述第一方向上位于所述第一條第三測試控制線和所述第三測試數據線之間;所述第四測試晶體管與所述第二條第一測試數據線和所述第三條第二測試控制線連接,且在所述第一方向上位于所述第二條第一測試數據線和所述第三條第一測試控制線之間;所述第五測試晶體管與所述第四條第一測試控制線和所述第二條第二測試數據線連接,且在所述第一方向上位于所述第四條第一測試控制線和所述第二條第二測試數據線之間。

8、在一些示例性實施方式中,所述顯示基板包括:兩條第一測試控制線、四條第二測試控制線、兩條第三測試控制線、四條第一測試數據線、四條第二測試數據線和三條第三測試數據線;第一條第二測試控制線、第一條第一測試數據線、第二條第一測試數據線、第一條第一測試控制線、第二條第二測試控制線、第一條第二測試數據線、第二條第二測試數據線、第一條第三測試控制線、第一條第三測試數據線、第二條第三測試數據線、第三條第三測試數據線、第二條第三測試控制線、第三條第二測試控制線、第三條第一測試數據線、第四條第一測試數據線、第二條第一測試控制線、第四條第二測試控制線、第三條第二測試數據線和第四條第二測試數據線沿所述第一方向依次排布;所述至少一個第一類測試電路組的第一類測試電路包括:兩個第一測試晶體管、兩個第二測試晶體管、兩個第三測試晶體管、兩個第四測試晶體管、兩個第五測試晶體管以及兩個第六測試晶體管;所述兩個第一測試晶體管在所述第一方向上位于所述第一條第一測試數據線和所述第二條第一測試數據線之間;所述兩個第二測試晶體管在所述第一方向上位于所述第一條第二測試數據線和所述第二條第二測試數據線之間;所述兩個第三測試晶體管在所述第一方向上位于所述第一條第三測試數據線和所述第二條第三測試數據線之間;所述兩個第六測試晶體管在所述第一方向上位于所述第二條第三測試數據線和所述第三條第三測試數據線之間;所述兩個第四測試晶體管在所述第一方向上位于所述第三條第一測試數據線和所述第四條第一測試數據線之間;所述兩個第五測試晶體管在所述第一方向上位于所述第三條第二測試數據線和所述第四條第二測試數據線之間。

9、在一些示例性實施方式中,所述第一類測試電路的第一個第一測試晶體管與所述第一條第一測試數據線和所述第一條第一測試控制線連接,第二個第一測試晶體管與所述第二條第一測試數據線和所述第一條第一測試控制線連接;第一個第二測試晶體管與所述第一條第二測試數據線和所述第二條第二測試控制線連接,第二個第二測試晶體管與所述第二條第二測試數據線和所述第二條第二測試控制線連接;第一個第三測試晶體管與所述第一條第三測試數據線和所述第一條第三測試控制線連接,第二個第三測試晶體管與所述第二條第三測試數據線和所述第一條第三測試控制線連接;第一個第六測試晶體管與所述第二條第三測試數據線和所述第二條第三測試控制線連接,第二個第六測試晶體管與所述第三條第三測試數據線和所述第二條第三測試控制線連接;第一個第四測試晶體管與所述第三條第一測試數據線和所述第三條第二測試控制線連接,第二個第四測試晶體管與所述第四條第一測試數據線和所述第三條第二測試控制線連接;第一個第五測試晶體管與所述第三條第二測試數據線和所述第二條第一測試控制線連接,第二個第五測試晶體管與所述第四條第二測試數據線和所述第二條第一測試控制線連接。

10、在一些示例性實施方式中,所述至少一個第一類測試電路組包括沿所述第一方向排布的兩個第一類測試電路,第一個第一類測試電路的第一測試電路、第二測試電路、第四測試電路、第三測試電路沿所述第一方向依次排布,第二個第一類測試電路的第二測試電路、第四測試電路、第一測試電路和第三測試電路沿所述第一方向依次排布。

11、在一些示例性實施方式中,所述顯示基板包括:四條第一測試控制線、四條第二測試控制線、四條第三測試控制線、四條第一測試數據線、四條第二測試數據線和兩條第三測試數據線。第一條第一測試控制線、第一條第一測試數據線、第一條第二測試數據線、第一條第二測試控制線、第一條第三測試控制線、第一條第三測試數據線、第二條第三測試控制線、第二條第二測試控制線、第二條第一測試數據線、第二條第二測試數據線、第二條第一測試控制線、第三條第三測試控制線、第二條第三測試數據線、第四條第三測試控制線、第三條第一測試控制線、第三條第一測試數據線、第三條第二測試數據線、第三條第二測試控制線、第四條第二測試控制線、第四條第一測試數據線、第四條第二測試數據線和第四條第一測試控制線沿所述第一方向依次排布。

12、在一些示例性實施方式中,所述顯示基板還包括:多個第二類測試電路組,所述多個第二類測試電路組中的至少一個第二類測試電路組包括:沿所述第一方向排布的至少一個第二類測試電路,所述第二類測試電路包括沿所述第一方向排布的多個晶體管,所述第二類測試電路配置為給所述一列像素單元提供第二類測試數據信號。

13、在一些示例性實施方式中,所述第二類測試電路包括:第五測試電路、第六測試電路、第七測試電路和第八測試電路。所述一列像素單元包括四列子像素;所述第二類測試電路的所述第五測試電路、所述第六測試電路、所述第七測試電路和所述第八測試電路配置為給所述四列子像素提供第二類測試數據信號;所述第二類測試電路的所述第八測試電路、所述第七測試電路、所述第六測試電路和所述第五測試電路沿所述第一方向依次排布。

14、在一些示例性實施方式中,所述第五測試電路包括:至少一個第七測試晶體管,所述第六測試電路包括:至少一個第八測試晶體管,所述第七測試電路包括:至少一個第九測試晶體管,所述第八測試電路包括:至少一個第十測試晶體管。所述顯示基板還包括:位于所述第一邊框區域的多條第四測試控制線、多條第四測試數據線和多條第五測試數據線。所述第七測試晶體管的柵極和所述第八測試晶體管的柵極與所述多條第四測試控制線中的同一條第四測試控制線連接,所述第七測試晶體管的第一極和所述第八測試晶體管的第一極與所述多條第四測試數據線中的同一條第四測試數據線連接,所述第七測試晶體管的第二極與所述多條數據引出線中的一條數據引出線連接,所述第八測試晶體管的第二極與所述多條數據引出線中的另一條數據引出線連接。所述第九測試晶體管的柵極和所述第十測試晶體管的柵極與所述多條第四測試控制線中的同一條第四測試控制線連接,所述第九測試晶體管的第一極和所述第十測試晶體管的第一極與所述多條第五測試數據線中的同一條第五測試數據線連接,所述第九測試晶體管的第二極與所述多條數據引出線中的另一條數據引出線連接,所述第十測試晶體管的第二極與所述多條數據引出線中的另一條數據引出線連接。

15、在一些示例性實施方式中,所述顯示基板還包括:位于所述第一邊框區域的兩條第一邊框電源線和三條第二邊框電源線,第一條第二邊框電源線和第二條第二邊框電源線位于所述兩條第一邊框電源線和第三條第二邊框電源線的兩側,所述兩條第一邊框電源線位于所述第三條第二邊框電源線的兩側。

16、在一些示例性實施方式中,所述顯示基板還包括:位于所述第一邊框區域的四組初始信號線,第一組初始信號線位于所述第一條第二邊框電源線遠離所述第三條第二邊框電源線的一側,第二組初始信號線位于所述第一條第二邊框電源線靠近所述第三條第二邊框電源線的一側,第三組初始信號線位于所述第二條第二邊框電源線靠近所述第三條第二邊框電源線的一側,第四組初始信號線位于所述第二條第二邊框電源線遠離所述第三條第二邊框電源線的一側。

17、另一方面,本實施例提供一種顯示裝置,包括如前所述的顯示基板。

18、本技術的其它特征和優點將在隨后的說明書中闡述,并且,部分地從說明書中變得明顯的,或者通過實施本技術而了解。本技術的其他優點可通過在說明書以及附圖中所描述的方案來實現和獲得。

- 還沒有人留言評論。精彩留言會獲得點贊!