一種高速雷達信號處理系統的制作方法

本技術涉及雷達集,尤其涉及一種高速雷達信號處理系統。

背景技術:

1、如今的雷達已由單一模式向多模式發展,新的復合雷達功能日趨復雜,數據傳輸量越來越大,對通信速率的要求隨之增高。

2、傳統的雷達傳輸信息的方式多為rs422、1553b、can等總線的形式,通信速率太低,已不能滿足需求。同時武器系統對于全國產化的要求也提上日程,這就要求雷達尋找新的通信方式,高效高速,可靠性高,并實現所有產品自主可控。

技術實現思路

1、鑒于上述的分析,本實用新型旨在提供一種高速雷達信號處理系統,用以解決現有雷達信號處理傳輸效率低的問題。

2、本實用新型的目的主要是通過以下技術方案實現的:

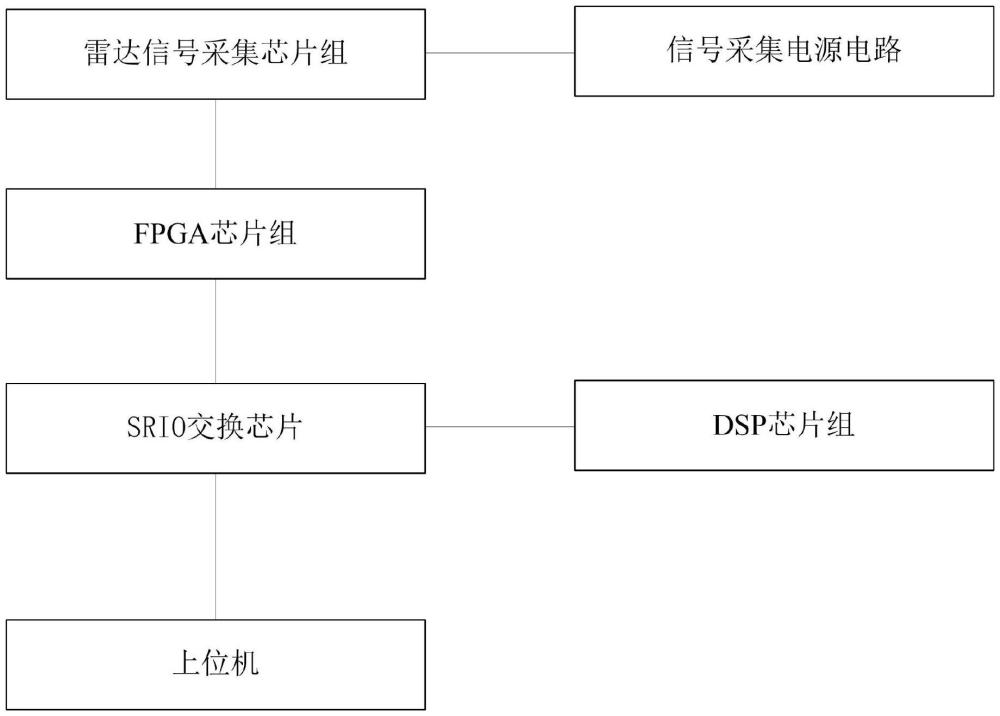

3、一種高速雷達信號處理系統,包括:雷達信號采集芯片組、fpga芯片組、srio交換芯片、dsp芯片組、信號采集電源電路和上位機;

4、所述雷達信號采集芯片組與所述fpga芯片組通信連接;

5、所述fpga芯片組、dsp芯片組和上位機均與所述srio交換芯片通信連接;

6、所述信號采集電源電路為所述雷達信號采集芯片組供電。

7、基于上述系統的進一步改進,所述交換芯片的每個電源引腳均連接一個第一電容;所述第一電容的電容值范圍為0.01uf到0.1uf。

8、基于上述系統的進一步改進,在所述交換芯片的電源引腳中,每隔第一預設值的電源引腳上還連接有第二電容;所述第二電容的電容值為1uf。

9、基于上述系統的進一步改進,在所述交換芯片的電源引腳中,每隔第二預設值的電源引腳上還連接有第三電容;所述第三電容的電容值大于10uf。

10、基于上述系統的進一步改進,所述fpga芯片組、dsp芯片組和上位機與所述srio交換芯片通過mvpx高速板間連接器電連接。

11、基于上述系統的進一步改進,所述srio交換芯片的每個芯片id配置引腳通過第一電阻接地,每個芯片id配置引腳還通過第二電阻連接電源。

12、基于上述系統的進一步改進,所述系統還包括交換芯片的配置芯片,所述配置芯片的io管腳和srio交換芯片的復位引腳、iic配置時鐘引腳、iic配置數據引腳連接。

13、基于上述系統的進一步改進,所述高速雷達信號處理系統還包括時鐘電路;所述時鐘電路包括時鐘芯片和時鐘緩存器,所述時鐘芯片的輸出引腳和時鐘緩存器的輸入引腳連接;每片高速adc轉換器的時鐘引腳均與所述時鐘緩存器的時鐘輸出引腳連接。

14、基于上述系統的進一步改進,所述信號采集電源電路包括4片ldo電源芯片,所述ldo電源芯片包括使能引腳,所述ldo電源芯片的使能引腳en通過電阻r209接地;所述ldo電源芯片的使能引腳en還與fpga芯片的io引腳連接。

15、基于上述系統的進一步改進,所述高速雷達信號處理系統的雷達信號采集芯片組、fpga芯片組、srio交換芯片、dsp芯片組、信號采集電源電路布設在多塊pcb板卡上,所述多塊pcb板卡為層疊結構;

16、所述高速雷達信號處理系統的信號線和數據線所在平面層的相鄰兩側均為接地層;

17、所述雷達信號采集芯片組與fpga芯片組間的信號連線在pcb板上的過孔為背鉆過孔,且去掉非功能焊盤。

18、與現有技術相比,本實用新型通過雷達信號采集芯片組和fpga芯片組實現多通道的雷達信號檢測通過信號采集電源電路為雷達信號采集芯片組供電,提高采集的穩定性和速率,通過srio交換芯片連接fpga芯片組、dsp芯片組和上位機,使得數據傳輸不再通過點對點的方式,而是通過交換芯片實現接口分時復用,從而可以多通道同時進行雷達信號的數據采集、處理,增加了傳輸帶寬,提高了數據采集傳輸效率,并且具有更高的靈活性。

19、本實用新型中,上述各技術方案之間還可以相互組合,以實現更多的優選組合方案。本實用新型的其他特征和優點將在隨后的內容中闡述,并且,部分優點可從說明書中變得顯而易見,或者通過實施本實用新型而了解。本實用新型的目的和其他優點可通過文字以及附圖中所特別指出的內容中來實現和獲得。

技術特征:

1.一種高速雷達信號處理系統,其特征在于,包括:雷達信號采集芯片組、fpga芯片組、srio交換芯片、dsp芯片組、信號采集電源電路和上位機;

2.根據權利要求1所述的高速雷達信號處理系統,其特征在于,所述交換芯片的每個電源引腳均連接一個第一電容;所述第一電容的電容值范圍為0.01uf到0.1uf。

3.根據權利要求2所述的高速雷達信號處理系統,其特征在于,在所述交換芯片的電源引腳中,每隔第一預設值的電源引腳上還連接有第二電容;所述第二電容的電容值為1uf。

4.根據權利要求2所述的高速雷達信號處理系統,其特征在于,在所述交換芯片的電源引腳中,每隔第二預設值的電源引腳上還連接有第三電容;所述第三電容的電容值大于10uf。

5.根據權利要求1所述的高速雷達信號處理系統,其特征在于,所述fpga芯片組、dsp芯片組和上位機與所述srio交換芯片通過mvpx高速板間連接器電連接。

6.根據權利要求1所述的高速雷達信號處理系統,其特征在于,所述srio交換芯片的每個芯片id配置引腳通過第一電阻接地,每個芯片id配置引腳還通過第二電阻連接電源。

7.根據權利要求1所述的高速雷達信號處理系統,其特征在于,所述系統還包括交換芯片的配置芯片,所述配置芯片的io管腳和srio交換芯片的復位引腳、iic配置時鐘引腳、iic配置數據引腳連接。

8.根據權利要求1所述的高速雷達信號處理系統,其特征在于,所述高速雷達信號處理系統還包括時鐘電路;所述時鐘電路包括時鐘芯片和時鐘緩存器,所述時鐘芯片的輸出引腳和時鐘緩存器的輸入引腳連接;每片高速adc轉換器的時鐘引腳均與所述時鐘緩存器的時鐘輸出引腳連接。

9.根據權利要求1所述的高速雷達信號處理系統,其特征在于,所述信號采集電源電路包括4片ldo電源芯片,所述ldo電源芯片包括使能引腳,所述ldo電源芯片的使能引腳en通過電阻r209接地;所述ldo電源芯片的使能引腳en還與fpga芯片的io引腳連接。

10.根據權利要求1所述的高速雷達信號處理系統,其特征在于,

技術總結

本技術涉及一種高速雷達信號處理系統,屬于雷達技術領域,解決了現有技術中現有雷達信號處理的問題。系統包括:雷達信號采集芯片組、FPGA芯片組、SRIO交換芯片、DSP芯片組、信號采集電源電路和上位機;所述雷達信號采集芯片組與所述FPGA芯片組通信連接;所述FPGA芯片組、DSP芯片組和上位機均與所述SRIO交換芯片通信連接;所述信號采集電源電路為所述雷達信號采集芯片組供電。實現了高效靈活的雷達信號處理。

技術研發人員:曾繁榮,王博,劉曉東

受保護的技術使用者:北京華航無線電測量研究所

技術研發日:20240524

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!