帶隙基準電壓產生電路和包括其的半導體裝置的制作方法

本發明涉及一種能夠可靠地產生帶隙基準電壓的帶隙基準電壓產生電路以及具有該帶隙基準電壓產生電路的半導體裝置。

背景技術:

1、包括家用電器、智能電話、可穿戴裝置等的各種電子裝置包含諸如微控制器單元(mcu)、存儲器等的半導體裝置。

2、一種半導體裝置包括帶隙基準電壓產生電路,該帶隙基準電壓產生電路使用從外部源供應的電力來供應穩定的內部電力。

3、帶隙基準電壓產生電路需要即使在諸如電源電壓、工藝和溫度之類的驅動環境改變時也能夠穩定地產生并供應基準電壓的特性。

4、近來,帶隙基準電壓產生電路可能會因為驅動環境的變化而在初始啟動操作期間發生故障,導致輸出不正常的基準電壓;因此,要求與驅動環境的變化無關的穩定的啟動操作。

技術實現思路

1、技術問題

2、本發明提供了一種能夠通過實現獨立于驅動環境變化的穩定的啟動操作來穩定地產生帶隙基準電壓的帶隙基準電壓產生電路、以及具有該帶隙基準電壓產生電路的半導體裝置。

3、技術方案

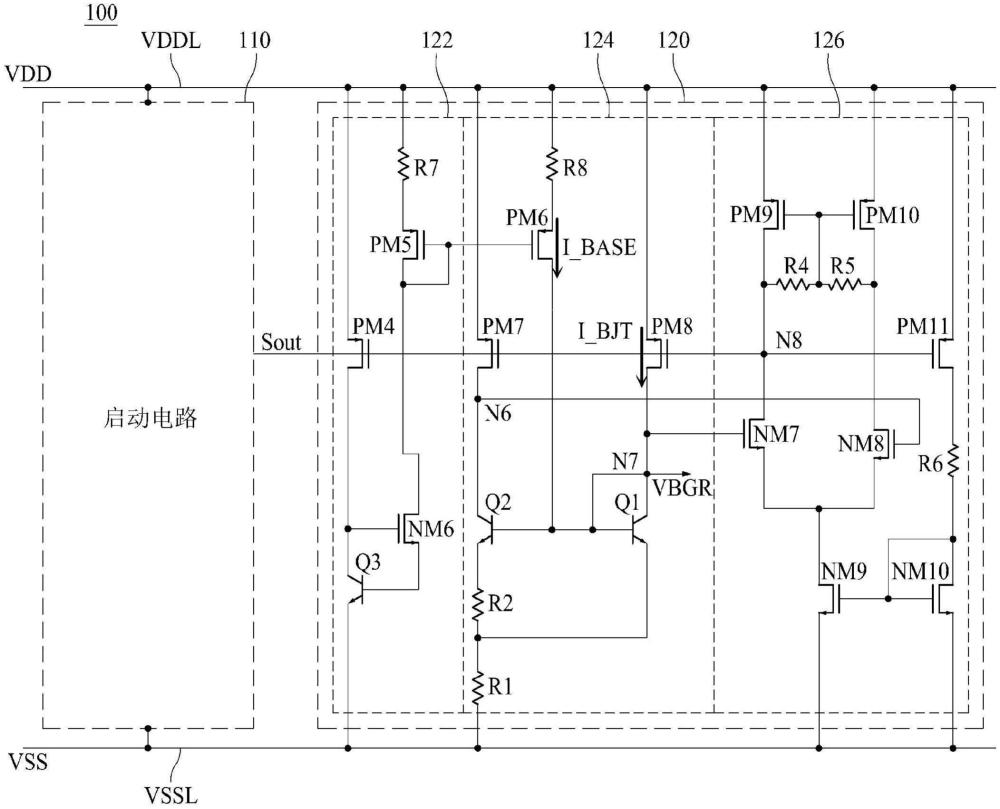

4、根據本發明的實施方式的帶隙基準電壓產生電路可以包括:啟動電路,其被配置為在第一電源電壓上升時輸出啟動信號;以及帶隙基準核心電路,其被配置為響應于所述啟動信號而被激活,并且產生并輸出帶隙基準電壓,其中所述啟動電路可包括:β乘法器基準電路,其包括級聯電流鏡電路,所述級聯電流鏡電路在第一電源線和第二電源線之間形成第一電流路徑和第二電流路徑;啟動輸出部,其被配置為響應于所述第二電流路徑的輸出節點處的電壓而輸出所述啟動信號;以及比較器,其被配置為將所述帶隙基準電壓與目標電壓進行比較以停用所述啟動電路的操作。

5、根據本發明的實施方式的半導體裝置可以包括:所述帶隙基準電壓產生電路;以及裝置電路,其被配置為接收和使用來自帶隙基準電壓產生電路的帶隙基準電壓。

6、技術效果

7、根據本發明的一個實施方式,帶隙基準電壓產生電路可以通過使用β乘法器基準電路允許啟動電路穩定地啟動帶隙基準核心電路的每個電路級,來穩定地產生和輸出帶隙基準電壓,而與驅動環境的變化(諸如電源電壓的上升時間、工藝的變化和溫度的變化)無關。

8、根據本發明的實施方式,帶隙基準電壓產生電路可以通過施密特觸發器電路使用啟動電路來產生和輸出對電源噪聲高度(不敏感)的帶隙基準電壓。

9、根據本發明的實施方式,帶隙基準電壓產生電路可以通過使用比較器在帶隙基準電壓高于目標電壓時終止啟動電路的操作,從而實現獨立于驅動環境的變化的穩定啟動電路,而沒有額外的功耗。

10、根據本發明的一個實施方式,包括帶隙基準電壓產生電路的半導體裝置可以通過獨立于驅動環境的變化而穩定地接收和使用基準電壓來確保操作可靠性。

技術特征:

1.一種帶隙基準電壓產生電路,所述帶隙基準電壓產生電路包括:

2.根據權利要求1所述的帶隙基準電壓產生電路,其中,所述β乘法器基準電路包括:

3.根據權利要求2所述的帶隙基準電壓產生電路,其中,所述pmos電流鏡包括:

4.根據權利要求3所述的帶隙基準電壓產生電路,其中,所述nmos電流鏡包括:

5.根據權利要求4所述的帶隙基準電壓產生電路,其中,所述啟動控制部包括:

6.根據權利要求5所述的帶隙基準電壓產生電路,其中,所述啟動控制部被配置為:當提供給所述第一電源線的所述第一電源電壓上升時,通過以二極管的形式連接的所述第一pmos晶體管、所述第三nmos晶體管和所述第二nmos晶體管來啟動所述β乘法器基準電路。

7.根據權利要求5所述的帶隙基準電壓產生電路,其中,在所述第一電源電壓上升時,當連接在所述第一pmos晶體管和所述第一nmos晶體管之間的第三節點的電壓等于連接在所述第二pmos晶體管和所述第二nmos晶體管之間的所述輸出節點的電壓時,所述第三nmos晶體管截止。

8.根據權利要求4所述的帶隙基準電壓產生電路,其中,所述β乘法器基準電路還包括:

9.根據權利要求8所述的帶隙基準電壓產生電路,其中,所述β乘法器基準電路還包括:

10.根據權利要求9所述的帶隙基準電壓產生電路,其中,所述比較器被配置為:

11.根據權利要求8所述的帶隙基準電壓產生電路,其中,所述啟動輸出部包括:

12.根據權利要求11所述的帶隙基準電壓產生電路,其中,所述啟動輸出部被配置為當所述β乘法器基準電路的所述輸出節點的電壓高于所述施密特觸發器電路的上升閾值電壓時,響應于所述施密特觸發器電路的所述輸出而通過所述第五nmos晶體管輸出所述啟動信號。

13.根據權利要求12所述的帶隙基準電壓產生電路,其中,當所述第三pmos晶體管響應于所述比較器的所述輸出而截止時,所述第五nmos晶體管響應于所述施密特觸發器電路的所述輸出而截止。

14.根據權利要求11所述的帶隙基準電壓產生電路,其中,所述帶隙基準核心電路包括:

15.一種半導體裝置,所述半導體裝置包括:

技術總結

本發明涉及一種帶隙基準電壓產生電路,其能夠通過實現穩定的啟動操作來穩定地產生帶隙基準電壓,而與驅動環境的變化無關。根據實施方式,帶隙基準電壓產生電路可包括:啟動電路,其在第一電源電壓上升時輸出啟動信號;以及帶隙基準核心電路,其中響應于啟動信號而啟用操作,并且所述帶隙基準核心電路產生并輸出帶隙基準電壓,其中所述啟動電路可包括:β乘法器基準電路,其包括級聯電流鏡電路,所述級聯電流鏡電路在第一電源線和第二電源線之間形成第一電流路徑和第二電流路徑;啟動輸出單元,其響應于第二電流路徑的輸出節點的電壓而輸出啟動信號;以及比較器,其將帶隙基準電壓與目標電壓進行比較以禁用所述啟動電路的操作。

技術研發人員:高玄水

受保護的技術使用者:LX半導體科技有限公司

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!