一種PUF碼生成裝置及生成方法與流程

本發(fā)明涉及信息安全,涉及一種puf碼生成裝置及生成方法。

背景技術(shù):

1、隨著物聯(lián)網(wǎng)、大數(shù)據(jù)、人工智能等技術(shù)的迅速發(fā)展,信息安全成為當(dāng)前時(shí)代背景下必須要重視和解決的關(guān)鍵問(wèn)題。被稱為“物理指紋”的物理不可克隆函數(shù)(physicallyunclonable?functions,puf))作為新型安全基礎(chǔ)技術(shù),可用于密鑰生成、授權(quán)、認(rèn)證等安全場(chǎng)景,從提出到至今的二十多年間一直受到信息安全領(lǐng)域的廣泛關(guān)注。

2、在puf設(shè)計(jì)與應(yīng)用過(guò)程中,重點(diǎn)關(guān)注“穩(wěn)定性”和“唯一性”兩個(gè)指標(biāo)。其中,“穩(wěn)定性”是指同一puf芯片在不同時(shí)間和空間中受相同激勵(lì)所產(chǎn)生響應(yīng)的相似度,常用片內(nèi)漢明距離來(lái)量化,該指標(biāo)的優(yōu)劣主要取決于puf芯片對(duì)溫度、電壓等環(huán)境條件變化的穩(wěn)定程度;“唯一性”是指不同puf芯片在相同時(shí)間和空間中受相同激勵(lì)所產(chǎn)生響應(yīng)的差異度,常用片間漢明距離來(lái)量化,該指標(biāo)的優(yōu)劣主要取決于puf芯片對(duì)工藝變化的敏感程度。

3、目前,國(guó)內(nèi)外出現(xiàn)了多種puf電路結(jié)構(gòu),根據(jù)所構(gòu)成單元類型的不同,可分為兩大類:一類基于延遲單元,如晶閘管型puf、雙堆疊型puf,其中晶閘管型puf因?qū)﹄妷鹤兓幻舾卸休^好的穩(wěn)定性,但唯一性較差,雙堆疊型puf因?qū)に囎兓舾卸休^好的唯一性,但穩(wěn)定性較差;另一類基于分壓?jiǎn)卧珉娫淳€網(wǎng)格puf、sram?puf,其中電源線網(wǎng)格puf因電阻比隨著溫度的變化基本保持不變而有較好的穩(wěn)定性,但唯一性較差;sram?puf因?qū)に囎兓舾卸休^好的唯一性,但穩(wěn)定性較差。因此,傳統(tǒng)puf電路難以同時(shí)具有良好的穩(wěn)定性和唯一性。

4、為了解決此問(wèn)題,目前已經(jīng)出現(xiàn)在較好唯一性puf電路基礎(chǔ)上進(jìn)行穩(wěn)定性增強(qiáng)的解決方案。如paral等人提出一種模式匹配技術(shù)來(lái)糾正出錯(cuò)的puf響應(yīng)序列,但需實(shí)現(xiàn)復(fù)雜的糾錯(cuò)碼譯碼邏輯;vivekraja等人提出監(jiān)測(cè)芯片工作溫度的方法,根據(jù)所反饋溫度信息的不同,使puf電路在不同電壓下工作,來(lái)提高puf電路相對(duì)于溫度變化的穩(wěn)定性,但對(duì)電壓變化無(wú)效。因此,使傳統(tǒng)puf電路同時(shí)具有較好穩(wěn)定性和唯一性的解決方案復(fù)雜度高,穩(wěn)定性提升效果有限。

5、根據(jù)上述分析,亟需設(shè)計(jì)一種puf架構(gòu),使其同時(shí)具備良好的穩(wěn)定性和唯一性。

技術(shù)實(shí)現(xiàn)思路

1、本發(fā)明旨在提供一種puf碼生成裝置及生成方法;以使puf架構(gòu)同時(shí)具備良好的唯一性和穩(wěn)定性。同時(shí),提出臨界可控電路,用于實(shí)現(xiàn)穩(wěn)定性按需可調(diào)。

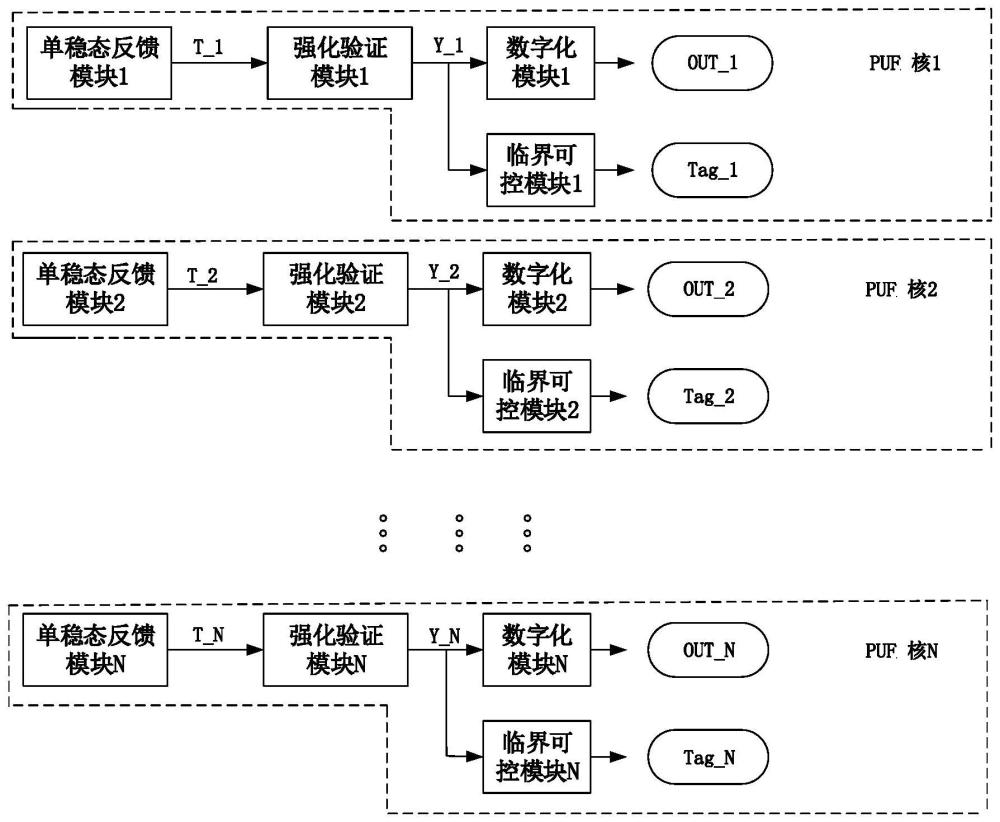

2、本發(fā)明公開了一種puf碼生成裝置,包括:并行設(shè)置的n個(gè)puf核;每個(gè)puf核用于產(chǎn)生1bit的puf碼;n個(gè)puf核共產(chǎn)生n?bit的puf碼;

3、每個(gè)puf核中均包括:?jiǎn)畏€(wěn)態(tài)反饋模塊、強(qiáng)化驗(yàn)證模塊、數(shù)字化模塊和臨界可控模塊;其中,

4、單穩(wěn)態(tài)反饋模塊,用于產(chǎn)生本puf核的1bit的puf碼來(lái)源的電壓值t;各puf核中的電壓值t呈非線性規(guī)律分布;

5、強(qiáng)化驗(yàn)證模塊,用于對(duì)電壓值t逐級(jí)驅(qū)動(dòng),輸出電壓y;

6、數(shù)字化模塊,用于對(duì)輸出電壓y進(jìn)行數(shù)字化,輸出本puf核的1bit的puf碼;

7、臨界可控模塊,用于對(duì)本puf核輸出的1bit的puf碼進(jìn)行穩(wěn)定性標(biāo)記;當(dāng)判斷輸出電壓y處于設(shè)定的臨界電壓范圍內(nèi),則將所述1bit的puf碼標(biāo)記為不穩(wěn)定的bit位,否則標(biāo)記為穩(wěn)定的bit位。

8、進(jìn)一步地,所述單穩(wěn)態(tài)反饋模塊包括比特單元電路和雙開單控開關(guān);

9、所述比特單元電路,用于實(shí)現(xiàn)電壓反向,將輸入端的電壓反向后從輸出端輸出;

10、所述雙開單控開關(guān)s的第一開關(guān)的第二接線端、第二開關(guān)的第一接線端分別與所述的比特單元電路的輸入端、輸出端連接;所述雙開單控開關(guān)s的第一開關(guān)的第一接線端和第二開關(guān)的第二接線端相連接,該連接的結(jié)點(diǎn)作為單穩(wěn)態(tài)反饋模塊輸出端。

11、進(jìn)一步地,所述比特單元電路包括:反相器電路inv、第一輔助調(diào)節(jié)電路和第二輔助調(diào)節(jié)電路;

12、所述反相器電路inv包括電壓輸入端、電壓輸出端、與第一輔助調(diào)節(jié)電路連接的結(jié)點(diǎn)、與第二輔助調(diào)節(jié)電路連接的結(jié)點(diǎn);

13、所述反相器電路的與第一輔助調(diào)節(jié)電路連接的結(jié)點(diǎn)與供電電源vdd之間連接有第一輔助調(diào)節(jié)電路;與第二輔助調(diào)節(jié)電路連接的結(jié)點(diǎn)與地gnd之間連接有第二輔助調(diào)節(jié)電路;

14、所述電壓輸入端接入的輸入電壓vin在經(jīng)過(guò)反相器電路inv的反相后從電壓輸出端輸出電壓vout;

15、所述第一輔助調(diào)節(jié)電路和第二輔助調(diào)節(jié)電路,用于對(duì)比特單元電路進(jìn)行限流和分壓。

16、進(jìn)一步地,所述第一輔助調(diào)節(jié)電路和第二輔助調(diào)節(jié)電路為包括電阻、mos二極管等在內(nèi)的具備限流和分壓功能的電子器件或者電路,用于對(duì)比特單元電路限流和分壓。

17、進(jìn)一步地,所述強(qiáng)化驗(yàn)證模塊包括多級(jí)級(jí)聯(lián)的比特單元電路;所述級(jí)聯(lián)的第一級(jí)比特單元電路的輸入端與所述單穩(wěn)態(tài)反饋模塊的輸出端t連接,所述級(jí)聯(lián)的最后一級(jí)比特單元的輸出端輸出電壓y;

18、每一級(jí)比特單元電路可作為一個(gè)單端比較器,將其輸入電壓與自身的翻轉(zhuǎn)電壓vtrip作比較;級(jí)聯(lián)的比特單元電路逐級(jí)放大其輸入電壓相對(duì)于自身的翻轉(zhuǎn)電壓vtrip的偏離量,最終輸出接近vdd或者gnd的輸出電壓y。

19、進(jìn)一步地,數(shù)字化模塊電路中包括buf模塊;所述buf模塊的輸入端與所述強(qiáng)化驗(yàn)證模塊的輸出端y連接,輸出端輸出1bit的puf碼out;

20、當(dāng)輸出電壓y的電壓值在vdd附近時(shí),buf模塊輸出“1”;

21、當(dāng)輸出電壓y的電壓值在gnd附近時(shí),buf模塊輸出“0”。

22、進(jìn)一步地,所述臨界可控模塊包括m路臨界子模塊電路,每一路的臨界子模塊電路對(duì)應(yīng)一個(gè)臨界電壓范圍;

23、通過(guò)對(duì)不同臨界范圍選通控制,使輸出電壓y接入到選擇的一路臨界子模塊電路的輸入端,所述臨界子模塊判斷所述輸出電壓y是否處于所述臨界電壓范圍內(nèi);若是,則該路的臨界子模塊輸出端tag為1,此時(shí)將所述輸出電壓y數(shù)字化后輸出的1bit的puf碼標(biāo)記為不穩(wěn)定的bit位;反之,該路的臨界子模塊輸出端tag為0,將puf碼標(biāo)記為穩(wěn)定的bit位。

24、進(jìn)一步地,m路臨界子模塊電路中的第i路臨界子模塊電路中包括單開單控開關(guān)si、反相器noti,1、反相器noti,2和二輸入異或門xori;

25、其中,單開單控開關(guān)si的第一開關(guān)端接入輸出電壓y,第二開關(guān)端分別連接反相器noti,1和反相器noti,2的輸入端;反相器noti,1和反相器noti,2的輸出端分別與二輸入異或門xori的兩個(gè)輸入端連接;二輸入異或門xori的輸出端作為第i路臨界子模塊電路的輸出端。

26、進(jìn)一步地,在第i路臨界子模塊電路中通過(guò)設(shè)置反相器noti,1、反相器noti,2的翻轉(zhuǎn)電壓來(lái)進(jìn)行臨界電壓范圍的設(shè)置;其中,

27、設(shè)置反相器noti,1的pmos管的開啟電壓大于nmos管的開啟電壓,得到翻轉(zhuǎn)電壓小于vdd/2的電壓v?i,trip_l,將其作為第i個(gè)臨界子模塊的臨界電壓范圍的下限值;

28、設(shè)置反相器noti,2的pmos管的開啟電壓小于nmos管的開啟電壓,得到翻轉(zhuǎn)電壓大于vdd/2的電壓v?i,trip_h,將其作為第i個(gè)臨界子模塊的臨界電壓范圍的上限值。

29、本發(fā)明還公開了一種利用如上所述的puf碼生成裝置的puf碼生成方法,包括:

30、步驟s1、對(duì)所述puf裝置進(jìn)行初始化,設(shè)定包括供電電壓vdd在內(nèi)的puf工作條件;

31、步驟s2、供電電源工作穩(wěn)定后,控制puf裝置中n個(gè)puf核中單穩(wěn)態(tài)反饋模塊的雙開單控開關(guān)s閉合;各puf核工作后,輸出n?bit的puf碼;

32、步驟s3、根據(jù)設(shè)定的臨界電壓范圍,選通n個(gè)puf核的臨界可控模塊中對(duì)應(yīng)的臨界子模塊電路;每個(gè)puf核中選通的臨界子模塊電路對(duì)本puf核輸出的1bit的puf碼進(jìn)行穩(wěn)定性標(biāo)記;臨界子模塊電路輸出“1”表示puf碼不穩(wěn)定,臨界子模塊電路輸出“0”表示puf碼穩(wěn)定;

33、步驟s4、對(duì)步驟s2中輸出的n?bit的puf碼和步驟s3中輸出的nbit的標(biāo)記碼進(jìn)行提取。

34、本發(fā)明可實(shí)現(xiàn)以下有益效果之一:

35、本發(fā)明公開的puf碼生成裝置及生成方法;不同puf核的單穩(wěn)態(tài)反饋環(huán)路輸出為集中在vdd/2附近的單穩(wěn)態(tài);這些單穩(wěn)態(tài)輸出作為puf碼來(lái)源,能夠保證該架構(gòu)puf具備良好的工藝敏感性,同時(shí),能夠抵抗溫度和電源電壓等環(huán)境因素的影響,從而使該puf架構(gòu)同時(shí)具備良好的唯一性和穩(wěn)定性。由于受工藝偏差影響,不同puf核的單穩(wěn)態(tài)反饋環(huán)路中的比特單元電路均工作在呈非線性規(guī)律的亞穩(wěn)態(tài),使該puf架構(gòu)具有抗攻擊能力。

36、通過(guò)臨界可控模塊電路中包含的不同臨界電壓范圍的臨界子模塊,對(duì)n?bit的puf碼進(jìn)行標(biāo)記;當(dāng)臨界子模塊的電壓范圍越大,可被標(biāo)記的不穩(wěn)定的比特位越多,片內(nèi)漢明距離越接近0%,puf穩(wěn)定性越高,從而實(shí)現(xiàn)在芯片應(yīng)用階段“穩(wěn)定性”的靈活調(diào)整。

- 還沒(méi)有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!