基于憶阻器的非易失性多數門電路和加法電路的控制方法及裝置

本發明屬于微電子邏輯運算,更具體地,涉及一種基于憶阻器的非易失性多數門電路和加法電路的控制方法及裝置。

背景技術:

1、傳統計算機采用馮·諾依曼體系結構,其中存儲單元與處理單元在物理上是分離的。通常,處理單元從存儲單元中讀取數據,完成相應的算術邏輯運算后,再將數據寫回存儲單元。頻繁的讀寫操作給總線帶來了巨大的負擔,尤其是在傳輸速度有限的情況下,這不僅影響了數據傳輸效率,還造成了相當大的功耗消耗。同時,處理單元與存儲單元之間的速度不匹配,這一差異還在逐年加劇。因此,如何解決馮·諾依曼架構中存在的“瓶頸問題”和“存儲墻”問題,成為了計算機體系結構領域的研究重點。

2、為了突破這些瓶頸,存算一體技術應運而生。該技術通過將計算和存儲功能集成在同一硬件平臺上,實現了高計算并行性、低延遲和低功耗等優勢,逐漸成為學術界和產業界的研究熱點。憶阻器作為一種新型的非易失性存儲器件,具有低功耗、小尺寸以及與cmos工藝兼容等優點,成為了存內計算架構的理想候選器件。憶阻器能夠通過改變其電阻狀態來存儲信息,且在斷電后仍能保持電阻狀態,因此天然適用于數字邏輯運算。通過同時選中多個憶阻器單元進行讀出操作,即可在不顯式取出憶阻器存儲數據的條件下完成指定的邏輯操作或復雜的算術功能,從而實現存算一體。這種方式極大地提高了信息處理的速度和效率。

3、多數反向圖(majority-inverter?graph,mig)邏輯是一種新型的數據邏輯表示結構,它由多數門邏輯(majority,maj)和取反邏輯(inverter,inv)組成,其中三輸入多數決定門的邏輯表達式為:m(a,b,c)?=?a·b?+a·c?+?b·c,取反邏輯的表達式為:。maj和取反邏輯構成完備的邏輯集,即所有布爾邏輯函數都可以通過迭代maj和取反邏輯實現。邏輯優化包括操縱邏輯表示結構以使某些目標度量最小化,邏輯優化方法與運行它們的數據結構緊密相連,mig邏輯原語本身展示出高效的邏輯綜合潛能。mig在實現相同復雜邏輯往往需要更小的邏輯深度,因而傳播延遲上具有更好的實驗結果。實現mig邏輯的重點和難點在于實現多數門邏輯。多數門邏輯在加法器、乘法器等算術電路以及復雜推理任務中具有核心作用,因此研究一種多數門邏輯電路存在重要意義。

4、然而,現有基于cmos的多數門實現不僅硬件復雜度較高,還存在顯著的延遲和功耗瓶頸。基于憶阻器實現多數門邏輯則為這一問題提供了一種新的解決方案。現有的基于憶阻器的多數門邏輯的實現方案通過三個憶阻器單元分別對a、b、c進行操作,實現了三輸入多數門邏輯m(a,b,c)?=?a·b?+?a·c?+?b·c,雖然能夠降低硬件復雜度,但這種邏輯方案僅支持單一邏輯操作,缺乏取反邏輯的實現;而在基于多數門邏輯實現的多功能邏輯中往往不僅涉及傳統的多數門邏輯m(a,b,c)?=?a·b?+a·c?+?b·c,還涉及包括取反邏輯的多數門邏輯;由于同時涉及兩種不同類型的多數門邏輯,若采用現有的基于憶阻器的多數門邏輯的實現方案,往往需要將多數門邏輯分解為多數門邏輯m(a,b,c)和取反邏輯兩個獨立邏輯操作,且至少四個憶阻器單元分別對a、b、c、進行操作,所需的器件數量較多,集成度較低,計算速度也較低,無法以較高的集成度和計算速度滿足實際應用中對多功能邏輯的需求。

技術實現思路

1、針對現有技術的以上缺陷或改進需求,本發明提供了一種基于憶阻器的非易失性多數門電路和加法電路的控制方法及裝置,用以解決現有技術由于僅支持單一邏輯操作難以以較高的集成度和計算速度滿足實際應用中對多功能邏輯的需求的技術問題。

2、為了實現上述目的,第一方面,本發明提供了一種基于憶阻器的非易失性多數門電路的控制方法;

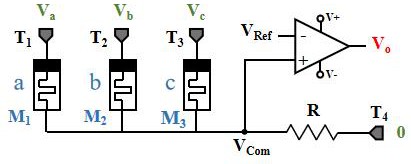

3、多數門電路包括:電壓比較器、電阻和三個相同的憶阻器;三個憶阻器的負極均與電阻的一端相連;電阻的另一端接地;電壓比較器的第一輸入端連接三個憶阻器和電阻的公共節點;電阻的阻值為憶阻器的低阻態電阻值;

4、上述控制方法包括:

5、將待進行多數門邏輯運算的邏輯值a、b、c分別對應寫入到三個憶阻器中,在寫入邏輯值a的憶阻器的正極施加電壓va,在寫入邏輯值b的憶阻器的正極施加電壓vb,在寫入邏輯值c的憶阻器的正極施加電壓vc,在電壓比較器的第二輸入端接入參考電壓vref,在電壓比較器的輸出端得到多數門邏輯運算的結果;

6、其中,當對邏輯值a、b、c進行多數門邏輯運算m(a,b,c)?=?a·b?+?a·c?+?b·c時,va=?vb=?vc=?v1,vref=?vref1;0<v1<vset;v1/2<vref1<2v1/3;

7、當對邏輯值a、b、c進行多數門邏輯運算時,va=vb=?v2,vc=?0,vref=?vref2;0<v2<vset;v2/3<vref2<v2/2;

8、vset為憶阻器由高阻態轉變為低阻態的閾值;當電壓比較器第一輸入端的電壓大于第二輸入端的電壓時,輸出端輸出第一電平,以第一電平作為多數門邏輯運算的結果“1”;否則,輸出端輸出第二電平,以第二電平作為多數門邏輯運算的結果“0”。

9、進一步優選地,通過設置憶阻器的高低阻態來寫入對應的邏輯值;其中,憶阻器的高阻態對應邏輯值“0”,低阻態對應邏輯值“1”。

10、第二方面,本發明提供了一種多數門運算裝置,包括:多數門電路和控制器;

11、其中,多數門電路包括:電壓比較器、電阻和三個相同的憶阻器;三個憶阻器的負極均與電阻的一端相連;電阻的另一端接地;電壓比較器的第一輸入端連接三個憶阻器和電阻的公共節點;電阻的阻值為憶阻器的低阻態電阻值;

12、控制器用于執行本發明第一方面所提供的控制方法。

13、第三方面,本發明提供了一種加法電路的控制方法,用于實現n-bit數an......a2a1與bn......b2b1的加法運算;加法電路包括:電壓比較器、電阻和五個憶阻器;五個憶阻器的負極均與電阻的一端相連;電阻的另一端接地;電壓比較器的第一輸入端連接五個憶阻器和電阻的公共節點;電阻的阻值為憶阻器的低阻態電阻值;n≥1;

14、上述控制方法包括:執行n輪加法子過程;其中,在第i輪加法子過程中執行以下操作:

15、選取三個憶阻器分別記為第一憶阻器、第二憶阻器和第三憶阻器;在第一憶阻器中寫入邏輯值ai,在第二憶阻器中寫入邏輯值bi,在第三憶阻器中寫入第i輪加法的進位ci;

16、分別在第一憶阻器、第二憶阻器和第三憶阻器的正極施加電壓v1,在電壓比較器的第二輸入端接入參考電壓vref1,在電壓比較器的輸出端得到多數門邏輯運算的結果m(ai,bi,ci)?=?ai·bi+?ai·ci+?bi·ci,作為第i+1輪加法的進位ci+1;

17、分別在第一憶阻器和第二憶阻器的正極施加電壓v2,在第三憶阻器的正極施加幅值為0的電壓,在電壓比較器的第二輸入端接入參考電壓vref2,在電壓比較器的輸出端得到多數門邏輯運算的結果;

18、將剩余的兩個未置值的憶阻器分別記為第四憶阻器和第五憶阻器,在第四憶阻器中寫入m(ai,bi,ci),在第五憶阻器中寫入;

19、分別在第三憶阻器和第五憶阻器的正極施加電壓v2,在第四憶阻器的正極施加幅值為0的電壓,在電壓比較器的第二輸入端接入參考電壓vref2,在電壓比較器的輸出端得到多數門邏輯運算的結果,作為在第i輪加法的求和結果si;

20、sn......s2s1和cn+1即為所求n-bit數an......a2a1與bn......b2b1的相加結果;

21、其中,i=1,2,...,n;0<v1<vset;v1/2<vref1<2v1/3;0<v2<vset;v2/3<vref2<v2/2;vset為憶阻器由高阻態轉變為低阻態的閾值;當電壓比較器第一輸入端的電壓大于第二輸入端的電壓時,輸出端輸出第一電平,以第一電平作為多數門邏輯運算的結果“1”;否則,輸出端輸出第二電平,以第二電平作為多數門邏輯運算的結果“0”。

22、進一步優選地,通過設置憶阻器的高低阻態來寫入對應的邏輯值;其中,憶阻器的高阻態對應邏輯值“0”,低阻態對應邏輯值“1”。

23、第四方面,本發明提供了一種加法運算裝置,包括:加法電路和控制器;

24、加法電路包括:電壓比較器、電阻和五個憶阻器;五個憶阻器的負極均與電阻的一端相連;電阻的另一端接地;電壓比較器的第一輸入端連接五個憶阻器和電阻的公共節點;電阻的阻值為憶阻器的低阻態電阻值;

25、控制器用于執行本發明第三方面所提供的控制方法。

26、第五方面,本發明提供了一種控制系統,包括:存儲器和處理器,所述存儲器存儲有計算機程序,所述處理器執行所述計算機程序時執行本發明第一方面或第三方面所提供的控制方法。

27、第六方面,本發明還提供了一種計算機可讀存儲介質,所述計算機可讀存儲介質包括存儲的計算機程序,其中,在所述計算機程序被處理器運行時控制所述存儲介質所在設備執行本發明第一方面或第三方面所提供的控制方法。

28、第七方面,發明還提供了一種計算機程序產品,包括計算機程序/指令,該計算機程序/指令被處理器執行時實現本發明第一方面或第三方面所提供的控制方法。

29、總體而言,通過本發明所構思的以上技術方案,能夠取得以下有益效果:

30、1、在本發明所提供的基于憶阻器的非易失性多數門電路的控制方法及對應的多數門運算裝置中,多數門電路包括三個憶阻器、一個電阻和一個電壓比較器;三個憶阻器分別對應輸入待進行多數門邏輯運算的邏輯值a、b、c,多數門邏輯運算的結果由電壓比較器根據公共節點電壓與參考電壓的比較結果確定;通過改變憶阻器正極的電壓,即可實現傳統的多數門邏輯m(a,b,c)和包含取反邏輯的新型多數門邏輯;其中,多數門邏輯的實現避免了將其分解為多數門邏輯m(a,b,c)和取反邏輯兩個獨立邏輯操作的情況,通過一步施加電壓的方式即可實現得到,使得在不同類型的多數門邏輯實現過程中,無需增加憶阻器數量,能夠以較少的器件、較快的計算速度實現兩種多數門邏輯運算,且這兩種多數門邏輯是完備的,通過組合兩種多數門邏輯能夠實現任意布爾函數,進而滿足了多功能邏輯的需求;基于此,本發明能夠以較高的集成度、較快的計算速度滿足實際應用中對多功能邏輯的需求。

31、2、本發明所提供的基于憶阻器的非易失性多數門電路的控制方法及對應的多數門運算裝置,在邏輯計算完成后三個輸入憶阻器狀態依舊保持寫入的輸入信息值,對輸入信息并無破壞性,同時具有非易失性,實現了一種輸入為憶阻器阻值、且運算過程為非破壞的多數門邏輯電路;該電路的數據復用性較強,在實際應用中無需額外的復制操作以保存數據。

32、3、本發明所提供的加法電路的控制方法及對應的加法運算裝置,基于本發明第一方面所提供的多數門邏輯運算的實現思路實現得到,通過對組合m(a,b,c)和兩種多數門邏輯進行組合,并分別采用本發明第一方面所提供的實現m(a,b,c)和的控制方法對應進行控制,能夠以較少的器件和較快的計算速度實現加法運算。

- 還沒有人留言評論。精彩留言會獲得點贊!