半導體結構及其形成方法與流程

本發明實施例涉及半導體制造領域,尤其涉及一種半導體結構及其形成方法。

背景技術:

1、隨著半導體制造技術的飛速發展,半導體器件朝著更高的元件密度,以及更高集成度的方向發展。晶體管作為基本半導體器件之一目前正被廣泛應用。所以隨著半導體器件密度和集成度的提高,平面晶體管的柵極尺寸也越來越短,傳統平面晶體管對溝道電流的控制能力變弱,出現短溝道效應,引起漏電流增大,最終影響半導器件的電學性能。

2、為了更好的適應特征尺寸的減小,半導體工藝逐漸開始從平面mosfet向具有更高功效的三維立體式的晶體管過渡,例如:鰭式場效應晶體管(finfet)。在finfet中,柵極至少可以從兩側對超薄體(鰭部)進行控制,與平面mosfet相比,柵極對溝道的控制能力更強,能夠很好的抑制短溝道效應;且finfet相對于其他器件,與現有集成電路制造具有更好的兼容性。

3、此外,為了提高芯片運行速度,提高晶體管的性能,現有技術通過在源漏摻雜區引入應力層,在晶體管的溝道區域引入壓應力或拉應力,以提高溝道內載流子的遷移率,從而改善晶體管的性能。因此,目前鰭式場效應晶體管中的應力層位于柵極結構兩側的鰭部內。

4、然而,隨著半導體器件尺寸的縮小,相鄰鰭部之間的距離也隨之縮小。為了防止相鄰器件之間發生橋接(bridge),引入了雙擴散隔斷(doublediffusion?break,ddb)結構,沿著鰭部延伸方向,相鄰兩個晶體管之間的間距為一個柵極節距。為了進一步壓縮芯片面積,又引入了單擴散隔斷(singlediffusion?break,sdb)結構,引入sdb結構后,沿著鰭部延伸方向,兩個相鄰晶體管之間的間距僅為一個柵極的寬度。

5、但是,目前半導體結構的性能仍有待提高。

技術實現思路

1、本發明實施例解決的問題是提供一種半導體結構及其形成方法,以提高半導體結構的性能。

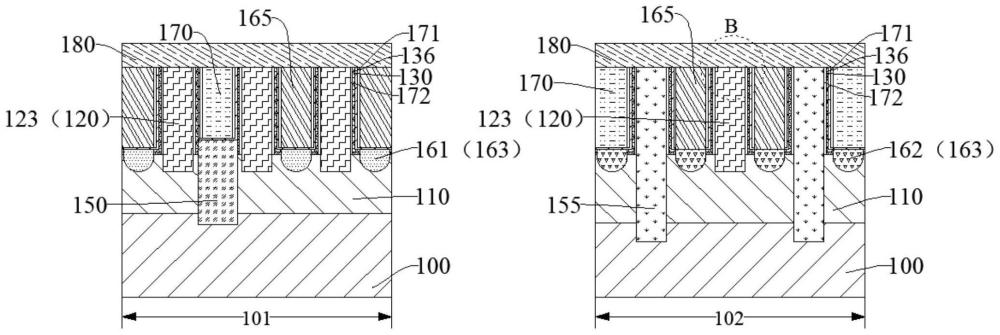

2、為解決上述問題,本發明實施例提供一種半導體結構,包括:襯底,所述襯底包括pmos區和nmos區,所述襯底上形成有分立的鰭部;柵極結構,位于所述襯底上且橫跨所述鰭部,所述柵極結構覆蓋所述鰭部的部分頂部和部分側壁;第一隔離結構,位于所述pmos區中,且位于待隔離的相鄰柵極結構之間的鰭部中;第二隔離結構,位于所述nmos區中,所述第二隔離結構橫跨所述柵極結構側部的鰭部并與所述柵極結構并列排布,所述第二隔離結構的底部延伸至所述鰭部中;第一源漏摻雜層,位于所述pmos區的柵極結構兩側的鰭部中;第二源漏摻雜層,位于所述nmos區的柵極結構兩側的鰭部中。

3、相應的,本發明實施例還提供一種半導體結構的形成方法,包括:提供襯底,所述襯底包括pmos區和nmos區,所述襯底上形成有分立的鰭部;在所述襯底上形成橫跨所述鰭部的柵極結構,所述柵極結構覆蓋所述鰭部的部分頂部和部分側壁;在所述pmos區中,在待隔離的相鄰柵極結構之間的鰭部中形成第一隔離結構;形成所述第一隔離結構后,在所述pmos區的柵極結構兩側的鰭部中形成第一源漏摻雜層;在所述nmos區的柵極結構兩側的鰭部中形成第二源漏摻雜層;在所述nmos區中,在部分柵極結構的位置處形成第二隔離結構,所述第二隔離結構延伸至所述鰭部中。

4、與現有技術相比,本發明實施例的技術方案具有以下優點:

5、本發明實施例提供的半導體結構中,包括位于所述pmos區中,且位于待隔離的相鄰柵極結構之間的鰭部中的第一隔離結構,位于所述nmos區中的第二隔離結構,所述第二隔離結構橫跨所述柵極結構側部的鰭部并與所述柵極結構并列排布,所述第二隔離結構的底部延伸至所述鰭部中;位于所述pmos區的柵極結構兩側的鰭部中的第一源漏摻雜層,位于所述nmos區的柵極結構兩側的鰭部中的第二源漏摻雜層。由于pmos區的載流子是空穴,nmos區的載流子是電子,電子的響應速度會較快,因此與pmos區的響應速度相比,nmos區的響應速度較快;而且,空穴對應力的變化更加敏感度,即損失相同絕對值的應力后,pmos區的響應速度下降幅度大于nmos區的響應速度下降幅度,在所述pmos區中待隔離的相鄰柵極結構之間的鰭部中形成第一隔離結構,避免了去除pmos區的柵極結構,減小了形成所述第一隔離結構對第一源漏摻雜層造成的應力損失,相應也減小了pmos區的響應速度下降幅度,從而減小了形成第一隔離結構后,pmos區和nmos區的響應速度的差異,進而提高了半導體結構的性能;而且,與在pmos區和nmos區均形成第一隔離結構的方案相比,本發明實施例包括位于所述pmos區中,且位于待隔離的相鄰柵極結構之間的鰭部中的第一隔離結構,位于所述nmos區中的第二隔離結構,所述第二隔離結構橫跨所述柵極結構側部的鰭部并與所述柵極結構并列排布,所述第二隔離結構的底部延伸至所述鰭部中,也即在所述nmos區的部分柵極結構的位置處形成延伸至所述鰭部中的第二隔離結構,有利于節省半導體結構的面積。

6、本發明實施例提供的半導體結構的形成方法中,在所述pmos區的待隔離的相鄰柵極結構之間的鰭部中形成第一隔離結構,形成所述第一隔離結構后,在所述pmos區的柵極結構兩側的鰭部中形成第一源漏摻雜層,在所述nmos區的柵極結構兩側的鰭部中形成第二源漏摻雜層,在所述nmos區中,在部分柵極結構的位置處形成第二隔離結構,所述第二隔離結構延伸至所述鰭部中。由于pmos區的載流子是空穴,nmos區的載流子是電子,電子的響應速度會較快,因此與pmos區的響應速度相比,nmos區的響應速度較快;而且,空穴對應力的變化更加敏感度,即損失相同絕對值的應力后,pmos區的響應速度下降幅度大于nmos區的響應速度下降幅度,在所述pmos區中待隔離的相鄰柵極結構之間的鰭部中形成第一隔離結構,避免了去除pmos區的柵極結構,減小了形成所述第一隔離結構對第一源漏摻雜層造成的應力損失,相應也減小了pmos區的響應速度下降幅度,從而減小了形成第一隔離結構后,pmos區和nmos區的響應速度的差異,進而提高了半導體結構的性能;而且,與在pmos區和nmos區均形成第一隔離結構的方案相比,本發明實施例在所述pmos區的待隔離的相鄰柵極結構之間的鰭部中形成第一隔離結構,在所述nmos區中,在部分柵極結構的位置處形成第二隔離結構,所述第二隔離結構延伸至所述鰭部中,也即在所述nmos區的部分柵極結構的位置處形成延伸至所述鰭部中的第二隔離結構,有利于節省半導體結構的面積。

技術特征:

1.一種半導體結構,其特征在于,包括:

2.如權利要求1所述的半導體結構,其特征在于,所述第一隔離結構的材料包括石墨烯。

3.如權利要求1所述的半導體結構,其特征在于,所述半導體結構還包括:

4.如權利要求1~3中任一項所述的半導體結構,其特征在于,所述柵極結構為器件柵極結構。

5.如權利要求3所述的半導體結構,其特征在于,所述半導體結構還包括:

6.如權利要求5所述的半導體結構,其特征在于,所述半導體結構還包括:

7.一種半導體結構的形成方法,其特征在于,包括:

8.如權利要求7所述的半導體結構的形成方法,其特征在于,形成所述第一隔離結構的步驟包括:

9.如權利要求8所述的半導體結構的形成方法,其特征在于,在形成所述第一凹槽之前,所述形成方法還包括:在所述pmos區的柵極結構兩側的鰭部中形成源漏凹槽;

10.如權利要求8或9所述的半導體結構的形成方法,其特征在于,形成所述第一凹槽的步驟包括:

11.如權利要求10所述的半導體結構的形成方法,其特征在于,在形成所述第一隔離結構的步驟中,在所述第一掩膜結構的保護下,形成所述第一隔離結構;

12.如權利要求9所述的半導體結構的形成方法,其特征在于,形成所述第一源漏摻雜層的步驟包括:形成所述第一隔離結構后,在所述pmos區剩余的源漏凹槽中形成第一源漏摻雜層。

13.如權利要求8所述的半導體結構的形成方法,其特征在于,在所述第一凹槽中形成第一隔離結構的工藝包括介電質上介電質選擇性沉積工藝。

14.如權利要求13所述的半導體結構的形成方法,其特征在于,形成所述第一凹槽后,形成所述第一隔離結構前,所述形成方法還包括:對所述第一凹槽的表面進行氧化處理;

15.如權利要求7所述的半導體結構的形成方法,其特征在于,形成所述第二源漏摻雜層后,形成所述第二隔離結構前,所述形成方法還包括:形成覆蓋源漏摻雜層頂部的層間介質層,所述層間介質層還覆蓋所述柵極結構的側壁、以及第一隔離結構的頂部;

16.如權利要求15所述的半導體結構的形成方法,其特征在于,在所述襯底上形成橫跨所述鰭部的柵極結構的步驟中,所述柵極結構為偽柵極結構;

17.如權利要求7所述的半導體結構的形成方法,其特征在于,形成所述第二源漏摻雜層后,所述第二源漏摻雜層和第一源漏摻雜層構成源漏摻雜層,且在形成所述第二隔離結構前,所述形成方法還包括:形成覆蓋源漏摻雜層頂部的層間介質層,所述層間介質層還覆蓋所述柵極結構的側壁、以及第一隔離結構的頂部;

18.如權利要求17所述的半導體結構的形成方法,其特征在于,形成所述源漏互連層的步驟包括:

19.如權利要求17或18所述的半導體結構的形成方法,其特征在于,在形成所述柵極結構后,在形成第一隔離結構前,所述形成方法還包括:在所述柵極結構的側壁上形成側墻結構,所述側墻結構包括最靠近柵極結構的第一側墻層;

20.如權利要求17所述的半導體結構的形成方法,其特征在于,形成所述犧牲層的工藝包括原子層沉積工藝。

技術總結

一種半導體結構及其形成方法,半導體結構包括具有PMOS區和NMOS區的襯底,襯底上形成有分立的鰭部;柵極結構,位于襯底上且橫跨鰭部,柵極結構覆蓋鰭部的部分頂部和部分側壁;第一隔離結構,位于PMOS區中待隔離的相鄰柵極結構之間的鰭部中;第二隔離結構,位于NMOS區中,第二隔離結構橫跨柵極結構側部的鰭部并與柵極結構并列排布,第二隔離結構的底部延伸至鰭部中;第一源漏摻雜層,位于PMOS區的柵極結構兩側的鰭部中;第二源漏摻雜層,位于NMOS區的柵極結構兩側的鰭部中。本發明減小了形成第一隔離結構后,PMOS區和NMOS區的響應速度差異,進而提高了半導體結構的性能;而且還有利于節省半導體結構的面積。

技術研發人員:邱晶

受保護的技術使用者:中芯國際集成電路制造(上海)有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!