用于量子芯片的邊緣電容耦合的制作方法

本公開(kāi)總體上涉及電氣裝置,并且更具體地涉及用于量子芯片的邊緣電容耦合。相關(guān)技術(shù)的描述量子計(jì)算芯片通常大于在常規(guī)cmos電子裝置中使用的那些。在某些點(diǎn)上,制造和生產(chǎn)越來(lái)越大的量子芯片的能力變得困難。此時(shí),為了增大量子裝置的尺寸,期望將單個(gè)量子芯片連接在一起以有效地形成更大的裝置。當(dāng)將兩個(gè)量子位連接在一起時(shí),存在在這兩個(gè)量子位之間維持量子位狀態(tài)的要求。然而,量子位電路非常容易從環(huán)境中拾取干擾或一些其他不希望的信號(hào)。此外,量子位之間的連接應(yīng)該具有低的損耗。在這種情況下,“損耗”的特征通常在于量子位以及量子位芯片上的相關(guān)聯(lián)的共振結(jié)構(gòu)的頻率范圍,該頻率范圍可以是例如幾千兆赫的量級(jí)。在存在電介質(zhì)的電連接中,通常使用的電介質(zhì)材料的損耗角正切本質(zhì)上通常是如此有損的,以至于它們?cè)诹孔佑?jì)算系統(tǒng)中的使用將破壞量子位鏈中的量子態(tài)。例如,具有1×10-3的損耗角正切并且緊密連接到量子位和量子裝置上存在的諧振器的介電材料在千兆赫范圍內(nèi)操作,在能量耗散和量子位狀態(tài)在量子位連接之間丟失之前,基本上將裝置操作限制到大約微秒。實(shí)際上來(lái)說(shuō),合適的介電材料將需要10-6或10-7量級(jí)的損耗角正切以用于量子位連接,但是這樣的介電材料是稀缺的,并且它們的可用性和使用是不切實(shí)際的。因此,存在有限的材料選擇可用于構(gòu)造量子位電連接。

背景技術(shù):

技術(shù)實(shí)現(xiàn)思路

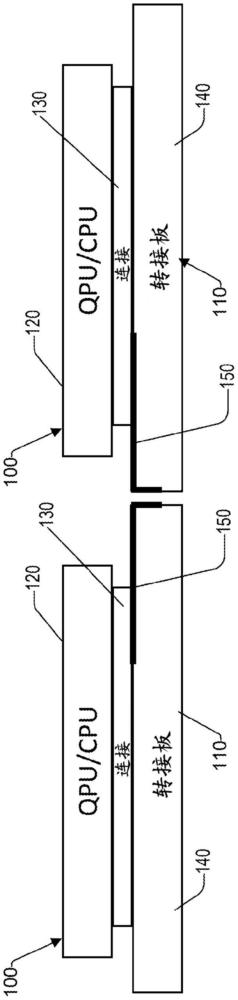

1、根據(jù)本公開(kāi)的實(shí)施例,提供了一種量子計(jì)算芯片裝置。量子計(jì)算芯片裝置包括第一芯片。第一芯片包括第一信號(hào)線。第一信號(hào)線包括位于第一芯片邊緣附近或邊緣上的遠(yuǎn)端和位于遠(yuǎn)離第一芯片邊緣的近端。量子計(jì)算芯片裝置還包括第二芯片。第二芯片包括第二信號(hào)線。第二信號(hào)線包括位于第二芯片的邊緣附近或邊緣上的遠(yuǎn)端和位于遠(yuǎn)離第二芯片的邊緣的近端。第二芯片的第二信號(hào)線被設(shè)置成與第一芯片的第一信號(hào)線對(duì)齊以形成電容性總線連接。第一信號(hào)線和第二信號(hào)線被配置為傳導(dǎo)信號(hào)。第一芯片的第一信號(hào)線相對(duì)于第二芯片的第二信號(hào)線的布置提供了對(duì)量子計(jì)算裝置中的芯片到芯片耦合的改進(jìn)。通過(guò)使用基于邊緣的耦合,通過(guò)由第一信號(hào)線和第二信號(hào)線產(chǎn)生的電容場(chǎng)進(jìn)行間接信號(hào)連接。基于邊緣的電容耦合布置增加了系統(tǒng)中的量子計(jì)算元件之間傳輸?shù)牧孔游坏臄?shù)量,這增加了系統(tǒng)的量子計(jì)算效率。

2、在可與前述實(shí)施例組合的實(shí)施例中,第一信號(hào)線的遠(yuǎn)端通過(guò)襯底材料與第一芯片的邊緣間隔開(kāi)。通過(guò)允許一些襯底材料位于信號(hào)線和芯片邊緣之間,在形成基于電容的耦合的協(xié)作芯片的信號(hào)線之間提供了有保證的間隔。物理間隔防止芯片之間的無(wú)意的電連接發(fā)生,這種電連接可能在芯片內(nèi)連接中丟失量子位。

3、根據(jù)本公開(kāi)的實(shí)施例,提供了一種量子計(jì)算芯片。量子計(jì)算芯片包括襯底。襯底包括第一端和第二端。量子計(jì)算芯片還包括第一超導(dǎo)金屬信號(hào)線。第一超導(dǎo)金屬線包括位于襯底的第一端和襯底的第二端中間的第一端。超導(dǎo)金屬線的第二端位于襯底的第二端的邊緣上。量子計(jì)算芯片還包括第二超導(dǎo)金屬信號(hào)線。第二超導(dǎo)金屬信號(hào)線包括定位在襯底的第一端和襯底的第二端中間的第一端。第二超導(dǎo)金屬信號(hào)線的第二端定位成接近襯底的第二端的邊緣。第一超導(dǎo)金屬信號(hào)線和第二超導(dǎo)金屬信號(hào)線被配置為產(chǎn)生電容場(chǎng)。該實(shí)施例通過(guò)創(chuàng)建用于傳導(dǎo)信號(hào)的基于邊緣的電容場(chǎng)來(lái)改進(jìn)量子計(jì)算應(yīng)用中的芯片內(nèi)連接。基于邊緣的電容信號(hào)允許相鄰芯片彼此傳輸信號(hào),即使這些芯片是傳統(tǒng)上在芯片內(nèi)級(jí)別上不彼此連接的通常不兼容的技術(shù)的一部分。

4、在可與前述實(shí)施例結(jié)合的實(shí)施例中,第一超導(dǎo)金屬信號(hào)線的第二端和第二超導(dǎo)金屬信號(hào)線的第二端定位在從襯底的頂表面延伸、越過(guò)襯底的第二端的邊緣、以及越過(guò)襯底的第二端的側(cè)壁的路線中。通過(guò)路由信號(hào)。

5、根據(jù)本公開(kāi)的實(shí)施例,提供了一種制造量子計(jì)算裝置的方法。該方法包括形成芯片襯底。超導(dǎo)金屬的一個(gè)或多個(gè)信號(hào)線形成在第一芯片襯底的頂表面上,與第一芯片襯底的頂表面的邊緣接近或接觸。形成一第二晶片襯底。超導(dǎo)金屬的一個(gè)或多個(gè)信號(hào)線形成在第二芯片襯底的頂表面上,與第二芯片襯底的第二頂表面的邊緣接近或接觸。一個(gè)或多個(gè)第一信號(hào)線的第一遠(yuǎn)端定位在一個(gè)或多個(gè)第二信號(hào)線的第二遠(yuǎn)端附近。當(dāng)信號(hào)通過(guò)一個(gè)或多個(gè)第一信號(hào)線或一個(gè)或多個(gè)第二信號(hào)線時(shí),一個(gè)或多個(gè)第一信號(hào)線和一個(gè)或多個(gè)第二信號(hào)線形成基于電容的總線連接。該方法描述了對(duì)當(dāng)前制造方法的改進(jìn),因?yàn)槠渌椒ㄍǔ1辉O(shè)計(jì)用于電流連接,其產(chǎn)量是在切割芯片管芯之前測(cè)試的挑戰(zhàn)。直到芯片被切割之后,才能測(cè)試基于電流的線路中的不連續(xù)性和其它缺陷。由于信號(hào)線的完整性獨(dú)立于其它信號(hào)線,所以可以在芯片切割之前預(yù)先測(cè)試在上述實(shí)施例中形成的基于電容的信號(hào)線。

6、在可與前述實(shí)施例組合的實(shí)施例中,所述方法包含在所述一個(gè)或多個(gè)第一信號(hào)線上形成第一導(dǎo)電凸塊,且在所述一個(gè)或多個(gè)第二信號(hào)線上形成第二導(dǎo)電凸塊。第一導(dǎo)電凸塊和第二導(dǎo)電凸塊形成基于電容的總線連接。通常,凸塊僅用作導(dǎo)線或跡線的物理連接點(diǎn),或用作間隔特征以在不同材料層之間產(chǎn)生間隙。如可以理解的,本公開(kāi)的凸塊可以在提供基于邊緣的電容連接的同時(shí)提供作為與相鄰模塊的間隔物的雙重功能。

7、本文描述的技術(shù)可以以多種方式實(shí)現(xiàn)。下面參考以下附圖提供示例實(shí)施方式。

技術(shù)特征:

1.一種量子計(jì)算芯片裝置,包括:

2.根據(jù)權(quán)利要求1所述的量子計(jì)算芯片裝置,其中所述第一信號(hào)線的所述遠(yuǎn)端通過(guò)襯底材料與所述第一芯片的所述邊緣間隔開(kāi)。

3.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,其中所述第一信號(hào)線被定位在所述第一芯片的頂表面上、在所述第一芯片的邊緣之上、以及到所述第一轉(zhuǎn)接板的側(cè)壁配合表面上。

4.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括所述第一芯片的襯底中的溝槽,其中所述第一信號(hào)線嵌入在所述溝槽中。

5.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括在所述第一信號(hào)線的遠(yuǎn)端上并且與所述第一芯片的邊緣相鄰的電容器墊。

6.根據(jù)權(quán)利要求5所述的量子計(jì)算芯片裝置,其中所述電容器墊被嵌入在所述第一芯片的襯底中并且與所述第一芯片的所述邊緣間隔開(kāi)。

7.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括所述第一信號(hào)線的所述遠(yuǎn)端的正面,其中所述第一信號(hào)線的所述遠(yuǎn)端的所述正面通過(guò)所述第一芯片的側(cè)壁暴露。

8.根據(jù)權(quán)利要求7所述的量子計(jì)算芯片裝置,其中所述第一信號(hào)線的所述遠(yuǎn)端的所述正面與所述第一芯片的所述側(cè)壁齊平。

9.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括在所述第一芯片的側(cè)壁上的支座。

10.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括在所述第一芯片的頂表面上的凸塊。

11.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括第一凸塊,所述第一凸塊耦合到所述第一信號(hào)線,并且被布置成與位于所述第二信號(hào)線上的第二凸塊協(xié)作來(lái)提供電容。

12.根據(jù)前述權(quán)利要求中的任一項(xiàng)所述的量子計(jì)算芯片裝置,還包括耦合到所述第一信號(hào)線的金屬片,其中所述金屬片突出超過(guò)所述第一芯片的邊緣,并且被設(shè)置成與耦合到所述第二信號(hào)線的第二金屬片協(xié)作來(lái)提供電容。

13.一種量子計(jì)算芯片,包括:

14.根據(jù)權(quán)利要求13所述的量子計(jì)算芯片,其中所述第一超導(dǎo)金屬信號(hào)線的第二端和所述第二超導(dǎo)金屬信號(hào)線的第二端定位在從所述襯底的頂表面延伸、在所述襯底的第二端的邊緣之上延伸、以及在所述襯底的第二端的側(cè)壁之上延伸的路線中。

15.根據(jù)權(quán)利要求13到14中的任一項(xiàng)所述的量子計(jì)算芯片,其中所述第一超導(dǎo)金屬信號(hào)線的第二端和所述第二超導(dǎo)金屬信號(hào)線的第二端通過(guò)所述襯底的第二端暴露。

16.根據(jù)權(quán)利要求13到15中的任一項(xiàng)所述的量子計(jì)算芯片,其中所述第一超導(dǎo)金屬信號(hào)線和所述第二超導(dǎo)金屬信號(hào)線嵌入到所述襯底中。

17.根據(jù)權(quán)利要求13到16中的任一項(xiàng)所述的量子計(jì)算芯片,還包括位于所述襯底的所述第二端的側(cè)壁上的一個(gè)或多個(gè)支座。

18.根據(jù)權(quán)利要求17所述的量子計(jì)算芯片,其中所述一個(gè)或多個(gè)支架被配置為提供基于使用所述量子計(jì)算芯片的耦合中的目標(biāo)電容的間隔。

19.根據(jù)權(quán)利要求13到18中的任一項(xiàng)所述的量子計(jì)算芯片,還包括位于所述第一超導(dǎo)金屬信號(hào)線上的第一導(dǎo)電凸塊和位于所述第二超導(dǎo)金屬信號(hào)線上的第二導(dǎo)電凸塊,其中所述電容場(chǎng)在所述第一導(dǎo)電凸塊和所述第二導(dǎo)電凸塊之間形成。

20.根據(jù)權(quán)利要求13到19中的任一項(xiàng)所述的量子計(jì)算芯片,還包括耦合到所述第一超導(dǎo)金屬信號(hào)線和所述第二超導(dǎo)金屬信號(hào)線的第二端的金屬片,并且其中所述金屬片的一端突出超過(guò)所述襯底的第二端。

21.一種制造量子計(jì)算裝置的方法,包括:

22.根據(jù)權(quán)利要求21所述的方法,還包括在所述第一襯底中形成溝槽并且將所述超導(dǎo)金屬沉積到所述溝槽中,其中所述溝槽和沉積的超導(dǎo)金屬限定所述一個(gè)或多個(gè)第一信號(hào)線。

23.根據(jù)前述權(quán)利要求21至22中任一項(xiàng)所述的方法,還包括:

24.根據(jù)前述權(quán)利要求21至23中任一項(xiàng)所述的方法,還包括:

25.根據(jù)前述權(quán)利要求21至24中任一項(xiàng)所述的方法,還包括:

技術(shù)總結(jié)

一種量子計(jì)算芯片裝置提供基于邊緣的電容性芯片內(nèi)連接。第一芯片包括第一信號(hào)線,該第一信號(hào)線具有位于第一芯片邊緣附近或邊緣上的遠(yuǎn)端和位于遠(yuǎn)離第一芯片邊緣的近端。第二芯片包括第二信號(hào)線,該第二信號(hào)線具有位于第二芯片的邊緣附近或邊緣上的遠(yuǎn)端和位于遠(yuǎn)離第二芯片的邊緣的近端。第一信號(hào)線和第二信號(hào)線被配置為傳導(dǎo)信號(hào)。第二芯片的第二信號(hào)線被設(shè)置成與第一芯片的第一信號(hào)線對(duì)齊以形成電容性總線連接。

技術(shù)研發(fā)人員:M·庫(kù)馬夫,O·戴爾,J·庫(kù)特,D·亞伯拉罕

受保護(hù)的技術(shù)使用者:國(guó)際商業(yè)機(jī)器公司

技術(shù)研發(fā)日:

技術(shù)公布日:2025/4/28

- 還沒(méi)有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!