電源選擇開關電路及具有電源選擇開關電路的功率放大器模塊的制作方法

本發明涉及一種電源選擇開關電路及具有電源選擇開關電路的功率放大器模塊。

背景技術:

1、第五代蜂窩通信技術可與第四代蜂窩通信技術和長期演進(lte)技術共存,在一個通信終端系統中需要不同的通信方法和對應的功率放大器。

2、典型的通信終端系統可使用一個電源管理集成電路(pmic)和一個功率放大器。為了在一個通信終端系統中支持各種通信方法,可能期望大量的pmic,從而增加了通信終端系統的制造成本。

3、通過使用電源選擇開關,可使用少量pmic來驅動多個功率放大器;因此,可減少電源組件的數量,并且可降低通信終端的制造成本。

4、在實現電源選擇開關時,如果一對n型晶體管和p型晶體管用作開關核心,則p型晶體管的尺寸可被設計為較大,以減小晶體管對于高直流(dc)輸入電壓的導通電阻。隨著p型晶體管的尺寸增大,當電源選擇開關安裝在功率放大器模塊中時,p型晶體管占據的面積可能增大。因此,功率放大器模塊的尺寸和價格可能增加。

5、上述信息僅作為背景信息呈現,以幫助理解本公開。上述記載不應被解釋為這些內容屬于本公開的現有技術。

技術實現思路

1、提供本

技術實現要素:

以按照簡化的形式介紹所選擇的構思,并在以下具體實施方式中進一步描述這些構思。本發明內容既不意在明確所要求保護的主題的關鍵特征或必要特征,也不意在用于幫助確定所要求保護的主題的范圍。

2、在一個總體方面中,一種電源選擇開關電路被配置為選擇第一電源電壓和第二電源電壓中的任一者,并將所選擇的電源電壓供應給功率放大器,所述電源選擇開關電路包括:第一n型晶體管,被配置為響應于第一開關控制信號而導通,并且在導通時將所述第一電源電壓供應給所述功率放大器的電源端子,第一開關控制信號所述具有通過電荷泵送所述第一電源電壓生成的第一電壓;以及第二n型晶體管,被配置為響應于第二開關控制信號而導通,并且在導通時將所述第二電源電壓供應給所述功率放大器的所述電源端子,所述具有通過電荷泵送所述第二電源電壓生成的第二電壓的第二開關控制信號。

3、所述電源選擇開關電路還可包括:開關控制器,被配置為使用從外部輸入的第一位信號和第二位信號來生成所述第一開關控制信號和所述第二開關控制信號,使得所述第一n型晶體管和所述第二n型晶體管中的將要從截止狀態被導通的晶體管在延遲預定時間之后導通,并且所述第一n型晶體管和所述第二n型晶體管中的將要從導通狀態被截止的晶體管立即截止。所述第一n型晶體管可被配置為響應于具有低于所述第一電壓的第三電壓的所述第一開關控制信號而截止,并且所述第二n型晶體管可被配置為響應于具有低于所述第二電壓的第四電壓的所述第二開關控制信號而截止。

4、所述開關控制器可包括:邏輯電路,被配置為通過組合所述第一位信號和所述第二位信號來生成用于生成所述第一開關控制信號的第一邏輯信號和用于生成所述第二開關控制信號的第二邏輯信號;第一延遲電路,被配置為延遲所述第一邏輯信號以生成第一延遲信號;第二延遲電路,被配置為延遲所述第二邏輯信號以生成第二延遲信號;第一緩沖控制電路,被配置為響應于所述第一延遲信號而將所述第一電壓或所述第三電壓作為所述第一開關控制信號供應給所述第一n型晶體管的控制端子;以及第二緩沖控制電路,被配置為響應于所述第二延遲信號而將所述第二電壓或所述第四電壓作為所述第二開關控制信號供應給所述第二n型晶體管的控制端子。

5、所述第一位信號和所述第二位信號可具有0或1的值。所述邏輯電路可被配置為:當所述第一位信號和所述第二位信號均為1或均為0時,將所述第一邏輯信號和所述第二邏輯信號兩者設定為低電平,使得所述第一n型晶體管和所述第二n型晶體管均截止。

6、所述開關控制器還可包括:第一時鐘發生器,被配置為:響應于所述第一邏輯信號而操作,并且生成具有第五電壓和低于所述第五電壓的第六電壓的第一時鐘信號;第二時鐘發生器,被配置為:響應于所述第二邏輯信號而操作,并且生成具有所述第五電壓和所述第六電壓的第二時鐘信號;第一電荷泵電路,被配置為:響應于所述第一時鐘信號而通過以所述第五電壓對所述第一電源電壓進行電荷泵送來生成所述第一電壓,并且將所述第一電壓提供給所述第一緩沖控制電路;以及第二電荷泵電路,被配置為:響應于所述第二時鐘信號而通過以所述第五電壓對所述第二電源電壓進行電荷泵送來生成所述第二電壓,并且將所述第二電壓提供給所述第二緩沖控制電路。

7、所述第一邏輯信號和所述第二邏輯信號可分別具有高電平和低電平。所述第一時鐘發生器和所述第二時鐘發生器可分別在所述第一邏輯信號的高電平和所述第二邏輯信號的高電平下操作且在低電平下不操作。

8、所述邏輯電路可包括:與非門,被配置為接收所述第一位信號和所述第二位信號;第一與門,被配置為接收所述第一位信號和所述與非門的輸出,并且輸出所述第一邏輯信號;以及第二與門,被配置為接收所述第二位信號和所述與非門的輸出,并且輸出所述第二邏輯信號。

9、所述第一延遲電路可包括:第一延遲單元,被配置為延遲所述第一邏輯信號;以及第一與門,被配置為接收所述第一邏輯信號和通過所述第一延遲單元延遲的信號。所述第二延遲電路可包括:第二延遲單元,被配置為延遲所述第二邏輯信號;以及第二與門,被配置為接收所述第二邏輯信號和通過所述第二延遲單元延遲的信號。

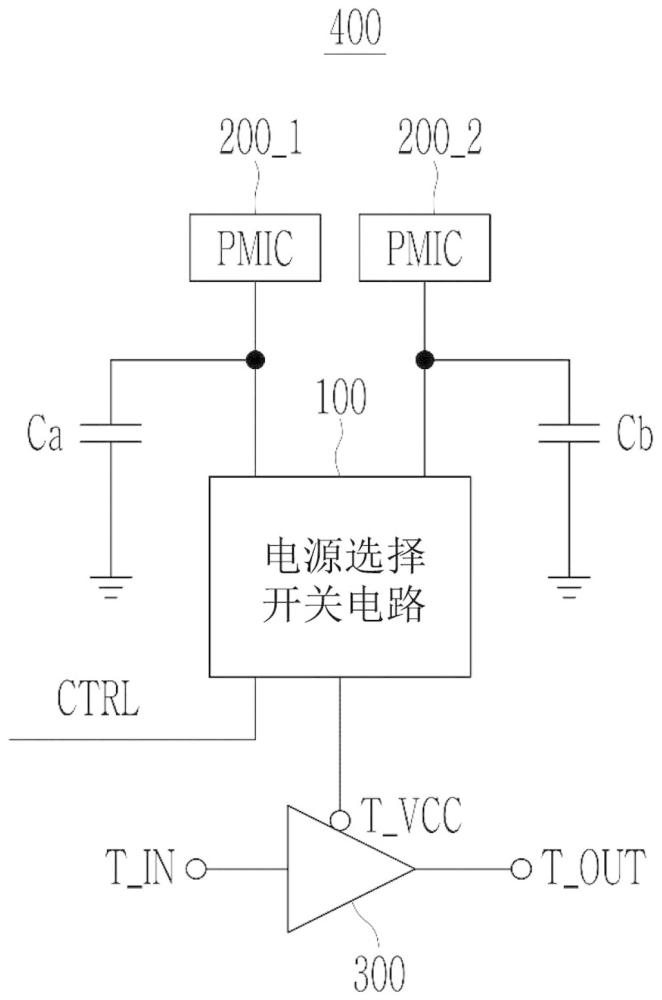

10、在另一總體方面,一種功率放大器模塊包括:如上所述的所述功率放大器和所述電源選擇開關電路。

11、在另一總體方面,一種功率放大器模塊包括:功率放大器,被配置為從電源端子接收電源電壓,并且放大輸入信號并輸出放大的信號;以及電源選擇開關電路,被配置為向所述電源端子提供從第一電源管理集成電路(ic)供應的第一電源電壓和從第二電源管理ic供應的第二電源電壓中的任一個電源電壓。所述電源選擇開關電路可包括:第一n型晶體管,被配置為具有連接到所述第一電源管理ic的第一端子、連接到所述電源端子的第二端子以及接收第一開關控制信號的控制端子,所述第一開關控制信號具有通過電荷泵送所述第一電源電壓生成的第一電壓;以及第二n型晶體管,被配置為具有連接到所述第二電源管理ic的第一端子、連接到所述電源端子的第二端子以及接收第二開關控制信號的控制端子,所述第二開關控制信號具有通過電荷泵送所述第二電源電壓生成的第二電壓。

12、所述電源選擇開關電路還可包括:開關控制器,被配置為生成所述第一開關控制信號和所述第二開關控制信號,使得所述第一n型晶體管在將要從截止狀態變為導通狀態的情況下在延遲預定時間之后導通,并且所述第二n型晶體管在將要從截止狀態變為導通狀態的情況下在延遲預定時間之后導通。

13、所述第一n型晶體管可被配置為響應于具有低于所述第一電壓的第三電壓的所述第一開關控制信號而截止,并且所述第二n型晶體管可被配置為響應于具有低于所述第二電壓的第四電壓的所述第二開關控制信號而截止。

14、所述開關控制器可包括:邏輯電路,被配置為通過組合從外部輸入的第一位信號和第二位信號來生成用于生成所述第一開關控制信號的第一邏輯信號和用于生成所述第二開關控制信號的第二邏輯信號;第一延遲電路,被配置為延遲所述第一邏輯信號以生成第一延遲信號;第二延遲電路,被配置為延遲所述第二邏輯信號以生成第二延遲信號;第一緩沖控制電路,被配置為響應于所述第一延遲信號而將所述第一電壓或所述第三電壓作為所述第一開關控制信號供應給所述第一n型晶體管的控制端子;以及第二緩沖控制電路,被配置為響應于所述第二延遲信號而將所述第二電壓或所述第四電壓作為所述第二開關控制信號供應給所述第二n型晶體管的控制端子。

15、所述第一位信號和所述第二位信號可具有0或1的值。所述邏輯電路被配置為:當所述第一位信號和所述第二位信號均為1或均為0時,將所述第一邏輯信號和所述第二邏輯信號兩者設定為低電平,使得所述第一n型晶體管和所述第二n型晶體管均截止。

16、所述開關控制器可包括:第一時鐘發生器,被配置為:響應于所述第一邏輯信號而操作,并且生成具有第五電壓和低于所述第五電壓的第六電壓的第一時鐘信號;第二時鐘發生器,被配置為:響應于所述第二邏輯信號而操作,并且生成具有所述第五電壓和所述第六電壓的第二時鐘信號;第一電荷泵電路,被配置為:響應于所述第一時鐘信號而通過以所述第五電壓對所述第一電源電壓進行電荷泵送來生成所述第一電壓,并且將所述第一電壓提供給所述第一緩沖控制電路;以及第二電荷泵電路,被配置為:響應于所述第二時鐘信號而通過以所述第五電壓對所述第二電源電壓進行電荷泵送來生成所述第二電壓,并且將所述第二電壓提供給所述第二緩沖控制電路。

17、所述第一n型晶體管可包括并聯連接的多個第三晶體管,所述第二n型晶體管可包括并聯連接的多個第四晶體管,并且所述多個第三晶體管和所述多個第四晶體管可以是n型晶體管。

18、通過下面的具體實施方式和附圖,其他特征和方面將是易于理解的。

- 還沒有人留言評論。精彩留言會獲得點贊!