電路和EEPROM的制作方法

本公開涉及閾值檢測器電路、mos晶體管老化對那些閾值檢測器電路的影響以及用于防止閾值電路受到mos晶體管老化的影響的技術的領域。

背景技術:

1、金屬氧化物半導體場效應晶體管(mos晶體管)是集成電路(ic)的常見組成部分,因此被廣泛使用。雖然mos晶體管因其多功能性和實用性而得到廣泛使用,但它也不是沒有問題,諸如老化的問題。老化是指mos晶體管的電氣性質隨著時間的推移逐漸降級,導致性能損失,并可能導致由mos晶體管形成的電路無法按預期運行。

2、mos晶體管的老化主要由四種機制造成,即,熱載流子注入(hci)、負偏置溫度不穩定性(nbti)、正偏置溫度不穩定性(pbti)和時間相關的電介質擊穿(tddb)。

3、當由于高電場而在晶體管的溝道中生成高能量電荷載流子(電子或空穴)時,發生hci。這些載流子可以克服能量勢壘并變得注入到柵極氧化物中,從而使得形成界面陷阱和氧化物電荷俘獲。hci在其中電場更顯著的短溝道晶體管中并且當柵極電壓(vg)接近漏極電壓的一半(vd/2)時尤其成問題。hci導致的影響包括閾值電壓移位、跨導降低和泄漏電流增加。

4、nbti是一種主要影響p溝道mos晶體管的降級機制。當晶體管受到負柵極-源極電壓(vgs)和提高的溫度時,發生這種情況。在這些狀況下,氫從二氧化硅(sio2)層中釋放出來,形成界面陷阱和氧化物電荷俘獲。nbti的影響包括閾值電壓移位(例如,閾值電壓增加、導致漏極電流減小)、跨導降低和泄漏電流增加(與hci類似)。

5、pbti是一種影響n溝道mos晶體管的降級機制。當晶體管受到非常正的柵極-源極電壓(vgs)和提高的溫度時,發生這種情況。就像nbti一樣,pbti也涉及氫從二氧化硅(sio2)層的釋放,從而導致界面陷阱和氧化物電荷俘獲。pbti的影響包括閾值電壓移位、跨導降低和泄漏電流增加。

6、tddb是指由于高電場和增加的溫度的存在而引起的mos晶體管中柵極氧化物逐漸降級。隨著時間的推移,柵極氧化物可能變弱,從而導致導通路徑的形成并最終導致電介質擊穿。tddb的影響包括柵極泄漏電流增加、閾值電壓移位和跨導降低。

7、eeprom(電可擦除可編程只讀存儲器)裝置特別容易受到mos晶體管老化的負面影響。這些存儲器裝置通常被指定為在寬電源(vdd)范圍內操作,通常在1.6v與5.5v之間。在這個范圍的上限(5.5v),mos晶體管可能經歷加速的老化,而在這個范圍的下限(1.6v),可能發生漏極電流水平的更高漂移。這些老化效應可能導致芯片漂移,并且在最壞的情況下,導致eeprom裝置無法正常工作。

8、在老化機制當中,nbti被識別為eeprom裝置最受關注的問題,尤其是對于p溝道mos晶體管。例如,在-6v的柵極-源極電壓(vgs)下操作1000小時之后,p溝道mos晶體管的閾值電壓(vt)可以從-0.8v增加到-1.0v,這顯著影響eeprom存儲器的性能和可靠性。

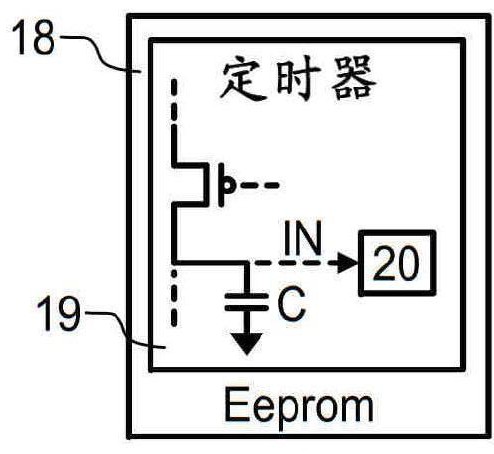

9、定時器電路也很容易受到mos晶體管老化的負面影響。此類定時器電路一般基于電容器的充電時間。電容器以一定的速率被充電,并且充電結束的檢測確定所經過的時間。但是,老化可能影響充電結束的檢測的閾值,這可能導致定時器操作不準確。

10、現在參考圖1,示出了用于檢測定時器電路中電容器充電的結束的現有技術檢測器10。到檢測器10的輸入in是跨電容器的電荷,并且一旦輸入in越過檢測器10的檢測閾值,檢測器的輸出out就會被斷言。定時器電路的“設定點”是電容器充電到的預定電壓閾值,在該設定點處檢測器10旨在斷言其輸出,指示充電過程的結束,電容器從其初始電壓充電到設定點所花費的時間確定了定時器電路旨在測量的時間間隔。

11、在檢測器10中的一個或多個mos晶體管發生有害老化之前,檢測器10按預期工作并且在設定點附近切換(即,其激活閾值接近設定點),這意味著它準確地檢測定時器電路中的電容器何時達到預定電壓閾值。這可以在示出檢測器10在mos晶體管老化之前的操作的圖2a-圖2b中觀察到,可以看出檢測器激活閾值接近或基本上處于設定點處。但是,在檢測器10中的一個或多個mos晶體管這樣老化之后,檢測器10現在可能在設定點以下切換。這可以在示出檢測器10在mos晶體管老化之后的操作的圖3a-圖3b中觀察到,其中可以看出檢測器激活閾值遠在設定點以下。結果,輸出out在輸入in(跨電容器的電壓)達到設定點之前被斷言,這意味著被測量的時間間隔現在比預期的短。

12、減輕定時器電路中mos晶體管老化的負面影響的一種方法是將定時器電路的供電電壓限制為老化影響被降低的值。這種限制可以幫助最小化用于給定時器中的電容器充電的(一個或多個)mos晶體管的老化。但是,如所述的,雖然較低的供電電壓使得mos晶體管老化速度變慢,但這種老化的影響(一旦發生老化)在較低的供電電壓下更為明顯。

13、另一種方法是將定時器電路設計為將以恒定電流充電的電容器與穩定的充電結束電壓檢測機制配對,以幫助維持一致的定時器操作。但是,這有幾個缺點,包括恒定電流充電和穩定電壓檢測系統汲取待機電流的事實,這可能影響裝置的整體功率效率,并且實施起來可能復雜且占用面積。還有,這種方法不能保證實現真正老化穩定的電壓檢測。檢測閾值中因老化而產生的波動仍可能發生,這潛在地影響定時器隨時間的性能和可靠性。

14、在某些應用中,eeprom被用于存儲要以特定間隔或在特定狀況下被訪問、修改或更新的數據。通過規定在發起下一個讀、寫或擦除操作之前已經過去適當的時間,可以利用定時器來控制這些過程。例如,定時器可以被用于控制eeprom寫周期的定時,從而提供在嘗試寫操作之前經過所需的最小時間。

15、由于eeprom和定時器兩者均容易受到mos晶體管老化的影響,因此這些組件的性能和可靠性可以是有聯系的。因此,老化引起的mos晶體管降級不僅可能影響eeprom的直接操作,而且還可能影響負責控制其訪問和修改的定時器的準確運行。

16、考慮到用于解決定時器電路中的mos晶體管老化的上述已知解決方案出于所述原因是不夠的,需要以產生不受mos晶體管老化影響的定時器電路為目的的進一步開發。

技術實現思路

1、本文公開了一種電路,包括檢測器電路,包括:第一檢測器,被配置為接收輸入信號并生成指示輸入信號已達到第一激活閾值的第一檢測器輸出信號;以及第二檢測器,被配置為接收輸入信號,并且當由第一檢測器輸出信號啟用時,生成指示輸入信號已達到第二激活閾值的第二檢測器輸出信號。邏輯電路被配置為對第一和第二檢測器輸出信號執行邏輯運算,以生成指示輸入信號已達到等于第二激活閾值的電壓的輸出。

2、由于第一檢測器中至少一個mos晶體管的老化,第二激活閾值可以大于第一激活閾值。

3、等于第二激活閾值的電壓可以是跨定時器的電容器的期望電壓電平。

4、邏輯電路可以是與門,該與門被配置為對第一和第二檢測器輸出信號執行邏輯與運算以斷言指示輸入信號已達到等于第二激活閾值的電壓的輸出。

5、本文提供了一種eeprom,包括:定時器,被配置為對電容器進行充電和放電,從而對操作進行計時;以及如上所述的檢測器電路,其中跨電容器的電壓是由檢測器電路的第一檢測器和第二檢測器接收的輸入信號。

6、定時電路可以被配置為響應于輸入信號的斷言而對電容器充電。在這種情況下,檢測器電路還可以包括老化減輕電路,其中第一反相器的輸入端被連接成接收第一檢測器輸出并提供第一反相器輸出。老化減輕電路可以包括第二檢測器,其中第二檢測器包括第一p溝道晶體管和第一n溝道晶體管,該第一p溝道晶體管具有連接成接收第一反相器輸出的源極和體塊、連接到第一抽頭節點的漏極以及連接成接收電容器上的電壓的柵極,該第一n溝道晶體管具有連接到第一抽頭節點的漏極、連接到地的源極以及連接成接收參考電壓的柵極。老化減輕電路還可以包括第二p溝道晶體管和第二n溝道晶體管,該第二p溝道晶體管具有連接到供電電壓的源極、連接到第二抽頭節點的漏極以及連接成接收第一反相器輸出的柵極,該第二n溝道晶體管具有連接到第二抽頭節點的漏極、連接到地的源極以及連接成接收參考電壓的柵極。邏輯電路可以通過接收來自第一和第二抽頭節點的輸入并生成輸出信號以及基于此對電容器進行放電來對第一和第二檢測器輸出執行邏輯運算。

7、第一檢測器可以包括第三p溝道晶體管和第三n溝道晶體管,該第三p溝道晶體管具有連接到供電電壓的源極、連接到第三抽頭節點的漏極以及連接成接收電容器上的電壓的柵極,該第三n溝道晶體管具有連接到第三抽頭節點的漏極、連接到地的源極以及連接成接收參考電壓的柵極。

8、第一反相器可以將其輸入端連接到第三抽頭節點并將其輸出端連接到第二p溝道晶體管的柵極。

9、邏輯電路可以包括或門、第一與非門和第二與非門,該或門具有連接到第二抽頭節點的第一輸入端、連接到第一抽頭節點的第二輸入端以及輸出端,該第一與非門具有連接到或門的輸出端的第一輸入端、連接到預輸出節點的第二輸入端以及輸出端,該第二與非門具有連接到第一與非門的輸出端的第一輸入端、連接成接收輸入信號的第二輸入端以及連接到預輸出節點的輸出端。

10、邏輯電路還可以包括第三與非門,該第三與非門具有連接成接收輸入信號的第一輸入端、連接到預輸出節點的第二輸入端以及連接到定時電路的輸出端。

11、定時電路可以被配置為響應于輸入信號的斷言而對電容器進行充電。在這種情況下,檢測器電路還可以包括具有反相器電路和第二檢測器的老化減輕電路,該反相器電路將其輸入端連接成接收第一檢測器輸出并提供第一反相器輸出。第二檢測器可以包括第一p溝道晶體管和第一n溝道晶體管,該第一p溝道晶體管具有連接成接收第一反相器輸出的源極和體塊、連接到第一抽頭節點的漏極以及連接成接收電容器上的電壓的柵極,該第一n溝道晶體管具有連接到第一抽頭節點的漏極、連接到地的源極以及連接成接收參考電壓的柵極。老化減輕電路還可以包括第二p溝道晶體管,該第二p溝道晶體管具有連接到供電電壓的源極、連接到第一抽頭節點的漏極以及連接成接收第一反相器輸出的柵極。邏輯電路可以通過從第一抽頭節點接收輸入并生成輸出信號以及基于此對電容器進行放電來對第一和第二檢測器輸出執行邏輯運算。

12、第一檢測器可以包括第三p溝道晶體管和第三n溝道晶體管,該第三p溝道晶體管具有連接到供電電壓的源極、連接到第二抽頭節點的漏極以及連接成接收電容器上的電壓的柵極,該第三n溝道晶體管具有連接到第二抽頭節點的漏極、連接到地的源極以及連接成接收參考電壓的柵極。

13、反相器電路可以包括連接在第二抽頭節點與第二p溝道晶體管的柵極之間的一系列級聯的反相器。

- 還沒有人留言評論。精彩留言會獲得點贊!