高速電平轉(zhuǎn)換電路以及芯片的制作方法

本發(fā)明涉及集成電路領(lǐng)域,具體地涉及一種高速電平轉(zhuǎn)換電路以及芯片。

背景技術(shù):

1、電平轉(zhuǎn)換電路被廣泛應(yīng)用于多電源電壓域的混合信號(hào)電路中。在混合信號(hào)設(shè)計(jì)領(lǐng)域,為了降低電路的功耗并提升電路的工作速度,往往采用混合電壓域設(shè)計(jì)。其中,關(guān)鍵性能模塊采用高壓設(shè)計(jì),高速低功耗模塊采用低壓設(shè)計(jì),而在兩者的接口處,需要大量的電平轉(zhuǎn)換電路,因此如何實(shí)現(xiàn)高速低成本的電平轉(zhuǎn)換電路一直都是一個(gè)被廣泛關(guān)注的問題。

2、電壓轉(zhuǎn)換器電路有兩種基本結(jié)構(gòu),圖1a與圖1b為現(xiàn)有設(shè)計(jì)一,其中圖1a為電路,圖1b為信號(hào)波形圖。圖1a所示的電路100包括一個(gè)輸入反相器電路110、基于交叉耦合結(jié)構(gòu)的電平轉(zhuǎn)換電路120、以及一個(gè)反相輸出緩沖器電路130。其中,輸入反相器電路110工作在1.8v的低電壓域,所述電平轉(zhuǎn)換電路120和反相輸出緩沖器電路130工作在5v的高電壓域。輸入反相器電路110對(duì)輸入信號(hào)進(jìn)行反轉(zhuǎn),以提供反相輸入信號(hào)。電平轉(zhuǎn)換電路120包括:由pmos管123、124組成的交叉耦合結(jié)構(gòu)作為上拉網(wǎng)絡(luò),以將輸出信號(hào)上拉到高電壓;由nmos管121、122組成的下拉網(wǎng)絡(luò),以將輸出信號(hào)下拉到地,基于交叉耦合的上拉網(wǎng)絡(luò)具有正反饋特性,強(qiáng)化了q1和q2的電壓差異,從而更快地進(jìn)行電平切換。工作時(shí)的信號(hào)波形如圖1b所示,在輸入信號(hào) vil上升沿期間,nmos管121打開,nmos管122關(guān)斷。此時(shí),q1處電壓逐漸降低,pmos管124逐漸打開,將q2拉向高電源電壓( vddh),這有助于關(guān)閉pmos管123,導(dǎo)致q1放電更快;反相輸出緩沖器電路130從低電平到高電平的上拉速度也就更快。這種架構(gòu)在待機(jī)模式下具有非常低的功耗,因?yàn)閮蓚€(gè)電路分支都不消耗靜態(tài)功率。然而,當(dāng)?shù)碗娫措妷海? vddl)較低時(shí),下拉晶體管nmos?121、122過驅(qū)動(dòng)電壓較低,無法輕松克服上拉晶體管pmos?123、124,因此為了提升下拉網(wǎng)絡(luò),nmos管121、122的尺寸往往較大,降低了整體效率,帶來了更大的延遲和功耗。

3、圖2a與圖2b為現(xiàn)有設(shè)計(jì)二,其中圖2a為電路,圖2b為信號(hào)波形圖。圖2a所示的電路200包括一個(gè)輸入反相器電路210、基于電流鏡結(jié)構(gòu)的電平轉(zhuǎn)換電路220、以及級(jí)聯(lián)輸出緩沖器電路230。其中,輸入反相器電路210工作在1.8v的低電壓域,所述電平轉(zhuǎn)換電路220和級(jí)聯(lián)輸出緩沖器電路230工作在5v的高電壓域。輸入反相器電路210對(duì)輸入信號(hào)進(jìn)行反轉(zhuǎn),以提供反相輸入信號(hào)。所述電平轉(zhuǎn)換電路220包括:由pmos管223、224組成的電流鏡結(jié)構(gòu)作為上拉網(wǎng)絡(luò),將輸出信號(hào)上拉到高電壓;由nmos管221、222組成的下拉網(wǎng)絡(luò),將輸出信號(hào)下拉到地。最終電平轉(zhuǎn)換器的輸出信號(hào)通過級(jí)聯(lián)輸出緩沖器電路223輸出。工作時(shí)的信號(hào)波形如圖2b所示,在輸入信號(hào) vil上升沿期間,nmos管221打開,nmos管222關(guān)斷。此時(shí),q1處電壓逐漸降低,pmos管224逐漸打開,將q2拉向高電源電壓( vddh),最終經(jīng)過級(jí)聯(lián)輸出緩沖器223后將低電壓轉(zhuǎn)換為高電壓。這種電路結(jié)構(gòu)中,雖然下拉網(wǎng)絡(luò)和上拉網(wǎng)絡(luò)不存在競(jìng)爭(zhēng)關(guān)系,但是上下拉網(wǎng)絡(luò)之間以及電路的左右分支之間幾乎沒有再生相互作用,因此轉(zhuǎn)換速度較低。此外,它具有相對(duì)較大的靜態(tài)功率,這主要是由于根據(jù)輸入狀態(tài)其中一個(gè)電路支路存在靜態(tài)電流。

技術(shù)實(shí)現(xiàn)思路

1、本發(fā)明的目的是提供一種高速電平轉(zhuǎn)換電路以及芯片,其可提高電平轉(zhuǎn)換電路的下拉網(wǎng)絡(luò)的過驅(qū)動(dòng)電壓,在不犧牲上拉網(wǎng)絡(luò)強(qiáng)度的同時(shí),增加了下拉網(wǎng)絡(luò)強(qiáng)度,實(shí)現(xiàn)了高速的電平轉(zhuǎn)換,與現(xiàn)有設(shè)計(jì)相比,在電路尺寸和負(fù)載大小相當(dāng)?shù)那闆r下,具有高速、寬電平轉(zhuǎn)換范圍的特點(diǎn)。

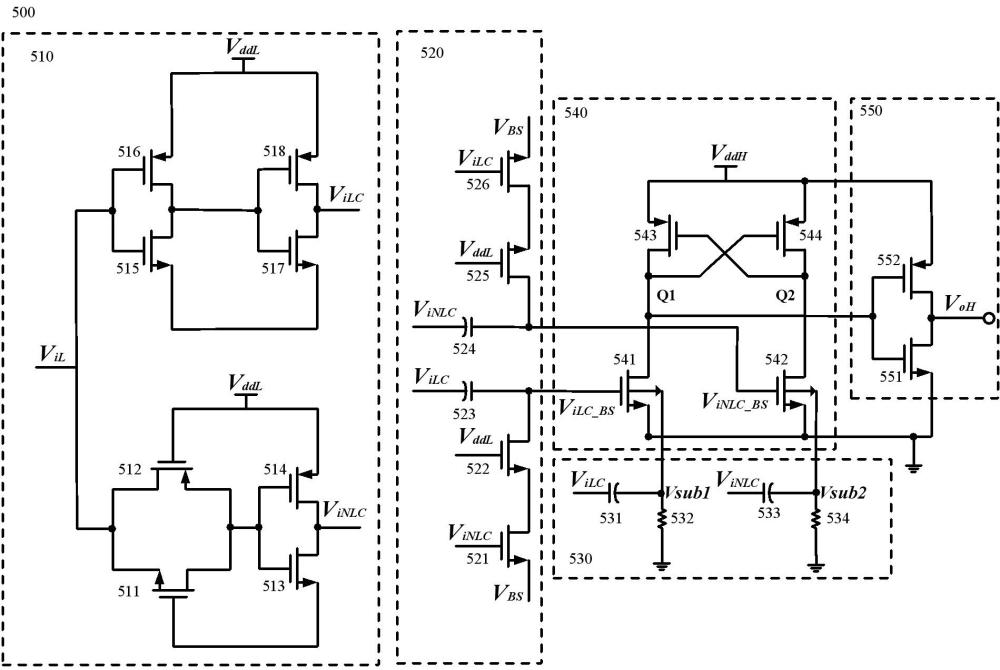

2、為了實(shí)現(xiàn)上述目的,本發(fā)明第一方面提供一種高速電平轉(zhuǎn)換電路,所述高速電平轉(zhuǎn)換電路包括:同反相信號(hào)輸出電路、電平升壓電路、襯底電壓調(diào)節(jié)電路、基于交叉耦合結(jié)構(gòu)的電平轉(zhuǎn)換電路以及反相輸出緩沖器電路,其中,所述同反相信號(hào)輸出電路用于在輸入信號(hào)的上升沿期間,輸出與輸入信號(hào)同相的第一輸出信號(hào)以及與所述輸入信號(hào)反相的第二輸出信號(hào);所述電平升壓電路用于響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),進(jìn)入充電狀態(tài)以及將所述第一輸出信號(hào)抬升 vbs,其中,所述 vbs為用于控制所述電平升壓電路的外部偏置電壓;所述襯底電壓調(diào)節(jié)電路用于響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),產(chǎn)生正向的脈沖微分波形以使得所述電平轉(zhuǎn)換電路中的第一nmos管快速開啟,以及產(chǎn)生負(fù)向的脈沖微分波形以使得所述電平轉(zhuǎn)換電路中的第二nmos管快速關(guān)閉,其中,所述 vbs小于所述第一nmos管與所述第二nmos管的閾值電壓;所述電平轉(zhuǎn)換電路用于響應(yīng)于所述第一nmos管快速開啟且所述第二nmos管快速關(guān)閉,將輸出電壓拉向低電平0;以及所述反相輸出緩沖器電路用于對(duì)所述輸出電壓進(jìn)行反相,以將低電平0轉(zhuǎn)換為目標(biāo)電平。

3、優(yōu)選地,所述同反相信號(hào)輸出電路用于在輸入信號(hào)的下降沿期間,輸出與輸入信號(hào)同相的第一輸出信號(hào)以及與所述輸入信號(hào)反相的第二輸出信號(hào);所述電平升壓電路用于響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),進(jìn)入充電狀態(tài)以及將所述第二輸出信號(hào)抬升 vbs;所述襯底電壓調(diào)節(jié)電路用于響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),產(chǎn)生正向的脈沖微分波形以使得所述電平轉(zhuǎn)換電路中的第二nmos管快速開啟,以及產(chǎn)生負(fù)向的脈沖微分波形以使得所述電平轉(zhuǎn)換電路中的第一nmos管快速關(guān)閉;所述電平轉(zhuǎn)換電路用于響應(yīng)于所述第二nmos管快速開啟且所述第一nmos管快速關(guān)閉,將輸出電壓拉向所述目標(biāo)電平;以及所述反相輸出緩沖器電路用于對(duì)所述輸出電壓進(jìn)行反相,以將所述目標(biāo)電平轉(zhuǎn)換為低電平0。

4、優(yōu)選地,所述同反相信號(hào)輸出電路為時(shí)鐘沿調(diào)節(jié)電路,所述時(shí)鐘沿調(diào)節(jié)電路還用于將所述第一輸出信號(hào)的上升沿與所述第二輸出信號(hào)的下降沿的中心點(diǎn)對(duì)齊,以及將所述第一輸出信號(hào)的下降沿與所述第二輸出信號(hào)的上升沿的中心點(diǎn)對(duì)齊。

5、優(yōu)選地,所述電平升壓電路包括:第一電路,用于在輸入信號(hào)的上升沿期間,響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),進(jìn)入充電狀態(tài),或者,在輸入信號(hào)的下降沿期間,響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),將所述第二輸出信號(hào)抬升 vbs;以及第二電路,用于在輸入信號(hào)的上升沿期間,響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),將所述第一輸出信號(hào)抬升 vbs,或者,在輸入信號(hào)的下降沿期間,響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),進(jìn)入充電狀態(tài)?。

6、優(yōu)選地,所述第一電路包括:第三nmos管,所述第三nmos管的柵極與所述第一輸出信號(hào)相連、所述第三nmos管的源極與所述外部偏置電壓相連;第一電容,所述第一電容的第一端與所述第三nmos管的漏極相連,所述第一電容的第二端與所述第二輸出信號(hào)相連,所述第二電路包括:第四nmos管,所述第四nmos管的柵極與所述第二輸出信號(hào)相連、所述第四nmos管的源極與所述外部偏置電壓相連;第二電容,第一端與所述第四nmos管的漏極相連,第二端與所述第一輸出信號(hào)相連。

7、優(yōu)選地,所述第一電路還包括:第五nmos管,所述第五nmos管的源極與所述第三nmos管的漏極相連,所述第五nmos管的漏極與所述第一電容的第一端相連,所述第二電路還包括:第六nmos管,所述第六nmos管的源極與所述第四nmos管的漏極相連,所述第六nmos管的漏極與所述第二電容的第一端相連。

8、優(yōu)選地,所述第一電路還包括:第一電阻,所述第一電阻的第一端與所述第三nmos管的漏極相連,所述第一電阻的第二端與所述第一電容的第一端相連,所述第二電路還包括:第二電阻,所述第二電阻的第一端與所述第四nmos管的漏極相連,所述第二電阻的第二端與所述第二電容的第一端相連。

9、優(yōu)選地,所述第二電容的第一端與所述電平轉(zhuǎn)換電路中的第一nmos管的柵極相連;所述第一電容的第一端與所述電平轉(zhuǎn)換電路中的第二nmos管的柵極相連。

10、優(yōu)選地,所述襯底電壓調(diào)節(jié)電路包括:第一微分支路,所述第一微分支路的輸入端與所述第一輸出信號(hào)相連,所述第一微分支路的輸出端與所述電平轉(zhuǎn)換電路中的第一nmos管的襯底相連;以及第二微分支路,所述第二微分支路的輸入端與所述第二輸出信號(hào)相連,所述第二微分支路的輸出端與所述電平轉(zhuǎn)換電路中的第二nmos管的襯底相連。

11、通過上述技術(shù)方案,本發(fā)明創(chuàng)造性地在所述高速電平轉(zhuǎn)換電路中設(shè)置同反相信號(hào)輸出電路、電平升壓電路、襯底電壓調(diào)節(jié)電路、基于交叉耦合結(jié)構(gòu)的電平轉(zhuǎn)換電路以及反相輸出緩沖器電路,其中,所述同反相信號(hào)輸出電路用于在輸入信號(hào)的上升沿期間,輸出與輸入信號(hào)同相的第一輸出信號(hào)以及與所述輸入信號(hào)反相的第二輸出信號(hào);所述電平升壓電路用于響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),進(jìn)入充電狀態(tài)以及將所述第一輸出信號(hào)抬升 vbs,其中,所述 vbs為用于控制所述電平升壓電路的外部偏置電壓;所述襯底電壓調(diào)節(jié)電路用于響應(yīng)于所述第一輸出信號(hào)與所述第二輸出信號(hào),產(chǎn)生正向的脈沖微分波形以使得所述電平轉(zhuǎn)換電路中的第一nmos管快速開啟,以及產(chǎn)生負(fù)向的脈沖微分波形以使得所述電平轉(zhuǎn)換電路中的第二nmos管快速關(guān)閉,其中,所述 vbs小于所述第一nmos管與所述第二nmos管的閾值電壓;所述電平轉(zhuǎn)換電路用于響應(yīng)于所述第一nmos管快速開啟且所述第二nmos管快速關(guān)閉,將輸出電壓拉向低電平0;以及所述反相輸出緩沖器電路用于對(duì)所述輸出電壓進(jìn)行反相,以將低電平0轉(zhuǎn)換為目標(biāo)電平。由此,本發(fā)明利用輔助的電平升壓電路和襯底電壓調(diào)節(jié)電路來提高電平轉(zhuǎn)換電路的下拉網(wǎng)絡(luò)的過驅(qū)動(dòng)電壓,在不犧牲上拉網(wǎng)絡(luò)強(qiáng)度的同時(shí),增加了下拉網(wǎng)絡(luò)強(qiáng)度,實(shí)現(xiàn)了高速的電平轉(zhuǎn)換,與現(xiàn)有設(shè)計(jì)相比,在電路尺寸和負(fù)載大小相當(dāng)?shù)那闆r下,具有高速、寬電平轉(zhuǎn)換范圍的特點(diǎn)。

12、本發(fā)明第二方面提供一種芯片,所述芯片包括所述的高速電平轉(zhuǎn)換電路。

13、本發(fā)明的其它特征和優(yōu)點(diǎn)將在隨后的具體實(shí)施方式部分予以詳細(xì)說明。

- 還沒有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!