半導體裝置背側配電網絡結構及其制造方法與流程

本公開大體涉及用于實施半導體封裝或芯片封裝的方法、系統及設備。

背景技術:

1、在現有半導體裝置中,配電網絡(例如,前側配電網絡)通常定位于頂部金屬層上的襯底的前側上。然后,電力從定位于頂部金屬層上的配電網絡傳輸到定位于金屬層下方的前道工藝有源裝置。然而,到前道工藝有源裝置的此電力傳輸路徑具有幾個問題。電流在到達前道工藝有源裝置之前必須行進通過的頂部金屬層會導致顯著的電壓降,也稱為ir降。隨著ir降增加,沿著穿過頂部金屬層的電流路徑浪費大量電力。另外,穿過頂部金屬層的長傳輸路徑難以維持電力完整性。此外,電源軌及/或電源線必須在頂部金屬層內與信號線并排放置。將電源軌及/或電源線與信號線并排放置限制半導體可減小的大小,這是因為單元大小減小受到每一單元內的電源軌及/或電源線的大小的限制。在一些情況下,使電力線與信號線并排進一步導致信號線內的干擾。

2、因此,需要更穩健且可擴展的解決方案來實施半導體封裝及芯片封裝。因此,提供用于實施包含半導體裝置中的背側配電網絡的半導體封裝或芯片封裝的方法、系統及設備。

技術實現思路

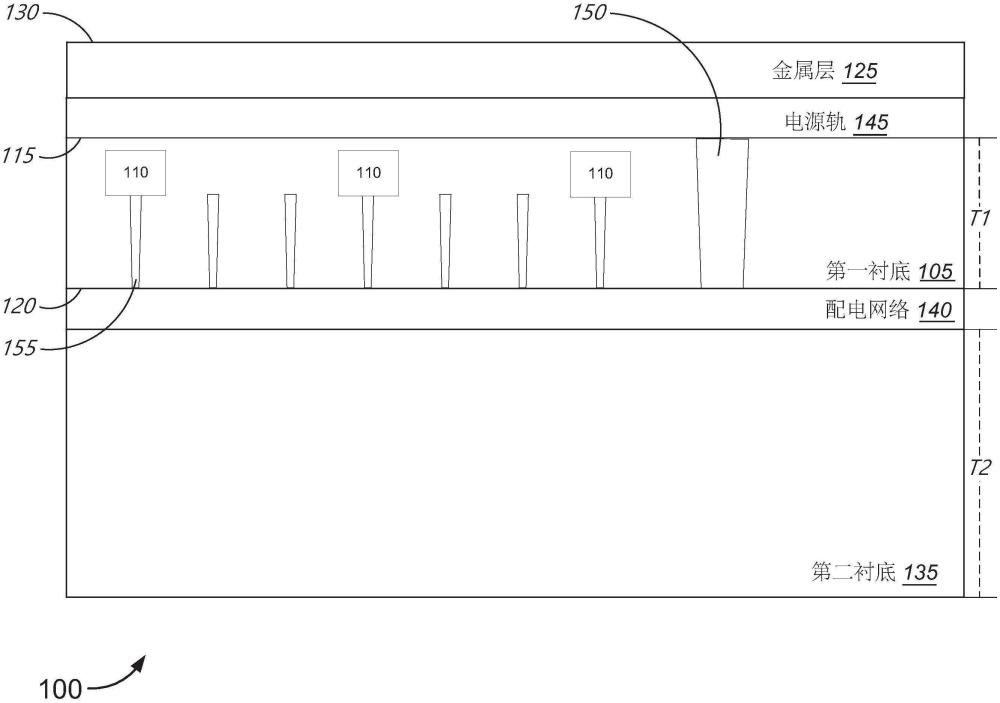

1、在一個方面中,本公開涉及一種設備,其包括:第一襯底,其包括經配置以接收電壓的第一裝置、安置在所述第一襯底的前面上的第一側及安置在所述第一襯底的背面上的第二側;第二襯底,所述第二襯底經配置以支撐所述第一襯底;及配電網絡,其安置在所述第一襯底的所述第二側與所述第二襯底之間的界面處。

2、在另一方面中,本公開涉及一種制造半導體裝置的背側配電網絡的方法,所述方法包括:形成包括經配置以接收電壓的裝置的第一襯底或第二襯底中的至少一者,其中所述第二襯底經配置以支撐所述第一襯底;及形成配電網絡,所述配電網絡經配置以安置在所述第一襯底與所述第二襯底之間的界面處。

3、在另一方面中,本公開涉及一種半導體裝置,其包括:第一襯底,其包括經配置以接收電壓的裝置;金屬層,其耦合到所述第一襯底的第一側;第二襯底,其耦合到所述第一襯底的與所述金屬層及所述第一側相對的第二側,所述第二襯底經配置以支撐所述第一襯底;及配電網絡,其安置在所述第一襯底的所述第二側與所述第二襯底之間。

技術特征:

1.一種設備,其包括:

2.根據權利要求1所述的設備,其中所述第一襯底包括單晶硅,并且所述第二襯底包括單晶硅、多晶硅、碳化硅、玻璃、藍寶石或砷化鎵。

3.根據權利要求1所述的設備,其中經配置以接收所述電壓的所述第一裝置包括晶體管。

4.根據權利要求1所述的設備,其中所述配電網絡直接耦合到所述第一襯底的所述第二側及所述第二襯底。

5.根據權利要求1所述的設備,其中所述第一襯底進一步包括:

6.根據權利要求5所述的設備,其中所述第一連接器的第一直徑與所述第二連接器的第二直徑的比在約3:1與20:1之間。

7.根據權利要求5所述的設備,其中所述第一連接器或所述第二連接器中的至少一者包括通孔或溝槽。

8.根據權利要求1所述的設備,其中所述第一襯底的第一厚度與所述第二襯底的第二厚度的比在約1:200與1:10之間。

9.根據權利要求1所述的設備,其進一步包括:

10.根據權利要求9所述的設備,其中所述第三襯底進一步包括:

11.根據權利要求1所述的設備,其中所述第二襯底進一步包括經配置以提供非易失性存儲器的第二裝置。

12.根據權利要求1所述的設備,其中所述第一襯底進一步包括朝向所述第一襯底的所述第二側的電路,其中所述電路經配置以控制電流。

13.一種制造半導體裝置的背側配電網絡的方法,所述方法包括:

14.根據權利要求13所述的方法,其中形成安置在所述第一襯底與所述第二襯底之間的所述界面處的所述配電網絡包括在所述第一襯底的背側上形成所述配電網絡。

15.根據權利要求14所述的方法,其中一旦在所述第一襯底上形成所述配電網絡,所述方法進一步包括將所述第一襯底接合到所述第二襯底。

16.根據權利要求13所述的方法,其中形成安置在所述第一襯底與所述第二襯底之間的界面處的所述配電網絡包括在所述第二襯底上形成所述配電網絡。

17.根據權利要求16所述的方法,其中一旦在所述第二襯底上形成所述配電網絡,所述方法進一步包括將所述第一襯底接合到所述第二襯底。

18.根據權利要求13所述的方法,其中形成安置在所述第一襯底與所述第二襯底之間的界面處的所述配電網絡包括形成第三襯底及在所述第三襯底上形成所述配電網絡,其中所述第三襯底進一步包括經配置以將所述第一襯底的所述裝置與所述配電網絡耦合的連接器。

19.根據權利要求18所述的方法,其中一旦在所述第三襯底上形成所述配電網絡,所述方法進一步包括將所述第一襯底接合到所述第三襯底并且將所述第二襯底接合到所述第三襯底,其中所述配電網絡在所述第二襯底與所述第三襯底之間。

20.一種半導體裝置,其包括:

技術總結

本公開涉及半導體裝置背側配電網絡結構及其制造方法。提供用于實施半導體封裝或芯片封裝的新穎工具及技術,并且更具體地說,提供用于實施包含背側配電網絡的半導體封裝或芯片封裝的方法、系統及設備。在各種實施例中,一種設備包含:第一襯底,其包括經配置以接收電壓的裝置及定位在所述第一襯底的前側上的第一側及經安置在所述第一襯底的背側上的第二側;第二襯底,所述第二襯底經配置以支撐所述第一襯底;及配電網絡,其經定位在所述第一襯底的所述第二側與所述第二襯底之間的界面處。

技術研發人員:趙子群,李曉明,劉清

受保護的技術使用者:安華高科技股份有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!