一種FGPA中CPHY信號的發送系統的制作方法

本文涉及電子電路技術,尤指一種fgpa中cphy信號的發送系統。

背景技術:

1、fpga(field-programmable?gate?array,現場可編程邏輯陣列)是一種靈活的半定制電路芯片,因其多功能性被譽為“萬能芯片”。隨著移動技術的發展,攝像頭到顯示屏的視頻信息傳輸需求得到較大的增長,需要在低頻低速介質中實現更高帶寬的通信,cphy(converged?phy,統一物理層)是一個較好的解決方案。

2、cphy是由mipi(mobile?industry?processor?interface,移動行業處理器接口)聯盟定義的物理層接口標準,專為移動設備中的高速數據傳輸而設計,主要用于連接攝像頭傳感器和移動設備的處理器。cphy接口支持多種數據傳輸速率,并能根據應用場景進行調整。這種接口能在保持低功耗的同時實現高數據傳輸速率,非常適合現代移動設備中圖像和視頻數據的傳輸需求。因此,確保cphy與fpga之間的兼容性,以滿足移動設備對高效圖像和視頻數據處理的需求,是一個亟待解決的技術問題。

技術實現思路

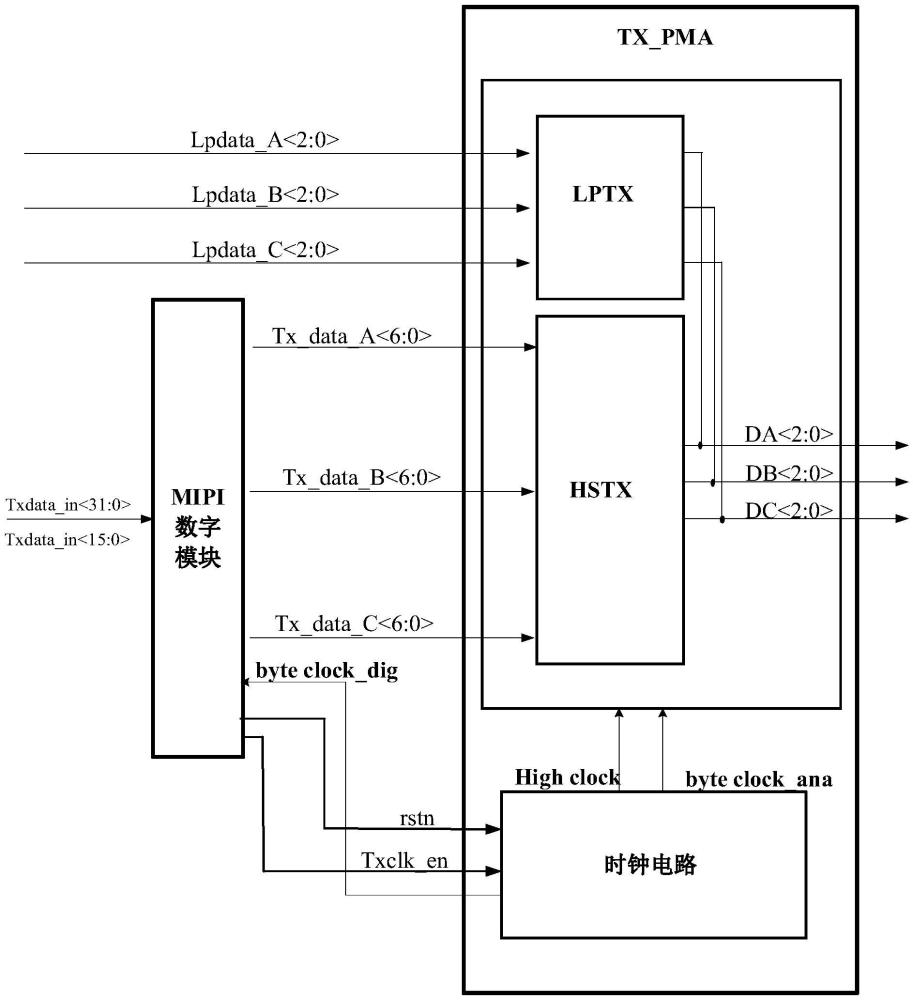

1、本申請實施例提供一種fgpa中cphy信號的發送系統,包括mipi數字模塊和hstx;其中:

2、所述mipi數字模塊,用于將fpga輸出的數據轉換為3路7位寬數據并輸出;

3、所述hstx包括:

4、3個數據通路,其中每個數據通路用于將各自對應的1路7位寬數據轉換為1位寬數據;

5、3線編碼器,與所述3個數據通路相連,用于對3個數據通路輸出的數字信號進行編碼,得到驅動信號;

6、驅動器,與3線編碼器相連,用于將所述驅動信號轉換為3路模擬信號,以便在信道進行傳輸。

7、本申請實施例,利用mipi數字模塊將fpga輸出的數據轉換為3路7位寬數據并輸出,再利用3個數據通路將各自對應的1路7位寬數據轉換為1位寬數據,通過3線編碼器對3個數據通路輸出的數字信號進行編碼,得到驅動信號,利用驅動器將所述驅動信號轉換為3路模擬信號,以便在信道進行傳輸,實現cphy與fpga之間數據傳輸的兼容性,滿足移動設備對高效圖像和視頻數據處理的需求。

8、本申請的其它特征和優點將在隨后的說明書中闡述,并且,部分地從說明書中變得顯而易見,或者通過實施本申請而了解。本申請的其他優點可通過在說明書以及附圖中所描述的方案來實現和獲得。

技術特征:

1.一種fgpa中cphy信號的發送系統,包括mipi數字模塊和hstx;其中:

2.根據權利要求1所述的系統,其特征在于:

3.根據權利要求2所述的系統,其特征在于:

4.根據權利要求2所述的系統,其特征在于,所述系統還包括:

5.根據權利要求4所述的系統,其特征在于:

6.根據權利要求2所述的系統,其特征在于,所述系統還包括:

7.根據權利要求6所述的系統,其特征在于,所述時鐘電路包括:

8.根據權利要求7所述的系統,其特征在于,所述時鐘電路還包括時鐘使能同步模塊和時鐘和復位同步模塊中的至少一個,其中:

9.根據權利要求8所述的系統,其特征在于:

10.根據權利要求7至9任一項所述的系統,其特征在于,所述時鐘電路還包括:

11.根據權利要求10所述的系統,其特征在于,所述初始時鐘模塊包括:

12.根據權利要求8所述的系統,其特征在于,所述系統還包括:

技術總結

一種FGPA中CPHY信號的發送系統,包括MIPI數字模塊、HSTX和LPTX;其中:所述MIPI數字模塊,用于將FPGA輸出的數據轉換為3路7位寬數據并輸出;所述HSTX包括:3個數據通路,其中每個數據通路用于將各自對應的1路7位寬數據轉換為1位寬數據;3線編碼器,與所述3個數據通路相連,用于對3個數據通路輸出的數字信號進行編碼,得到驅動信號;驅動器,與3線編碼器相連,用于將所述驅動信號轉換為3路模擬信號,以便在信道進行傳輸,其中LPTX發送符合MIPI?CPHY協議的低速握手信號,通知接收端使能接收端阻抗,使能接收端的高速接收器,以便建立高速通信鏈接,同時在高速信號通信結束時,讓系統進入低功耗狀態。

技術研發人員:吳啟明,丁佳,周強,林曉志,王添平

受保護的技術使用者:上海先基半導體科技有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!