一種時鐘相位誤差校準(zhǔn)裝置及方法與流程

本技術(shù)屬于芯片,特別涉及一種時鐘相位誤差校準(zhǔn)方法裝置及方法。

背景技術(shù):

1、隨著集成電路工藝的不斷升級,芯片的運行速度和吞吐率在不斷提高,對時鐘質(zhì)量要求也在提高。其中相位誤差是高速時鐘的重要指標(biāo);對于高速serdes接口,時鐘數(shù)據(jù)恢復(fù)裝置的時鐘質(zhì)量直接決定了serdes的性能。而對于時鐘數(shù)據(jù)恢復(fù)電路,多相位輸入時鐘的相位誤差又直接影響時鐘數(shù)據(jù)恢復(fù)電路的線性度性能。

2、然而,從pll送出來的高速時鐘,會因為工藝失配,長距離傳輸,電路本身設(shè)計失配等原因造成時鐘相位誤差的惡化;因此設(shè)計多相位時鐘相位誤差校準(zhǔn)電路是不可繞過的選擇。

技術(shù)實現(xiàn)思路

1、本技術(shù)的目的在于提供一種時鐘相位誤差校準(zhǔn)方法裝置及方法,旨在解決相關(guān)技術(shù)中數(shù)字時鐘校準(zhǔn)無法實現(xiàn)高速高精度時鐘校準(zhǔn),而模擬數(shù)字時鐘校準(zhǔn)容易受檢測電路自身失配影響的問題。

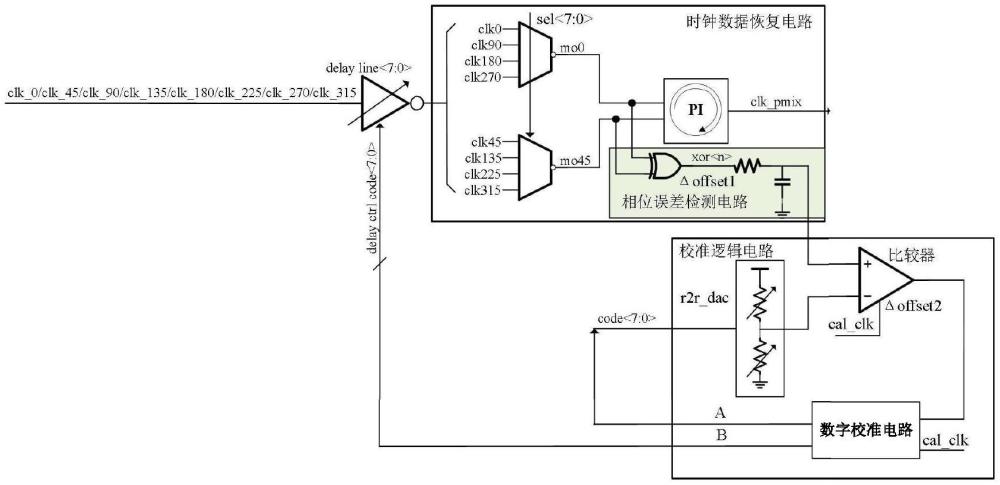

2、根據(jù)本技術(shù)的第一方面,提供了一種時鐘相位誤差校準(zhǔn)裝置,包括:延時鏈、時鐘數(shù)據(jù)恢復(fù)電路、相位誤差檢測電路和校準(zhǔn)邏輯電路;

3、所述延時鏈用于在控制碼值的控制下,輸出相位各不相同的多個延時時鐘信號,所述多個延時時鐘信號的任意一個與所述多個延時時鐘信號中的其中兩個的期望相位誤差為設(shè)定誤差值;

4、所述時鐘數(shù)據(jù)恢復(fù)電路依次從多個延時時鐘信號選擇期望相位誤差為設(shè)定誤差值的兩個延時時鐘信號;

5、所述相位誤差檢測電路用于檢測所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號之間的檢測相位誤差;

6、所述校準(zhǔn)邏輯電路用于根據(jù)所述檢測相位誤差對應(yīng)的直流電壓點輸出控制所述延時鏈調(diào)整所述延時時鐘信號的延時的控制碼值,以使所述延時時鐘信號與其中兩個延時時鐘信號的真實相位誤差向所述設(shè)定誤差值逼近。

7、在可選的實施方式中,所述時鐘數(shù)據(jù)恢復(fù)電路包括:第一信號選擇器和第二信號選擇器;

8、所述第一信號選擇器從所述延時鏈接收一半數(shù)量的所述延時時鐘信號,并從中選出一個延時時鐘信號;所述第一信號選擇器接收的所述延時時鐘信號兩兩之間的期望相位誤差為所述設(shè)定誤差值的偶數(shù)倍;

9、所述第二信號選擇器從所述延時鏈接收另一半數(shù)量的所述延時時鐘信號,并從中選出一個延時時鐘信號;所述第二信號選擇器接收的所述延時時鐘信號兩兩之間的期望相位誤差也為所述設(shè)定誤差值的偶數(shù)倍;

10、所述第一信號選擇器和所述第二信號選擇器每次選出的所述延時時鐘信號組成一種待檢測時鐘信號組合,且所述第一信號選擇器和所述第二信號選擇器依次循環(huán)選出多種不同的所述待檢測時鐘信號組合。

11、在可選的實施方式中,所述相位誤差檢測電路包括:異或邏輯電路;

12、所述異或邏輯電路接收所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號,并通過異或邏輯操作檢測所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號之間的檢測相位誤差。

13、在可選的實施方式中,所述校準(zhǔn)邏輯電路包括:比較器、數(shù)模轉(zhuǎn)換器和校準(zhǔn)算法電路;

14、所述比較器接收所述相位誤差檢測電路輸出的所述檢測相位誤差對應(yīng)的第一電壓信號以及所述數(shù)模轉(zhuǎn)換器輸出的第二電壓信號,并通過比較所述第一電壓信號和所述第二電壓信號輸出調(diào)整所述第二電壓信號的調(diào)整信號;

15、所述校準(zhǔn)算法電路將所述調(diào)整信號輸出至所述數(shù)模轉(zhuǎn)換器,并根據(jù)所述調(diào)整信號更新所述第二電壓信號對應(yīng)的直流電壓點;

16、所述數(shù)模轉(zhuǎn)換器根據(jù)所述調(diào)整信號向所述比較器輸出調(diào)整后的所述第二電壓信號,以使調(diào)整后的所述第二電壓信號相較于調(diào)整前更接近于所述第一電壓信號;

17、在調(diào)整后的所述第二電壓信號滿足設(shè)定條件后,所述校準(zhǔn)算法電路將更新后的所述直流電壓點確定為所述檢測相位誤差的直流電壓點,并根據(jù)所述檢測相位誤差對應(yīng)的所述直流電壓點輸出所述檢測相位誤差對應(yīng)的控制碼值。

18、在可選的實施方式中,所述校準(zhǔn)算法電路預(yù)先確定每一種所述待檢測時鐘信號組合的所述檢測相位誤差對應(yīng)的所述直流電壓點,并根據(jù)每一種所述待檢測時鐘信號組合對應(yīng)的所述直流電壓點,確定所有所述待檢測時鐘信號組合的相位總誤差對應(yīng)的直流總電壓點;

19、時鐘校準(zhǔn)過程中,所述校準(zhǔn)算法電路針對所述時鐘數(shù)據(jù)恢復(fù)電路當(dāng)前輸出的所述待檢測時鐘信號組合確定當(dāng)前的所述直流電壓點,并將當(dāng)前的所述直流電壓點與所述直流總電壓點進行比較,根據(jù)比較結(jié)果調(diào)整當(dāng)前的所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號中相位更大的所述延時時鐘信號的所述控制碼值。

20、在可選的實施方式中,所述控制碼值基于直流平均電壓點與當(dāng)前的所述直流電壓點的差值確定;所述直流平均電壓點基于所述直流總電壓點和所述待檢測時鐘信號組合的總種類數(shù)量確定;

21、所述延時鏈在所述控制碼值的控制下,調(diào)整當(dāng)前的所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號中相位更大的所述延時時鐘信號的延時,調(diào)整的延時長度與所述差值相關(guān)。

22、根據(jù)本技術(shù)的第二方面,提供了一種時鐘相位誤差校準(zhǔn)方法,包括:

23、延時鏈在控制碼值的控制下,輸出相位各不相同的多個延時時鐘信號,所述多個延時時鐘信號的任意一個與所述多個延時時鐘信號中的其中兩個的期望相位誤差為設(shè)定誤差值;

24、時鐘數(shù)據(jù)恢復(fù)電路接收所述多個延時時鐘信號,并依次從多個延時時鐘信號選擇期望相位誤差為設(shè)定誤差值的兩個延時時鐘信號;

25、相位誤差檢測電路接收并檢測所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號之間的檢測相位誤差;

26、校準(zhǔn)邏輯電路根據(jù)所述檢測相位誤差對應(yīng)的直流電壓點輸出控制所述延時鏈調(diào)整所述延時時鐘信號的延時的控制碼值,以使所述延時時鐘信號與其中兩個延時時鐘信號的真實相位誤差向所述設(shè)定誤差值逼近。

27、在可選的實施方式中,所述時鐘數(shù)據(jù)恢復(fù)電路接收所述多個延時時鐘信號,并依次從多個延時時鐘信號選擇期望相位誤差為設(shè)定誤差值的兩個延時時鐘信號,包括:

28、所述時鐘數(shù)據(jù)恢復(fù)電路利用第一信號選擇器從所述延時鏈接收一半數(shù)量的所述延時時鐘信號,并從中選出一個延時時鐘信號后輸出至所述相位誤差檢測電路;所述第一信號選擇器接收的所述延時時鐘信號兩兩之間的期望相位誤差為所述設(shè)定誤差值的偶數(shù)倍;

29、所述時鐘數(shù)據(jù)恢復(fù)電路還利用第二信號選擇器從所述延時鏈接收另一半數(shù)量的所述延時時鐘信號,并從中選出一個延時時鐘信號后輸出至所述相位誤差檢測電路;所述第二信號選擇器接收的所述延時時鐘信號兩兩之間的期望相位誤差也為所述設(shè)定誤差值的偶數(shù)倍;其中,所述第一信號選擇器和所述第二信號選擇器每次選出的所述延時時鐘信號組成一種待檢測時鐘信號組合,且所述第一信號選擇器和所述第二信號選擇器依次循環(huán)選出多種不同的所述待檢測時鐘信號組合。

30、在可選的實施方式中,相位誤差檢測電路接收并檢測所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號之間的檢測相位誤差,包括:

31、所述相位誤差檢測電路利用異或邏輯電路接收所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號,并通過異或邏輯操作檢測所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號之間的檢測相位誤差。

32、在可選的實施方式中,所述校準(zhǔn)邏輯電路根據(jù)所述檢測相位誤差對應(yīng)的直流電壓點輸出控制所述延時鏈調(diào)整所述延時時鐘信號的延時的控制碼值,包括:

33、所述校準(zhǔn)邏輯電路利用比較器接收所述相位誤差檢測電路輸出的所述檢測相位誤差對應(yīng)的第一電壓信號,并比較所述第一電壓信號和數(shù)模轉(zhuǎn)換器輸出的第二電壓信號,根據(jù)比較結(jié)果輸出調(diào)整所述第二電壓信號的調(diào)整信號;

34、所述校準(zhǔn)邏輯電路利用校準(zhǔn)算法電路將所述調(diào)整信號輸出至所述數(shù)模轉(zhuǎn)換器,并根據(jù)所述調(diào)整信號更新所述第二電壓信號對應(yīng)的直流電壓點;

35、所述數(shù)模轉(zhuǎn)換器根據(jù)所述調(diào)整信號向所述比較器輸出調(diào)整后的所述第二電壓信號,以使調(diào)整后的所述第二電壓信號相較于調(diào)整前更接近于所述第一電壓信號;

36、在調(diào)整后的所述第二電壓信號滿足設(shè)定條件后,所述校準(zhǔn)算法電路將更新后的所述直流電壓點確定為所述檢測相位誤差的直流電壓點,并根據(jù)所述檢測相位誤差對應(yīng)的所述直流電壓點輸出所述檢測相位誤差對應(yīng)的所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號中相位更大的所述延時時鐘信號的所述控制碼值。

37、在可選的實施方式中,所述方法還包括:

38、所述校準(zhǔn)算法電路預(yù)先確定每一種所述待檢測時鐘信號組合的所述檢測相位誤差對應(yīng)的所述直流電壓點,并根據(jù)每一種所述待檢測時鐘信號組合對應(yīng)的所述直流電壓點,確定所有所述待檢測時鐘信號組合的相位總誤差對應(yīng)的直流總電壓點;

39、根據(jù)所述檢測相位誤差的所述直流電壓點輸出所述檢測相位誤差對應(yīng)的所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號中相位更大的所述延時時鐘信號的所述控制碼值,包括:

40、將所述直流電壓點與所述直流總電壓點進行比較,根據(jù)比較結(jié)果調(diào)整當(dāng)前的所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號中相位更大的所述延時時鐘信號的所述控制碼值。

41、在可選的實施方式中,所述控制碼值基于直流平均電壓點與當(dāng)前的所述直流電壓點的差值確定;所述直流平均電壓點基于所述直流總電壓點和所述待檢測時鐘信號組合的總種類數(shù)量確定;

42、所述延時鏈在控制碼值的控制下,輸出相位各不相同的多個延時時鐘信號,包括:

43、所述延時鏈在所述控制碼值的控制下,調(diào)整當(dāng)前的所述時鐘數(shù)據(jù)恢復(fù)電路選擇的兩個延時時鐘信號中相位更大的所述延時時鐘信號的延時,調(diào)整的延時長度與所述差值相關(guān)。

44、相比于相關(guān)技術(shù),本技術(shù)的技術(shù)方案具備以下優(yōu)點:

45、本技術(shù)提出的上述時鐘相位誤差校準(zhǔn)裝置的校準(zhǔn)速度以及校準(zhǔn)精度較高,且不受校準(zhǔn)邏輯電路和相位誤差檢測電路誤差的影響,最終調(diào)整得到的多相位時鐘信號之間的誤差小,從而能夠產(chǎn)生高質(zhì)量的數(shù)據(jù)采樣時鐘clk_pmix。

46、本技術(shù)的其它特征和優(yōu)點將在隨后的說明書中闡述,并且部分地從說明書中變得顯而易見,或者通過實施本技術(shù)而了解。本技術(shù)的目的和其他優(yōu)點可以通過在說明書以及附圖中所指出的結(jié)構(gòu)和流程來實現(xiàn)和獲取。

- 還沒有人留言評論。精彩留言會獲得點贊!