半導體結構的制備方法及半導體結構與流程

本發明涉及半導體器件相關,具體地說,涉及一種半導體結構的制備方法及半導體結構。

背景技術:

1、隨著半導體器件的特征尺寸cd(critical?dimension)的不斷縮小,多晶硅柵極的密度不斷提高,層間介質層(inter-layer?dielectric,ild)工藝后的多晶硅柵極之間容易存在空洞(void),在后續形成接觸孔ct的時候,ti、tin、w會通過這些空洞連通,導致半導體器件的漏電流升高,影響器件的性能及運行的可靠性。通常,在自對準硅化物阻擋層(self-aligned?block,sab)工藝后直接進行金屬硅化物(silicide)工藝,再進一步沉積層間介質層ild,當多晶硅柵極之間的間隙的深寬比到一定程度的時候,就會出現空洞。如何提高半導體器件的層間介質層的質量從而提高器件性能成為亟需解決的技術問題。

2、需要說明的是,在上述背景技術部分公開的信息僅用于加強對本發明的背景的理解,因此可以包括不構成對本領域技術人員已知的現有技術的信息。

技術實現思路

1、針對現有技術中的問題,本發明的目的在于提供一種半導體結構的制備方法及半導體結構,該制備方法在沉積層間介質層前通過刻蝕工藝增大多晶硅柵極之間的間隙,從而提高間隙處填充的層間介質層的質量及半導體器件的性能。

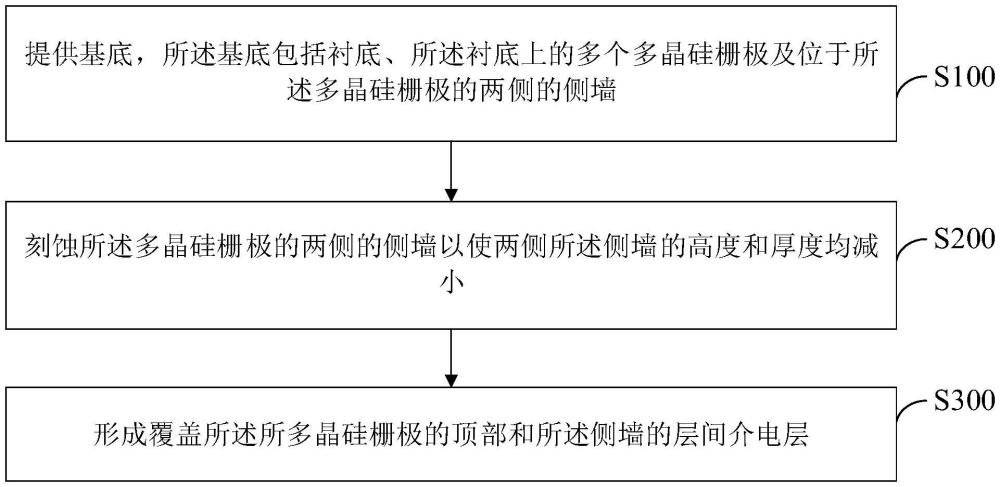

2、具體的,本發明的第一方面提供了一種半導體結構的制備方法,所述制備方法包括如下步驟:

3、提供基底,所述基底包括襯底、所述襯底上的多個多晶硅柵極及位于所述多晶硅柵極的兩側的側墻;

4、刻蝕所述多晶硅柵極的兩側的側墻以使兩側所述側墻的高度和厚度均減小;

5、形成覆蓋所述多晶硅柵極的頂部和所述側墻的層間介質層。

6、根據本發明的第一方面,在所述刻蝕所述多晶硅柵極的兩側的側墻步驟之前,所述制備方法還包括如下步驟:

7、在所述多晶硅柵極的頂部形成金屬硅化物層。

8、根據本發明的第一方面,在所述刻蝕所述多晶硅柵極的兩側的側墻步驟之后,所述制備方法還包括如下步驟:

9、在所述多晶硅柵極的頂部形成金屬硅化物層。

10、根據本發明的第一方面,所述金屬硅化物層為鎳硅化合物層、鈦硅化合物層和鉑硅化合物層中的一層或多層。

11、根據本發明的第一方面,所述側墻為氮化硅側墻;

12、采用濕法刻蝕工藝刻蝕所述多晶硅柵極的兩側的側墻;

13、所述濕法刻蝕工藝中采用的刻蝕液為磷酸溶液。

14、根據本發明的第一方面,所述層間介質層包括一層或多層介質層。

15、根據本發明的第一方面,所述層間介質層為氧化硅層或氮化硅層。

16、根據本發明的第一方面,兩個相鄰的所述多晶硅柵極的相鄰側墻形成一間隙,所述間隙的深寬比大于或等于15。

17、根據本發明的第一方面,所述刻蝕所述多晶硅柵極的兩側的側墻以使兩側所述側墻的高度和厚度均減小步驟后,所述多晶硅柵極的頂部與兩側所述側墻的高度差為h,所述高度差h在100~300埃之間。

18、本發明的第二方面提供了一種半導體結構,所述半導體結構采用所述的半導體結構的制備方法獲得。

19、與現有技術相比,本發明的半導體結構的制備方法中,在沉積層間介質層前,減少相鄰的多晶硅柵極的側墻的厚度,從而增大多晶硅柵極之間的間隙,降低間隙的深寬比,從而減少或消除后續層間介質層沉積過程中形成空洞,提高半導體結構的性能。

技術特征:

1.一種半導體結構的制備方法,其特征在于,所述制備方法包括如下步驟:

2.根據權利要求1所述的半導體結構的制備方法,其特征在于,在所述刻蝕所述多晶硅柵極的兩側的側墻步驟之前,所述制備方法還包括如下步驟:

3.根據權利要求1所述的半導體結構的制備方法,其特征在于,在所述刻蝕所述多晶硅柵極的兩側的側墻步驟之后,所述制備方法還包括如下步驟:

4.根據權利要求2或3所述的半導體結構的制備方法,其特征在于,所述金屬硅化物層為鎳硅化合物層、鈦硅化合物層和鉑硅化合物層中的一層或多層。

5.根據權利要求1所述的半導體結構的制備方法,其特征在于,所述側墻為氮化硅側墻;

6.根據權利要求1所述的半導體結構的制備方法,其特征在于,所述層間介質層包括一層或多層介質層。

7.根據權利要求1所述的半導體結構的制備方法,其特征在于,所述層間介質層為氧化硅層或氮化硅層。

8.根據權利要求1所述的半導體結構的制備方法,其特征在于,兩個相鄰的所述多晶硅柵極的相鄰側墻形成一間隙,所述間隙的深寬比大于或等于15。

9.根據權利要求1所述的半導體結構的制備方法,其特征在于,所述刻蝕所述多晶硅柵極的兩側的側墻以使兩側所述側墻的高度和厚度均減小步驟后,所述多晶硅柵極的頂部與兩側所述側墻的高度差為h,所述高度差h在100埃~300埃之間。

10.一種半導體結構,其特征在于,所述半導體結構采用權利要求1至權利要求9中任意一項所述的半導體結構的制備方法獲得。

技術總結

本發明提供了一種半導體結構的制備方法及半導體結構,所述制備方法包括如下步驟:提供基底,所述基底包括襯底、所述襯底上的多個多晶硅柵極及位于所述多晶硅柵極的兩側的側墻;刻蝕所述多晶硅柵極的兩側的側墻以使兩側所述側墻的高度和厚度均減小;形成覆蓋所述多晶硅柵極的頂部和所述側墻的層間介質層。本發明的半導體結構的制備方法中,在沉積層間介質層前,減少相鄰的多晶硅柵極的側墻的厚度,從而增大多晶硅柵極之間的間隙,降低間隙的深寬比,從而減少或消除后續層間介質層沉積過程中形成空洞,提高半導體結構的性能。

技術研發人員:陳蔚,林露,樊穎濤

受保護的技術使用者:上海積塔半導體有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!