一種寬禁帶半導體復合高壓垂直功率芯片及制作工藝的制作方法

本發明涉及半導體器件,具體涉及一種寬禁帶半導體復合高壓垂直功率芯片及制作工藝。

背景技術:

1、基于8英寸/12英寸fab平臺bcd工藝(bipolar、cmos和dmos)的高壓功率集成芯片廣泛應用于各種電源管理和功率芯片領域,可以實現在同一芯片上制作雙極管bipolar、cmos和dmos器件。bcd工藝的發展并不完全遵循moore定律,而是朝著高壓、高功率、高密度三個方向分化發展,特別是近年來,產業的需求需要更高電壓等級,達500-700v甚至更高,更高功率密度的單片集成pmic(power?management?ic)芯片,然而,硅材料本身耐壓能力有限,每μm厚度/長度的硅外延層只能耐壓10v左右,高壓特別是高于700v以上的bcd工藝高壓管區硅外延層耐壓長度往往需要70μm以上,工藝結構開發困難,工藝復雜,高于1200v的硅基bcd工藝還沒有規模有效的技術實現方案。另外,現有的高壓bcd功率芯片中,由于硅材料的耐壓能力限制,需要占用很大的面積,高低壓隔離方案也非常復雜,導致高壓管dmos或ldmos部分在芯片中占據非常大的面積,工藝復雜成本高昂。

2、近年來,sic、gan、ga2o3、aln等寬禁帶半導體材料具有比硅材料優異的高耐壓耐高溫耐輻射等優良特性而備受關注。如果直接采用寬禁帶半導體整片晶圓襯底(1)及外延片制作高壓bcd工藝集成芯片,一個是寬禁帶半導體材料本身發展不成熟,很多材料的完整晶圓成本高昂,另外則是寬禁帶半導體材料制作的器件各自有其問題,例如碳化硅的mosfet結構柵氧層缺陷多,閾值電壓容易產生漂移等各種可靠性問題,而且需要很大特殊工藝設備,工藝復雜;而gan和ga2o3材料存在p型遷移率差或者缺乏有效p型離子注入激活構造的問題;aln則存在材料晶體尺寸較小,不到6英寸,成本十分高昂的問題。但這些寬禁帶半導體薄膜材料則可以通過高溫cvd或者mocvd或者mbe等工藝方法在不同的襯底(1)晶圓表面生長,可以低成本高質量構造幾百納米到十幾個微米厚度的大尺寸晶圓級寬禁帶半導體薄膜材料;

3、產業界還缺乏有效的芯片架構和工藝方法把成熟的硅基cmos芯片技術和寬禁帶半導體的高耐壓性能結合起來,構造更有效更高性能更低成本的復合功率集成芯片的方案。未來隨著產業技術對于更高電壓等級,1200v甚至更高,更高功率密度的單片集成pmic(power?management?ic)芯片的需求,急需要探索新型的復合高壓功率芯片構造技術。

4、現有的基于全硅cmos和bcd工藝技術方案中,為了制作中高壓及高壓功率芯片集成,往往需要開發復雜的bcd高壓功率單元工藝及復雜的中高壓與低壓邏輯區的隔離工藝技術方案。特別是高壓dmos和ldmos,耐壓區不僅占用大量寶貴的芯片面積(如圖1所示,中高壓功率區和高壓功率芯片區在整個芯片面積占比往往超過50%),而且需要制作結隔離(ji)、深隔離(dti)、soi隔離等昂貴復雜的隔離工藝結構,并開發與之配套的高均勻性超深孔刻蝕,超深通孔金屬填充及平坦化工藝,對各模組工藝開發均提出了挑戰,例如與之配套的厚氧化層生長應力控制、超深孔刻蝕片內均勻性控制、超深通孔金屬化填充控制、平坦化工藝停止點及研磨均勻性控制等等,帶來工藝的復雜度,各種器件特性問題,及良率問題。

5、sic、gan、ga2o3、aln等寬禁帶半導體材料具有比硅材料優異的高耐壓耐高溫耐輻射等優良特性,是否可以通過一些新的芯片架構,器件構造和工藝制作方法,使硅cmos邏輯單元區及功率器件結構中的硅開關控制單元部件依然采用傳統的硅材料制作,而將寬禁帶半導體漂移區作為耐壓單元集成構成復合器件芯片技術,優化高壓集成芯片架構,實現更好性能,更低芯片面積和工藝成本,制成新型復合高壓bcd功率集成芯片,是本發明要解決的技術問題。

技術實現思路

1、基于上述表述,本發明提供了一種寬禁帶半導體復合高壓垂直功率芯片及制作工藝,以解決現有技術的芯片基于全硅制成,需要開發復雜的bcd高壓功率單元工藝及復雜的中高壓與低壓邏輯區的隔離工藝方案的技術問題,通過本發明的方案能優化高壓集成芯片架構,實現更好的性能,更低的芯片面積和工藝成本。

2、本發明解決上述技術問題的技術方案如下:

3、一方面,本發明提供一種寬禁帶半導體復合高壓垂直功率芯片,為高壓bcd芯片;

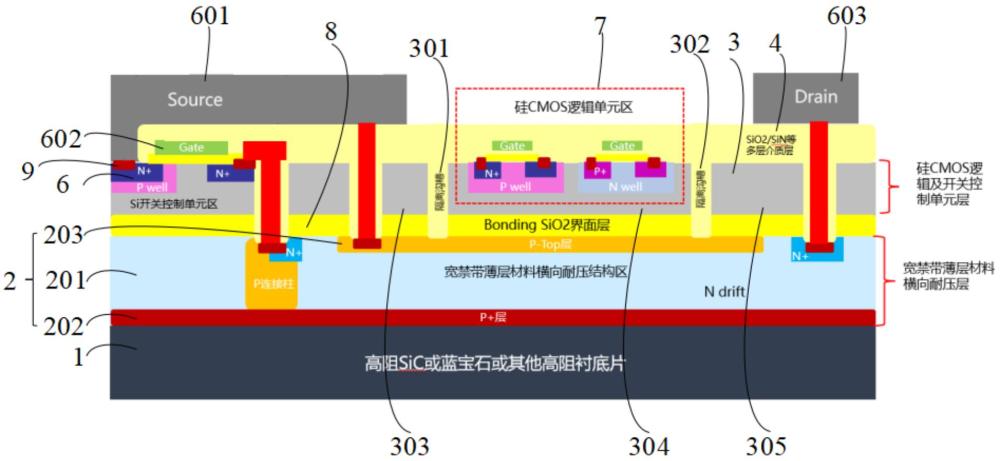

4、所述芯片包括至少一個元胞結構單元,該元胞結構單元包括襯底、寬禁帶薄層材料制成的橫向集成的高耐壓層、硅薄膜層、連接在硅薄膜層上的硅cmos邏輯及開關控制單元、第一多層介質層,所述橫向集成的高耐壓層和硅薄膜層豎向設置,用于使高壓功率管區域和低壓邏輯區域處于不同的物理層實現自隔離;

5、所述橫向集成的高耐壓層包括寬禁帶薄層材料制成的橫向集成的高耐壓結構區、p+掩埋層和p-top層,所述p+掩埋層和p-top層分居橫向集成的高耐壓結構區上下兩側,所述橫向集成的高耐壓層和硅薄膜層之間通過界面鍵合介質層連接;

6、所述硅薄膜層被填充有多層介質層的第一隔離溝槽、第二隔離溝槽分隔成高壓功率管上管臂1區、高壓功率管下管臂1區、高壓功率管其他管臂區;

7、所述硅cmos邏輯及開關控制單元包括硅開關控制單元和硅cmos低壓邏輯單元,所述硅開關控制單元設于高壓功率管上管臂1區,所述硅cmos低壓邏輯單元設于高壓功率管下管臂1區;

8、所述硅cmos邏輯及開關控制單元周邊采用把硅薄膜層部分或完全刻蝕形成包圍的隔離溝槽并填充第一多層介質層的方式隔離。

9、在上述技術方案的基礎上,本發明還可以做如下改進。

10、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述硅開關控制單元包括源極、用作控制開關的第一柵極、漏極、第一p?well區、第一n+區、第二n+區、第三n+區、第四n+區、p連接柱、第一連接金屬、第二連接金屬、第三連接金屬,所述漏極設于高壓功率管其他管臂區。

11、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述橫向集成的高耐壓層連接于硅薄膜層和襯底之間,且硅薄膜層靠近襯底的一側通過界面鍵合介質層與高耐壓結構區連接,所述p-top層連接于高耐壓結構區上與界面鍵合介質層相接處,一端位于高壓功率管上管臂1區下方,另一端位于高壓功率管其他管臂區下方。

12、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述硅薄膜層連接于橫向集成的高耐壓層和襯底之間,且硅薄膜層遠離襯底的一側的硅cmos邏輯及開關控制單元周邊采用把硅薄膜層部分或完全刻蝕形成包圍的隔離溝槽并填充第一多層介質層的方式隔離,并通過界面鍵合介質層與p+掩埋層連接,所述橫向集成的高耐壓層的p-top層側連接第二多層介質層。

13、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述高壓功率管上管臂1區上靠近第一隔離溝槽處開有第一金屬通孔,高壓功率管上管臂1區上遠離第一金屬通孔的一側設有第一p?well區,另一側設有第一n+區,第一p?well區上設有第二n+區,兩個n+區上均連接有歐姆接觸,第一多層介質層內與兩個n+區相接處設有第一柵氧化層,第一柵氧化層靠近第一n+區的一端與第一n+區上的歐姆接觸連接,所述第一柵氧化層遠離高阻襯底的一側連接第一柵極;

14、所述第一金屬通孔內連接有第一連接金屬,所述第一多層介質層遠離襯底的一側高壓功率管上管臂1區上方連接有源極,所述源極一端與第二n+區上的歐姆接觸連接,另一端與第一連接金屬上端連接,所述第一連接金屬下端與p-top層遠離第二隔離溝槽一端的歐姆接觸連接;

15、第一n+區靠近第一金屬通孔的一側且與所述第一n+區相接處開設有第二金屬通孔,第二金屬通孔的下端位于橫向集成的高耐壓結構區,第二金屬通孔內連接有第二連接金屬,所述高耐壓結構區上第二金屬通孔下方連接p連接柱,p連接柱靠近第二隔離溝槽的一側連接第三n+區,第三n+區靠近第二隔離溝槽的一側超出p連接柱,第二連接金屬下端與同時連接p連接柱和第三n+區的歐姆接觸連接,上端與第一n+區上的歐姆接觸連接,所述高壓功率管其他管臂區開設有第三金屬通孔,所述第三金屬通孔內連接第三連接金屬,所述高耐壓結構區上第三金屬通孔下方連接具有歐姆接觸的第四n+區,所述漏極通過第三連接金屬與第四n+區內的歐姆接觸連接連接;

16、所述第一金屬通孔、第二金屬通孔、第三金屬通孔的孔壁上覆蓋有一層10nm-800nm厚度的介質隔離層。

17、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,

18、所述硅開關控制單元包括源極、用作控制開關的第一柵極、漏極、第一p?well區、第一n+區、第二n+區、第三n+區、第四n+區、p連接柱、第四連接金屬、第五連接金屬、第六連接金屬、第七連接金屬,所述漏極設于高壓功率管其他管臂區;

19、所述橫向集成的高耐壓層上高壓功率管上管臂1區上方開設有延伸至硅薄膜層的第四金屬通孔,高壓功率管上管臂1區上遠離第四金屬通孔的一側設有第一p?well區,另一側設有第一n+區,第一p?well區上設有第二n+區,兩個n+區上均連接有歐姆接觸,第一多層介質層內與兩個n+區相接處設有第一柵氧化層,第一柵氧化層靠近第一n+區的一端與第一n+區上的歐姆接觸連接,所述第一柵氧化層遠離高阻襯底的一側連接第一柵極;

20、所述第二多層介質層上方連接有源極,所述源極一端通過第五連接金屬與第二n+區上的歐姆接觸連接,另一端通過第六連接金屬與p-top層遠離第二隔離溝槽一端的歐姆接觸連接;

21、所述第四金屬通孔內連接有第四連接金屬,所述橫向集成的高耐壓層上遠離第二隔離溝槽的一端內連接p連接柱,p連接柱靠近第二隔離溝槽的一側連接第三n+區,第三n+區靠近第二隔離溝槽的一側超出p連接柱,所述第四連接金屬下端與第一n+區上的歐姆接觸連接,上端與同時連接p連接柱和第三n+區的歐姆接觸連接,所述橫向集成的高耐壓層上高壓功率管其他管臂區上方連接具有歐姆接觸的第四n+區,所述第二多層介質層上高壓功率管其他管臂區上方連接漏極,所述漏極通過第七連接金屬與第四n+區內的歐姆接觸連接連接;

22、所述第四金屬通孔的孔壁上覆蓋有一層10nm-800nm厚度的介質隔離層。

23、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述襯底為設置在p+掩埋層遠離橫向集成的高耐壓結構區的一側的高阻襯底,或者所述襯底包括連接在p+掩埋層遠離橫向集成的高耐壓結構區一側的高阻sic單晶薄膜層和連接在高阻sic單晶薄膜層遠離橫向集成的高耐壓結構區一側的多晶碳化硅層,所述隔離溝槽底部穿透p+掩埋層位于高阻sic單晶薄膜層內;

24、所述高阻襯底為高阻sic、藍寶石或高阻硅片,所述多晶碳化硅層的厚度為100-500μm。

25、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述橫向集成的高耐壓層為寬禁帶薄層材料,為n型摻雜半導體材料;所述寬禁帶薄層材料由sic、gan、ga2o3或aln制成,厚度為100nm-50μm,優選為2μm,當寬禁帶薄層材料由sic制成時,歐姆接觸金屬為鎳金屬層或鈦鎳鋁復合金屬層;和/或,

26、所述界面鍵合介質層的材料為sio2或苯并環丁烯樹脂,所述界面鍵合介質層的厚度為1nm-10μm;和/或,

27、所述多層介質層由sio2和sin通過cvd化學氣相沉積法復合而成,所述硅薄膜層的厚度為100nm-10μm;和/或,

28、所述硅薄膜層為n型摻雜,厚度為100nm-10μm;和/或,

29、所述橫向集成的高耐壓層通過外延或鍵合的方法形成。

30、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片,所述硅cmos低壓邏輯單元包括第二p?well區、n?well區、第二柵極、第三柵極、第二柵氧化層、第三柵氧化層;

31、所述第二p?well區兩側分別設有第五n+區、第六n+區,兩個n+區上均連接有歐姆接觸,所述多層介質層上與第二p?well區連接處連接有第二柵氧化層,所述第二柵氧化層兩端分別與歐姆接觸連接;所述n?well區兩側分別設有p+掩埋層,兩個p+掩埋層上均連接有歐姆接觸,所述多層介質層上與n?well區連接處連接有第三柵氧化層,第三柵氧化層兩端分別與歐姆接觸連接;所述第二柵氧化層遠離高阻襯底的一側連接第二柵極,所述第三柵氧化層遠離高阻襯底的一側連接第三柵極。

32、另一方面,本發明還提供一種寬禁帶半導體復合高壓垂直功率芯片的制作工藝,包括以下步驟:

33、s1、在襯底上外延或鍵合一層n型摻雜寬禁帶薄層材料作為橫向集成的高耐壓層,該寬禁帶薄層材料靠近高阻襯底的一面連接有一層p+掩埋層;

34、s2、在寬禁帶薄層材料里通過離子注入形成第三n+區、第四n+區,p連接柱及p-top耐壓場板區,并退火激活;

35、s3、在后續需要和上面硅薄膜層的器件通孔連接的區域,進行歐姆接觸金屬沉積,并退火形成歐姆接觸;

36、s4、在寬禁帶薄層材料制成的高耐壓層遠離高阻襯底的一側通過cvd、ald或者旋涂工藝沉積一層界面鍵合介質層;

37、s5、通過晶圓級鍵合bonding工藝,鍵合一層n型摻雜硅薄膜層;

38、s6、在硅薄膜層里采用cmos工藝制作出硅開關控制單元以及硅cmos低壓邏輯單元;

39、s7、在硅薄膜層中刻蝕金屬通孔和隔離溝槽,金屬通孔的孔壁上覆蓋有一層10nm-800nm厚度的介質隔離層,金屬通孔的中心填充有連接金屬,連接金屬底部與寬禁帶半導體的歐姆接觸金屬區域接觸,起到電氣連接作用。

40、進一步地,上述的一種寬禁帶半導體復合高壓垂直功率芯片的制作工藝,將步驟s5、s6、s7替換為步驟s5-1、s6-1;

41、s5-1、采用carrier載片晶圓臨時鍵合并將背面硅襯底研磨減薄磨到2-10μm后,再晶圓級鍵合到寬禁帶薄層材料制成的高耐壓層遠離高阻襯底的一側;所述carrier載片晶圓為集成了硅cmos邏輯及開關控制單元的硅薄膜層;

42、s6-1、在硅薄膜層中刻蝕金屬通孔和隔離溝槽,金屬通孔的孔壁上覆蓋有一層10nm-800nm厚度的介質隔離層,金屬通孔的中心填充有連接金屬,連接金屬底部與寬禁帶半導體的歐姆接觸金屬區域接觸,起到電氣連接作用。

43、與現有技術相比,本發明的技術方案具有以下有益技術效果:

44、第一,本方案新型高壓bcd功率芯片的構架及制作工藝,結合了寬禁帶半導體高耐壓高功率特性與傳統硅基cmos工藝的成熟的工藝平臺。sic、gan、ga2o3、aln等寬禁帶半導體wbg(wide?bandgap)材料具有比硅材料優異的高耐壓耐高溫耐輻射等優良特性,每μm厚度/長度的寬禁帶半導體外延層耐壓能力可達100v以上,高于硅材料外延層單位μm厚度10倍以上;本方案通過一種新的芯片架構,器件構造和工藝制作方法,將傳統的硅cmos邏輯單元區及功率器件結構中的硅開關控制單元部件依然采用硅材料制作,而將寬禁帶半導體漂移區作為耐壓單元集成構成復合高壓器件芯片技術,優化高壓集成芯片架構,實現更好性能,更低芯片面積和工藝成本的復合新型高壓bcd功率集成芯片;

45、第二,避免了在傳統硅基高壓bcd芯片制作中的高壓功率dmos或ldmos管芯制作和高壓隔離等特殊工藝的構造困難,以及后續繼續向1200v以上高壓bcd工藝演進的困難。例如,現有硅基高壓bcd工藝需要制作結隔離(ji)、深隔離(dti)、soi隔離等昂貴復雜的隔離工藝結構,?并開發與之配套的高均勻性超深孔刻蝕,超深通孔金屬填充及平坦化工藝,對各模組工藝開發均提出了挑戰,例如與之配套的厚氧化層生長應力控制、超深孔刻蝕片內均勻性控制、超深通孔金屬化填充控制、平坦化工藝停止點及研磨均勻性控制等等,帶來工藝的復雜度,各種器件特性問題,及良率問題。而且,由于硅材料每μm厚度/長度的硅外延層耐壓能力僅10v左右,后續繼續向1200v及以上的高壓bcd工藝演進非常困難,業界還沒有可適合規模制作的工藝方案;本新型高壓bcd功率芯片的構架及制作工藝,利用硅cmos邏輯和開關控制單元和寬禁帶半導體耐壓單元結合的方法,寬禁帶半導體材料每μm厚度/長度的寬禁帶半導體外延層耐壓能力可達100v以上,后續可以很容易向1200v以上高壓功率集成芯片技術演進,并自身具有高壓管區域和低壓邏輯區域自隔離的簡單容易的隔離方案,高壓功率管的高壓耐壓區域處于寬禁帶半導體材料層,和硅基低壓邏輯單元層不在同一個物理層,并且中間有界面鍵合介質層自然隔離開;不需要傳統硅基bcd工藝中的額外制作各種復雜的隔離設計和復雜工藝。

- 還沒有人留言評論。精彩留言會獲得點贊!