動(dòng)態(tài)切換RISC-V和X86指令集的處理器、方法及系統(tǒng)與流程

本發(fā)明涉及計(jì)算機(jī),尤其涉及一種動(dòng)態(tài)切換risc-v和x86指令集的處理器、方法及系統(tǒng)。

背景技術(shù):

1、隨著計(jì)算機(jī)技術(shù)的不斷發(fā)展,指令集架構(gòu)也在不斷演進(jìn)。不同處理器架構(gòu)之間存在指令集的差異,這導(dǎo)致了同一操作系統(tǒng)下的應(yīng)用程序在不同指令集架構(gòu)的處理器上運(yùn)行時(shí)可能出現(xiàn)兼容性問題。由于傳統(tǒng)的通用處理器通常采用固定的指令集架構(gòu),因此,現(xiàn)有的處理器通常無法滿足運(yùn)行不同指令集的需求,存在靈活性不足、難以滿足不同應(yīng)用場(chǎng)景等問題。

2、目前,對(duì)于不同指令集架構(gòu)之間的兼容性問題,主要采用軟件翻譯和硬件翻譯兩種方式解決。軟件翻譯技術(shù)能夠?qū)崿F(xiàn)跨指令集的兼容,但因翻譯過程耗時(shí)較長,影響了系統(tǒng)的實(shí)時(shí)響應(yīng)能力;硬件翻譯則試圖在硬件層面實(shí)現(xiàn)不同指令集的即時(shí)轉(zhuǎn)換,但由于硬件設(shè)計(jì)復(fù)雜度高,且難以同時(shí)支持多個(gè)指令集的高效運(yùn)行,因此也存在一定的局限性。

3、現(xiàn)有技術(shù)在解決不同指令集架構(gòu)兼容性問題時(shí),普遍面臨效率低下、成本較高等問題。軟件翻譯雖能解決兼容性問題,但引入了額外的處理時(shí)間,降低了系統(tǒng)的整體性能;而硬件翻譯盡管能在一定程度上提高兼容性,但受限于硬件設(shè)計(jì)復(fù)雜度和成本,難以廣泛應(yīng)用于各類嵌入式系統(tǒng)中。

4、以上背景技術(shù)內(nèi)容的公開僅用于輔助理解本發(fā)明的發(fā)明構(gòu)思及技術(shù)方案,其并不必然屬于本技術(shù)的現(xiàn)有技術(shù),也不必然會(huì)給出技術(shù)教導(dǎo);在沒有明確的證據(jù)表明上述內(nèi)容在本技術(shù)的申請(qǐng)日之前已經(jīng)公開的情況下,上述背景技術(shù)不應(yīng)當(dāng)用于評(píng)價(jià)本技術(shù)的新穎性和創(chuàng)造性。

技術(shù)實(shí)現(xiàn)思路

1、本發(fā)明的目的是提供一種動(dòng)態(tài)切換risc-v和x86指令集的處理器、方法及系統(tǒng),能夠動(dòng)態(tài)切換處理risc-v指令和x86指令,實(shí)現(xiàn)快速高效地處理包括risc-v指令和x86指令的指令流。

2、為達(dá)到上述目的,本發(fā)明采用的技術(shù)方案如下:

3、一種動(dòng)態(tài)切換risc-v和x86指令集的處理器,包括指令讀取單元、翻譯單元和指令處理單元;

4、所述指令讀取單元包括狀態(tài)機(jī)和觸發(fā)電路,所述指令讀取單元被配置為接收待處理的指令流并且傳輸至所述狀態(tài)機(jī),所述指令流包括x86指令序列和risc-v指令序列,并且在任意相鄰的x86指令序列和risc-v指令序列之間均配置有目標(biāo)指令序列;

5、所述狀態(tài)機(jī)被配置為響應(yīng)于接收到所述目標(biāo)指令序列則向所述觸發(fā)電路發(fā)送觸發(fā)信號(hào),否則不向所述觸發(fā)電路發(fā)送觸發(fā)信號(hào);

6、所述觸發(fā)電路被配置為與所述翻譯單元和指令處理單元中的一個(gè)電連接,并且所述觸發(fā)電路響應(yīng)于接收到所述觸發(fā)信號(hào),則所述觸發(fā)電路從當(dāng)前連接所述翻譯單元和指令處理單元中的一個(gè)的狀態(tài)切換為連接所述翻譯單元和指令處理單元中的另一個(gè)的狀態(tài);

7、所述翻譯單元被配置為將x86指令序列翻譯為risc-v指令序列;

8、所述指令處理單元被配置為處理所述risc-v指令序列。

9、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述指令讀取單元還被配置為將接收到的指令流同時(shí)傳輸至所述狀態(tài)機(jī)和所述觸發(fā)電路。

10、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述狀態(tài)機(jī)包括計(jì)數(shù)器,所述計(jì)數(shù)器被配置為根據(jù)所述目標(biāo)指令序列進(jìn)行計(jì)數(shù)以得到目標(biāo)計(jì)數(shù)值,所述目標(biāo)計(jì)數(shù)值具有唯一性;

11、所述狀態(tài)機(jī)響應(yīng)于所述計(jì)數(shù)器的計(jì)數(shù)為所述目標(biāo)計(jì)數(shù)值,則向所述觸發(fā)電路發(fā)送觸發(fā)信號(hào)。

12、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述目標(biāo)指令序列的大小不小于所述處理器的緩存行的大小。優(yōu)選地,所述目標(biāo)指令序列的大小為所述處理器的緩存行的大小相等,或者,所述目標(biāo)指令序列的大小為所述處理器的緩存行的大小的數(shù)倍。處理器的緩存行(cache?line)是處理器緩存系統(tǒng)中的一個(gè)基本單位,用于在處理器和內(nèi)存之間傳輸和存儲(chǔ)數(shù)據(jù)。緩存行是處理器緩存中存儲(chǔ)數(shù)據(jù)的最小單位。

13、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述目標(biāo)指令序列中所包括的單指令的數(shù)量不小于所述處理器的流水線的級(jí)數(shù)。優(yōu)選地,所述目標(biāo)指令序列中所包括的單指令的數(shù)量與所述處理器的流水線的級(jí)數(shù)相等,或者,所述目標(biāo)指令序列中所包括的單指令的數(shù)量為所述處理器的流水線的級(jí)數(shù)數(shù)倍。流水線架構(gòu)是指處理器將一條指令的執(zhí)行過程分解為若干個(gè)連續(xù)的步驟或階段,每個(gè)階段在處理器中由專門的硬件單元執(zhí)行相應(yīng)的任務(wù)。

14、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,還包括:針對(duì)相鄰的x86指令序列和risc-v指令序列,確定在先的指令序列對(duì)應(yīng)的指令集為目標(biāo)指令集,所述指令集包括risc-v指令集和x86指令集;

15、所述目標(biāo)指令序列被配置為所述目標(biāo)指令集中相應(yīng)的指令序列,即若在相鄰的不同指令序列,若在先的指令序列為risc-v指令序列,則所述目標(biāo)指令序列為risc-v指令集中的指令,若在先的指令序列為x86指令序列,則所述目標(biāo)指令序列為x86指令集中的指令。

16、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述目標(biāo)指令序列包括若干個(gè)連續(xù)的空指令;

17、所述計(jì)數(shù)器響應(yīng)于接收到空指令則加一,否則所述計(jì)數(shù)器重置計(jì)數(shù)。

18、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,若所述狀態(tài)機(jī)首次接收到的指令序列為x86指令序列,則所述狀態(tài)機(jī)向所述觸發(fā)電路發(fā)送第一信號(hào),所述觸發(fā)電路響應(yīng)于接收到所述第一信號(hào),則與所述翻譯單元電連接;

19、若所述狀態(tài)機(jī)首次接收到的指令序列為risc-v指令序列,則所述狀態(tài)機(jī)向所述觸發(fā)電路發(fā)送第二信號(hào),所述觸發(fā)電路響應(yīng)于接收到所述第二信號(hào),則與所述指令處理單元電連接。

20、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,在所述處理器每次啟動(dòng)工作后,所述指令流中的第一組指令序列均為x86指令序列;

21、在所述處理器每次啟動(dòng)工作后,所述觸發(fā)電路的初始狀態(tài)均被配置為與所述翻譯單元電連接。

22、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,在所述處理器每次啟動(dòng)工作后,所述指令流中的第一組指令序列均為risc-v指令序列;

23、在所述處理器每次啟動(dòng)工作后,所述觸發(fā)電路的初始狀態(tài)均被配置為與所述指令處理單元電連接。

24、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述翻譯單元被配置為硬件翻譯器,所述硬件翻譯器被配置為通過調(diào)取預(yù)先存儲(chǔ)在硬件裝置中的指令處理結(jié)果以將所述x86指令序列翻譯為risc-v指令序列;

25、所述指令處理結(jié)果包括所述x86指令序列到所述risc-v指令序列的映射關(guān)系。

26、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,通過以下方式獲得所述指令處理結(jié)果:

27、針對(duì)目標(biāo)x86指令集中的任意一個(gè)x86指令序列;

28、判斷是否存在替代所述x86指令序列的等價(jià)risc-v標(biāo)準(zhǔn)指令序列,所述等價(jià)risc-v標(biāo)準(zhǔn)指令序列的功能與所述x86指令序列的功能一致并且二者的執(zhí)行效率差在預(yù)設(shè)范圍內(nèi),若存在,則確定所述x86指令序列為第一指令序列,以及確定所述等價(jià)risc-v標(biāo)準(zhǔn)指令序列為第二指令序列;

29、若不存在,則判斷是否存在替代所述x86指令序列的非等價(jià)risc-v標(biāo)準(zhǔn)指令序列,若存在,則判斷所述非等價(jià)risc-v標(biāo)準(zhǔn)指令序列的執(zhí)行效率是否滿足預(yù)設(shè)的要求,若滿足,則確定所述x86指令序列為第三指令序列,以及確定所述非等價(jià)risc-v標(biāo)準(zhǔn)指令序列為第四指令序列;

30、若不滿足,則確定替代所述x86指令序列的risc-v自定義指令序列,并且確定所述x86指令序列為第五指令序列,以及確定所述risc-v自定義指令序列為第六指令序列;

31、基于以上步驟得到指令序列處理結(jié)果并存儲(chǔ)于一硬件裝置中,所述指令序列處理結(jié)果包括:

32、以所述第一指令序列為輸入,則以所述第二指令序列為輸出;

33、以所述第三指令序列為輸入,則以所述第四指令序列為輸出;

34、以所述第五指令序列為輸入,則以所述第六指令序列為輸出。

35、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,還包括通過以下方式獲得所述指令處理結(jié)果:

36、針對(duì)目標(biāo)x86指令集中的任意一個(gè)x86指令序列;

37、若不存在替代所述x86指令序列的等價(jià)risc-v標(biāo)準(zhǔn)指令序列,并且也不存在替代所述x86指令序列的非等價(jià)risc-v標(biāo)準(zhǔn)指令序列;

38、則確定替代所述x86指令序列的risc-v自定義指令序列,并且確定所述x86指令序列為第五指令序列,以及確定所述risc-v自定義指令序列為第六指令序列。

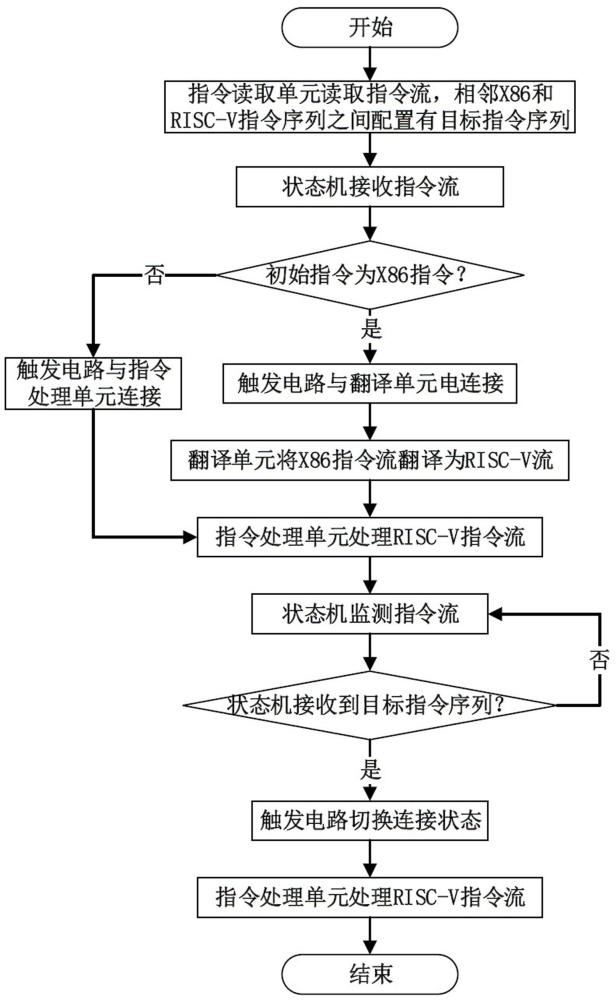

39、根據(jù)本發(fā)明的另一方面,提供了一種動(dòng)態(tài)切換risc-v和x86指令集的處理方法,待處理的指令流包括x86指令序列和risc-v指令序列,所述方法包括以下步驟:

40、預(yù)先配置一觸發(fā)電路,所述觸發(fā)電路包括一個(gè)輸入端和兩個(gè)輸出端,所述輸入端可選擇地與兩個(gè)所述輸出端電連接,其中一個(gè)所述輸出端與翻譯單元電連接,另一個(gè)所述輸出端與指令處理單元電連接;其中,所述翻譯單元被配置為將x86指令序列翻譯為risc-v指令序列,所述指令處理單元被配置為處理所述risc-v指令序列;如此,所述觸發(fā)電路可選擇地控制指令流經(jīng)過兩條傳輸路徑中的一個(gè),其中一條傳輸路徑為指令流經(jīng)過翻譯單元翻譯后再輸入指令處理單元,另一條傳輸路徑為指令流直接輸入所述指令處理單元;

41、在待處理的指令流中任意相鄰的x86指令序列和risc-v指令序列之間配置目標(biāo)指令序列;

42、通過狀態(tài)機(jī)對(duì)待處理的指令流進(jìn)行監(jiān)測(cè),若所述狀態(tài)機(jī)監(jiān)測(cè)到所述目標(biāo)指令序列則生成觸發(fā)信號(hào)并傳輸至所述觸發(fā)電路;

43、所述觸發(fā)電路響應(yīng)于接收到所述觸發(fā)信號(hào),則將所述輸入端當(dāng)前連接一個(gè)所述輸出端切換為連接另一個(gè)所述輸出端,如此實(shí)現(xiàn)切換所述指令流的傳輸/處理路徑。

44、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述的動(dòng)態(tài)切換risc-v和x86指令集的處理方法還包括以下步驟:

45、所述狀態(tài)機(jī)被配置為利用計(jì)數(shù)器檢測(cè)所述目標(biāo)指令序列,所述計(jì)數(shù)器被配置為根據(jù)所述目標(biāo)指令序列進(jìn)行計(jì)數(shù)以得到目標(biāo)計(jì)數(shù)值,所述目標(biāo)計(jì)數(shù)值具有唯一性;

46、所述狀態(tài)機(jī)響應(yīng)于所述計(jì)數(shù)器的計(jì)數(shù)值為所述目標(biāo)計(jì)數(shù)值,則向所述觸發(fā)電路發(fā)送觸發(fā)信號(hào)。

47、進(jìn)一步地,承前所述的任一技術(shù)方案或多個(gè)技術(shù)方案的組合,所述的動(dòng)態(tài)切換risc-v和x86指令集的處理方法還包括:所述目標(biāo)指令序列的大小與所述處理器的緩存行的大小相等。

48、根據(jù)本發(fā)明的另一方面,本發(fā)明提供了一種計(jì)算機(jī)系統(tǒng),包括如上任一技術(shù)方案或多個(gè)技術(shù)方案的組合所述的動(dòng)態(tài)切換risc-v和x86指令集的處理器。

49、本發(fā)明提供的技術(shù)方案帶來的有益效果如下:

50、a.?本發(fā)明通過在處理器中增加用于監(jiān)測(cè)輸入的指令流的狀態(tài)機(jī)以及用于控制指令流傳輸方向的觸發(fā)電路,實(shí)現(xiàn)了根據(jù)指令流中的risc-v和x86指令的變化動(dòng)態(tài)切換相應(yīng)的指令流處理線路,通過硬件方式快速將處理的指令集架構(gòu)進(jìn)行動(dòng)態(tài)的切換,增加了處理器對(duì)不同指令集架構(gòu)間的高效兼容以及程序的移植性和通用性,也降低了程序、處理器等產(chǎn)品的開發(fā)和維護(hù)的成本;

51、b.?本發(fā)明提供的技術(shù)方案通過引入狀態(tài)機(jī)及觸發(fā)電路,可以通過硬件接口實(shí)現(xiàn)指令集切換,簡化了硬件設(shè)計(jì),降低了硬件復(fù)雜度和成本,使得該技術(shù)更容易被廣泛應(yīng)用,更加適合資源有限的嵌入式系統(tǒng)和物聯(lián)網(wǎng)設(shè)備,可適用范圍廣;

52、c.?本發(fā)明通過將目標(biāo)指令序列的大小設(shè)置為與處理器的緩存行的大小相同,并且目標(biāo)指令序列中所包括的單指令的數(shù)量與處理器的流水線的級(jí)數(shù)相等,確保了處理器流水線上的寄存器與算術(shù)邏輯單元內(nèi)數(shù)據(jù)執(zhí)行完成并存入內(nèi)存中,能夠保證指令集切換不會(huì)中斷處理器的工作流程,進(jìn)而提升系統(tǒng)的實(shí)時(shí)響應(yīng)能力和整體性能。

- 基于物聯(lián)網(wǎng)AI技術(shù)的物流運(yùn)費(fèi)...

- 一種用于工業(yè)元件位姿估計(jì)的穩(wěn)...

- 一種針對(duì)企業(yè)經(jīng)營業(yè)務(wù)的統(tǒng)計(jì)分...

- 構(gòu)建巖土三維虛擬模型的方法、...

- 一種基于二叉樹的信貸風(fēng)險(xiǎn)動(dòng)態(tài)...

- 基于組件化的三維模型設(shè)計(jì)方法...

- 基于AI輔助的景觀園林方案輔...

- 一種營銷電子郵件投遞系統(tǒng)及方...

- 基于多維監(jiān)測(cè)融合技術(shù)的無人機(jī)...

- 二進(jìn)制翻譯方法、裝置、電子設(shè)...

- 還沒有人留言評(píng)論。精彩留言會(huì)獲得點(diǎn)贊!