一種功率器件的終端結構、制造方法和芯片與流程

本發明涉及半導體,特別是涉及一種功率器件的終端結構、制造方法和芯片。

背景技術:

1、現代功率器件(如mosfet、igbt等)通常由成千上萬個相同的單元(cell)并聯組成,每個單元都是一個小的功率器件,這些單元并聯在一起可以提高器件的總電流處理能力,每個單元的表面電壓大致相同,因為它們共享相同的電壓源和負載。在功率器件中,終端單元(靠近器件邊緣的單元)與襯底(器件的底層)之間的電壓差可能很大,這是因為終端單元需要承受更高的電壓,以防止電場集中導致的擊穿。這種電壓差會導致終端區域的電場集中,影響器件的耐壓能力。為了提高器件的耐壓能力,需要采取措施減小表面電場,這通常通過優化終端結構來實現,例如使用場限環(field?limiting?ring,flr)等技術,場限環可以在終端區域引入額外的摻雜區域,分散電場,防止電場集中導致的擊穿。現代硅功率器件通常采用淺平面結構(shallow?planar?structure),這種結構可以提高器件的耐壓能力,在場限環設計中,常采用場限環來降低結曲率效應引起的表面電場集中,從而提高擊穿電壓,雖然場限環可以提高擊穿電壓,但它們也會顯著增加芯片面積,這是因為場限環需要在終端區域引入額外的摻雜區域,這些區域占據了芯片的一部分面積。平面場限環在注入結拐角處(即摻雜區域的拐角)可能會出現峰值電場。這種峰值電場會導致器件的擊穿特性退化,因為電場集中會增加擊穿的風險。為了進一步提升結深(即摻雜區域的深度),降低注入結拐角處的峰值電場,可以采用溝槽場限環(trench?field?limiting?ring,tflr)終端結構,溝槽場限環通過在終端區域引入溝槽結構,進一步分散電場,降低峰值電場,雖然溝槽場限環可以降低峰值電場,但它們也會增加場限環終端橫向空間電荷區的擴展能力,這意味著終端區域需要更大的面積來容納這些擴展的空間電荷區,從而導致終端面積增大。

2、在功率器件中,主結環(main?junction)是指器件的主要pn結或肖特基結。為了提高器件的耐壓能力,主結環的表面通常會進行高劑量的摻雜注入。注入劑量通常在1e12~1e15/cm2的數量級。高劑量的摻雜注入會導致主結環的表面電場強度增加。由于主結環的拐角處(即摻雜區域的拐角)電場集中效應更為明顯,因此擊穿通常發生在主結的拐角處。這意味著主結拐角處承受的電場強度最大,容易導致擊穿。在實際生產過程中,注入劑量可能會受到產線機臺的偏差影響。這種偏差會導致注入劑量不均勻,從而影響器件的性能和可靠性。jte(junction?termination?extension)橫向結終端擴展結構是一種用于提高器件耐壓能力的終端保護技術。jte結構通過在終端區域引入額外的摻雜區域,來分散電場,防止電場集中導致的擊穿。然而,如果注入劑量偏差導致jte結構的摻雜濃度低,那么jte結構的效果會受到影響。如果jte結構的摻雜濃度低,那么電場分布會不均勻,導致擊穿發生在jte橫向結終端擴展結構處。這意味著jte結構未能有效分散電場,反而成為了擊穿的位置。由于jte結構的摻雜濃度低,導致擊穿發生在jte結構處,這會使得終端的可靠性不佳,耐壓能力不足。這意味著器件在高電壓或高溫環境下容易失效,影響系統的穩定性和壽命。

技術實現思路

1、鑒于上述問題,提出了本發明實施例以便提供一種克服上述問題或者至少部分地解決上述問題的一種功率器件的終端結構、制造方法和芯片。

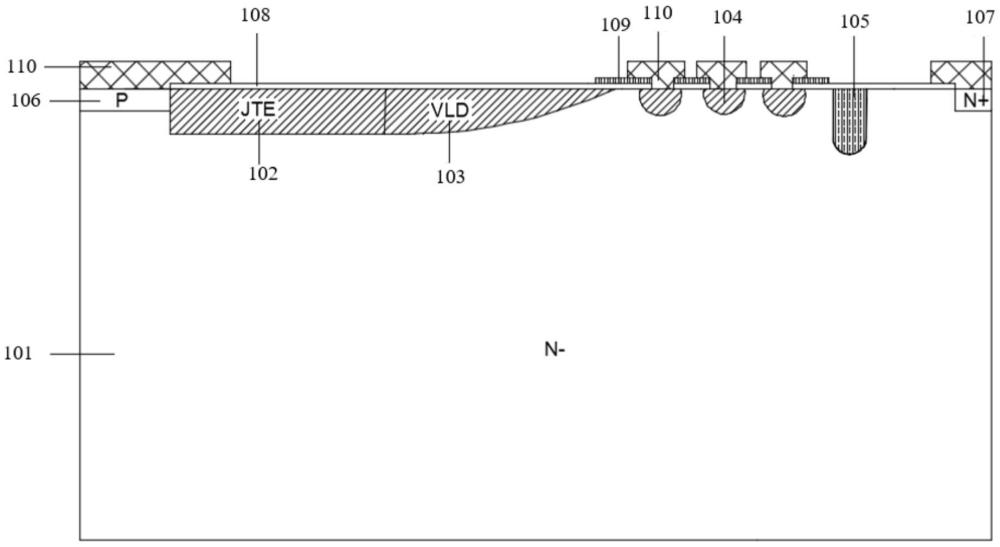

2、為了解決上述問題,本發明實施例公開了一種功率器件的終端結構,所述終端結構包括:

3、n型襯底;

4、設于所述n型襯底的結終端擴展區、結漸變摻雜區和多個場限環,所述結終端擴展區與所述結漸變摻雜區連接,所述結漸變摻雜區的深度沿遠離所述結終端擴展區的方向漸變遞減,所述多個場限環設于所述結漸變摻雜區遠離所述結終端擴展區的一端,且所述多個場限環相對所述結漸變摻雜區的距離漸變遞增;所述結終端擴展區、所述結漸變摻雜區和所述多個場限環內摻雜有p型離子;

5、設于所述n型襯底的溝槽,所述溝槽設于距離所述結漸變摻雜區最遠的場限環遠離所述結漸變摻雜區的一側;所述溝槽內淀積有多晶硅;

6、設于所述n型襯底的p阱區和截止環n+區,所述p阱區與所述結終端擴展區連接,所述截止環n+區設于所述溝槽遠離所述場限環的一側;

7、設于所述n型襯底表面的氧化層;

8、設于所述氧化層的目標區域的表面的多晶硅場板,所述目標區域為覆蓋所述多個場限環的邊沿的預設寬度的區域;

9、設于所述p阱區的表面、所述結終端擴展區靠近所述p阱區的部分區域的表面、所述多個場限環的上方、所述截止環n+區的表面和所述氧化層中靠近所述截止環n+區的部分區域的表面的金屬層。

10、可選的,所述n型襯底為n-型襯底,所述終端結構還包括:

11、在所述n-型襯底的另一側形成的n+型緩沖層;

12、在所述n+型緩沖層上形成的p+型集電區;

13、在所述p+型集電區上形成的集電極端。

14、可選的,所述各個場限環的寬度區間為5-12um。

15、可選的,所述溝槽的深度范圍為4-6um,所述溝槽的寬度范圍為0.6-2um。

16、可選的,所述金屬層的厚度范圍為3-5um。

17、相應的,本發明實施例公開了一種功率器件的終端結構的制造方法,用于制造如上所述的功率器件的終端結構,所述方法包括:

18、提供n型襯底;

19、在所述n型襯底形成結終端擴展區、結漸變摻雜區和多個場限環;所述結終端擴展區與所述結漸變摻雜區連接,所述結漸變摻雜區的深度沿遠離所述結終端擴展區的方向漸變遞減,所述多個場限環設于所述結漸變摻雜區遠離所述結終端擴展區的一端;

20、在所述n型襯底,形成溝槽,所述溝槽設于距離所述結漸變摻雜區最遠的場限環遠離所述結漸變摻雜區的一側;

21、在所述溝槽內淀積多晶硅;

22、在所述n型襯底,形成p阱區和截止環n+區;所述p阱區與所述結終端擴展區連接,所述截止環n+區設于所述溝槽遠離所述場限環的一側;

23、在所述n型襯底表面生長氧化層,

24、將所述p阱區、所述多個場限環的中心區域、所述截止環n+區的表面對應的氧化層清除;

25、在所述氧化層的目標區域的表面生成多晶硅場板;所述目標區域為覆蓋所述多個場限環的邊沿的預設寬度的區域;

26、在所述p阱區的表面、在所述結終端擴展區靠近所述p阱區的部分區域的表面、在所述多個場限環的上方、所述截止環n+區的表面和所述氧化層中靠近所述截止環n+區的部分區域的表面,生成金屬層。

27、可選的,所述n型襯底為n-型襯底,所述方法還包括:

28、在所述n-型襯底的另一側對所述n-型襯底進行背面減薄;

29、在所述n-型襯底的另一側對所述n-型襯底進行高濃度的n型摻雜,形成n+型緩沖層;

30、在所述n+型緩沖層上進行高濃度的p型摻雜,形成p+型集電區;

31、在所述p+型集電區上淀積金屬層,形成集電極端。

32、可選的,所述多個場限環相對所述結漸變摻雜區的距離漸變遞增;所述結終端擴展區、所述結漸變摻雜區和所述多個場限環內摻雜有p型離子;所述各個場限環的寬度區間為5-12um。

33、可選的,所述覆蓋所述多個場限環的邊沿的覆蓋范圍為0.5~1.5um。

34、可選的,所述溝槽的深度范圍為4-6um,所述溝槽的寬度范圍為0.6-2um。

35、可選的,所述金屬層的厚度范圍為3-5um。

36、相應的,本發明實施例公開了一種芯片,包括如上所述的功率器件的終端結構。

37、本發明實施例包括以下優點:

38、本發明實施例的功率器件的終端結構,包括n型襯底;設于n型襯底的結終端擴展區、結漸變摻雜區和多個場限環,結終端擴展區與結漸變摻雜區連接,結漸變摻雜區的深度沿遠離結終端擴展區的方向漸變遞減,多個場限環設于結漸變摻雜區遠離結終端擴展區的一端,且多個場限環相對結漸變摻雜區的距離漸變遞增;結終端擴展區、結漸變摻雜區和多個場限環內摻雜有p型離子;設于n型襯底的溝槽,溝槽設于距離結漸變摻雜區最遠的場限環遠離結漸變摻雜區的一側;溝槽內淀積有多晶硅;設于n型襯底的p阱區和截止環n+區,p阱區與結終端擴展區連接,截止環n+區設于溝槽遠離場限環的一側;設于n型襯底表面的氧化層;設于氧化層的目標區域的表面的多晶硅場板,目標區域為覆蓋多個場限環的邊沿的預設寬度的區域;設于p阱區的表面、結終端擴展區靠近p阱區的部分區域的表面、多個場限環的上方、截止環n+區的表面和氧化層中靠近截止環n+區的部分區域的表面的金屬層。通過包括結終端擴展區、結漸變摻雜區、多個場限環、溝槽和多晶硅場板的復合終端結構,可以有效降低芯片最大電場強度,提升器件耐壓性能。

- 還沒有人留言評論。精彩留言會獲得點贊!