射頻開關的制作方法

本申請實施例涉及開關設計,尤其涉及一種射頻開關。

背景技術:

1、射頻開關是射頻收發機的重要組成部分,具有切換不同的信號通路進行射頻信號傳輸的功能。

2、目前的射頻開關通常包括多個信號通路,每個信號通路由多個晶體管連接而成,在射頻開關工作的過程中,可以通過切換晶體管的工作情況,以使射頻開關中的每個信號通路分別發生導通或關斷,進而可以實現通過不同的信號通路進行射頻信號傳輸。

3、但是,隨著集成電路工藝的不斷進步,晶體管的特征尺寸與柵氧厚度不斷減小,射頻開關的抗靜電釋放能力(即為抗esd能力)也隨之變得較差;靜電釋放(electro-staticdischarge,esd)是指處于不同靜電電位的兩個物體間的靜電電荷轉移,esd事件通常分為兩類,一類是指芯片在生產、運輸和裝配過程中發生的芯片級esd事件,另一類是指發生在芯片應用時的系統級esd事件,在相同預充電電壓下,系統級esd事件所釋放的能量要遠遠大于芯片級esd事件,所以系統級esd事件對器件的損害更為嚴重;由于晶體管的特征尺寸與柵氧厚度的減小,會使射頻開關較容易發生系統級esd事件,因此導致射頻開關的抗靜電釋放能力更差,以致射頻開關的工作質量較差。

技術實現思路

1、有鑒于此,本申請實施例提供一種射頻開關,以至少部分解決上述問題。

2、根據本申請實施例提供的一種射頻開關,包括:至少一個公共端口、至少一個通路和至少一個非公共端口,所述通路包括第一支路和第二支路;所述第一支路的一端連接于任一所述公共端口,所述第一支路的另一端連接于任一所述非公共端口,所述第一支路包括至少一個第一晶體管;所述第二支路的一端連接在所述第一支路與所述非公共端口之間,所述第二支路的另一端接地,所述第二支路包括至少一個第二晶體管;所述第二晶體管的第一特征距離大于所述第一晶體管的第一特征距離,所述第一特征距離為對應晶體管的源區金屬通孔與柵區之間沿柵長方向的距離;所述第二晶體管的第二特征距離大于所述第一晶體管的第二特征距離,所述第二特征距離為對應晶體管的漏區金屬通孔與柵區之間沿柵長方向的距離。

3、在一種可能的實現方式中,所述第二晶體管的第一特征距離大于或等于0.3微米,所述第二晶體管的第二特征距離大于或等于0.3微米。

4、在一種可能的實現方式中,所述第一晶體管包括第一襯底、第一源區、第一漏區、第一體區和第一柵區;所述第一源區、所述第一漏區和所述第一體區分別設置在所述第一襯底的上方;所述第一柵區設置在所述第一體區的上方。

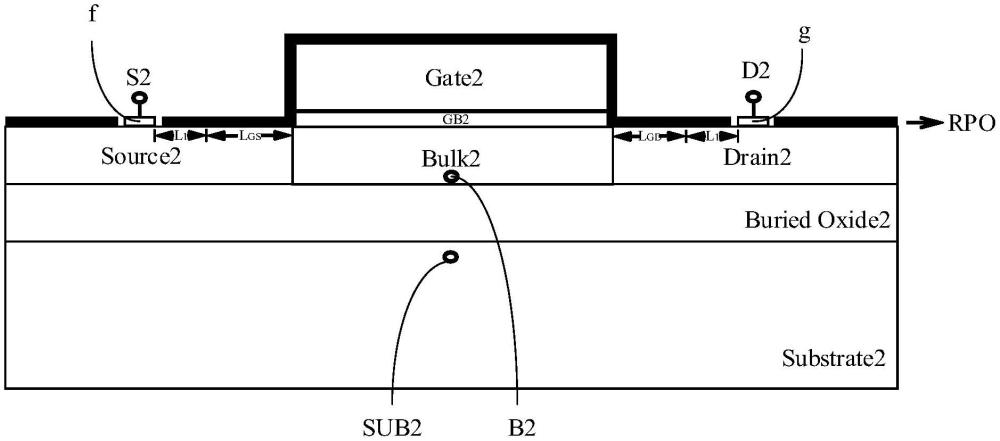

5、在一種可能的實現方式中,所述第二晶體管包括第二襯底、第二源區、第二漏區、第二體區、第二柵區和抗蝕保護氧化物層;所述第二源區、所述第二漏區和所述第二體區分別設置在所述第二襯底的上方;所述第二柵區設置在所述第二體區的上方;所述抗蝕保護氧化物層覆蓋在所述第二源區、所述第二漏區和所述第二柵區的上方。

6、在一種可能的實現方式中,所述第一晶體管的柵寬大于所述第二晶體管的柵寬。

7、在一種可能的實現方式中,所述第一晶體管和所述第二晶體管均為n溝道晶體管。

8、在一種可能的實現方式中,所述第一支路包括一個所述第一晶體管,或者所述第一支路包括串聯的至少兩個所述第一晶體管;所述第二支路包括一個所述第二晶體管,或者所述第二支路包括串聯的至少兩個所述第二晶體管。

9、在一種可能的實現方式中,所述射頻開關還包括模擬電路,所述第一晶體管的柵極、所述第一晶體管的體電極、所述第二晶體管的柵極、所述第二晶體管的體電極均與所述模擬電路連接;所述模擬電路用于控制所述第一晶體管和所述第二晶體管的工作狀態,以使所述至少一個通路中的目標通路包括的所述第一支路處于導通狀態時,所述目標通路包括的所述第二支路處于關斷狀態,所述至少一個通路中所述目標通路以外的通路包括的所述第一支路處于關斷狀態,所述至少一個通路中所述目標通路以外的通路包括的所述第二支路處于導通狀態,其中,所述目標通路為所述至少一個通路中的任一所述通路。

10、在一種可能的實現方式中,所述射頻開關中的至少部分所述通路對稱設置。

11、在一種可能的實現方式中,所述第一晶體管的第一特征距離為0.1微米至0.3微米,所述第二晶體管的第一特征距離與所述第一晶體管的第一特征距離的差值為0.2微米至1微米;所述第一晶體管的第二特征距離為0.1微米至0.3微米,所述第二晶體管的第二特征距離與所述第一晶體管的第二特征距離的差值為0.2微米至1微米。

12、根據本申請實施例提供的射頻開關,當射頻開關的任一通路處于導通狀態時,該通路的第一晶體管均處于導通狀態,以使該通路的第一支路導通,且該通路的第二晶體管均處于關斷狀態,以使該通路的第二支路關斷。由此,對于第一晶體管和第二晶體管的第一特征距離相等、且第一晶體管和第二晶體管的第二特征距離相等這一相關方案,由于關斷狀態的晶體管的抗系統級esd能力較差,因此射頻開關的任一通路導通時該通路的第二支路會導致該通路抗系統級esd能力較差,相比于相關方案,本申請實施例中的第二晶體管的第一特征距離大于第一晶體管的第一特征距離,且第二晶體管的第二特征距離大于第一晶體管的第一特征距離,進而,任一通路導通時,該通路包括的第一晶體管的第一特征距離和第二特征距離較小,從而第一晶體管內的導電通道更短,以使第一晶體管的工作性能更好,同時,該通路包括的第二晶體管的第一特征距離和第二特征距離較大,可以使第二晶體管的表面電阻增加,以使第二晶體管的寄生npn開啟后,系統級esd電流的路徑更深,導通更加均勻,從而提高esd的失效電流,以使第二支路的抗系統級esd能力更好,因此該通路的第一支路的工作性能較好,且該通路的第二支路的抗系統級esd能力較好,基于此,相比于相關方案,本申請實施例中的射頻開關在保持正常工作的工作性能較好的前提下,提高了射頻開關的抗系統級esd能力,減小系統級esd事件發生的可能性,以提高射頻開關的工作質量。

技術特征:

1.一種射頻開關,其特征在于,包括:至少一個公共端口、至少一個通路和至少一個非公共端口,所述通路包括第一支路和第二支路;

2.根據權利要求1所述的射頻開關,其特征在于,所述第二晶體管的第一特征距離大于或等于0.3微米,所述第二晶體管的第二特征距離大于或等于0.3微米。

3.根據權利要求1所述的射頻開關,其特征在于,所述第一晶體管包括第一襯底、第一源區、第一漏區、第一體區和第一柵區;

4.根據權利要求1所述的射頻開關,其特征在于,所述第二晶體管包括第二襯底、第二源區、第二漏區、第二體區、第二柵區和抗蝕保護氧化物層;

5.根據權利要求1所述的射頻開關,其特征在于,所述第一晶體管的柵寬大于所述第二晶體管的柵寬。

6.根據權利要求1所述的射頻開關,其特征在于,所述第一晶體管和所述第二晶體管均為n溝道晶體管。

7.根據權利要求1所述的射頻開關,其特征在于,所述第一支路包括一個所述第一晶體管,或者所述第一支路包括串聯的至少兩個所述第一晶體管;

8.根據權利要求1-7中任一項所述的射頻開關,其特征在于,所述射頻開關還包括模擬電路,所述第一晶體管的柵極、所述第一晶體管的體電極、所述第二晶體管的柵極、所述第二晶體管的體電極均與所述模擬電路連接;

9.根據權利要求1所述的射頻開關,其特征在于,所述射頻開關中的至少部分所述通路對稱設置。

10.根據權利要求1所述的射頻開關,其特征在于,

技術總結

本申請實施例涉及開關設計技術領域,尤其涉及一種射頻開關,該射頻開關包括至少一個公共端口、至少一個通路和至少一個非公共端口,通路包括第一支路和第二支路;第一支路的一端連接于任一公共端口,第一支路的另一端連接于任一非公共端口,第一支路包括至少一個第一晶體管;第二支路的一端連接在第一支路與非公共端口之間,第二支路的另一端接地,第二支路包括至少一個第二晶體管;第二晶體管的第一特征距離大于第一晶體管的第一特征距離;第二晶體管的第二特征距離大于第一晶體管的第二特征距離。本方案提高了射頻開關的工作質量。

技術研發人員:鄭海宇,蔡婧怡,葛藝立,段軒

受保護的技術使用者:上海艾為電子技術股份有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!