一種延遲鏈電路、壓降檢測電路、芯片及電子設備的制作方法

本申請屬于電子電路領域,具體涉及一種延遲鏈電路、壓降檢測電路、芯片及電子設備。

背景技術:

1、芯片中的電源電壓通常具有紋波特性:電壓值隨著負載變化而波動。當電壓值小于目標電壓值的時候,芯片中的數字邏輯電路的傳輸延時會增加。如果電壓壓降過大,可能會導致數字邏輯電路的時序無法滿足要求,特殊情況下,電壓壓降過大還可能會引起芯片功能錯誤。為了避免這種情況出現,可以引入動態降頻技術。在電源電壓遇到突發壓降時,如果電壓壓降值超過壓降檢測電路的靈敏度,壓降檢測電路輸出下垂信號而啟動動態降頻技術,以降低數字邏輯電路的工作頻率。

2、而芯片中的電壓壓降值通常和負載存在相關性,具有不固定的特性,使得芯片在使用動態降頻技術時經常無法實現最大的電壓收益。其中,電壓收益是指未啟用動態降頻技術和啟用動態降頻技術下的最低電源電壓之差。

技術實現思路

1、鑒于此,本申請的目的在于提供一種延遲鏈電路、壓降檢測電路、芯片及電子設備,通過調節延遲鏈電路的靈敏度,能夠適應不同的負載變化,能夠支持芯片在使用動態降頻技術時的最大電壓收益。

2、本申請的實施例是這樣實現的:

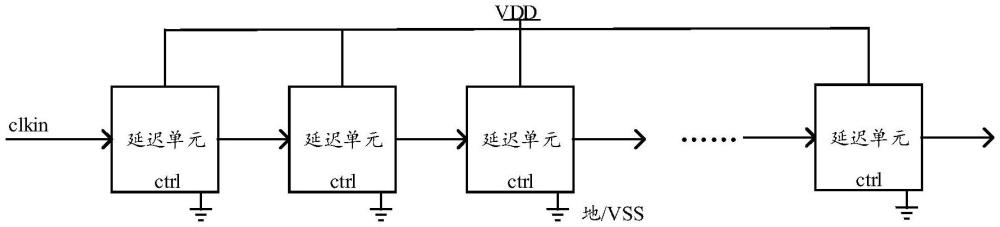

3、第一方面,本申請實施例提供了一種延遲鏈電路,包括:n級延遲單元,每級延遲單元包含一個輸出端和k個輸入端,n為大于等于2的整數,k為大于等于2的整數;第i級延遲單元的至少一個輸入端與第i-1級延遲單元的輸出端連接,i為大于等于2且小于等于n的整數;每級延遲單元的靈敏度可調,每級延遲單元包括并聯的k路延遲支路;所述k路延遲支路包含至少一路可控延遲支路,每路可控延遲支路的狀態包含導通狀態或斷開狀態。

4、在上述實施例中,采用上述結構的延遲鏈電路,使得每級延遲單元的靈敏度可調,可以通過改變每級延遲單元中可控延遲支路的狀態,來調節延遲單元的靈敏度。通過調節延遲鏈電路的靈敏度,能夠適應不同的負載變化,能夠支持芯片在使用動態降頻技術時的最大電壓收益。同時,第i級延遲單元的至少一個輸入端與第i-1級延遲單元的輸出端連接,使得第2級至第n級延遲單元的k個輸入端的輸入信號可以包括全部相同、部分相同、全部不同中的一種,從而適應不同的場景需要。

5、結合第一方面實施例的一種可能的實施方式,所述k路延遲支路還包含固定延遲支路,所述固定延遲支路與所述至少一路可控延遲支路并聯。

6、在上述實施例中,通過采用包含固定延遲支路和至少一路可控延遲支路兩種類型的延遲支路,可以在靈敏度可調的前提下,降低控制難度或減少調節次數。

7、結合第一方面實施例的一種可能的實施方式,每路可控延遲支路包括:可控器件和延遲器件;所述可控器件和延遲器件串聯;所述可控器件用于控制所述可控延遲支路的狀態。

8、在上述實施例中,采用可控器件和延遲器件串聯的方式,使得通過控制可控器件便可控制可控延遲支路的狀態,能夠降低電路的復雜度,便于生產制造。

9、結合第一方面實施例的一種可能的實施方式,所述延遲器件包括:反相器和可調電容電路;所述反相器的輸出端與所述可調電容電路的第一端連接,所述可調電容電路的第二端接地,所述可調電容電路的容值可調;所述可調電容電路用于調節延遲器件的延遲。

10、在上述實施例中,通過將反相器的輸出側連接容值可調的可調電容電路,使得通過調節可調電容電路的容值,即可調節延遲器件的延遲,從而能夠降低電路的復雜度,便于生產制造。

11、結合第一方面實施例的一種可能的實施方式,所述可控器件包括選擇器,多路可控延遲支路復用同一個所述選擇器。

12、在上述實施例中,可以選用選擇器來控制可控延遲支路的狀態,通過復用同一個選擇器來實現多輸入單輸出的效果,以達到節約成本的效果。結合第一方面實施例的一種可能的實施方式,第1級延遲單元的k個輸入端的輸入信號全部相同,第2級至第n級延遲單元的k個輸入端的輸入信號包括部分相同或全部不同。

13、在上述實施例中,第2級至第n級延遲單元的k個輸入端的輸入信號包括部分相同或全部不同,使得可以支持相位前饋技術,例如,以k=3為例,則三個輸入信號中的第一個輸入信號可以為前一級延遲單元的輸出信號、第二個輸入信號可以為前2級延遲單元的輸出信號、第三個輸入信號可以為前3級延遲單元的輸出信號,通過引入前2級或者3級延遲單元的相位(即相位前饋),可以減少延遲單元的延遲,進而提高延遲鏈電路的工作頻率。

14、結合第一方面實施例的一種可能的實施方式,若k=3,i大于等于4時,第i級延遲單元的三個輸入信號包括以下中的一種:所述三個輸入信號均為第i-1級延遲單元的輸出信號;所述三個輸入信號中的第一個輸入信號為第i-1級延遲單元的輸出信號、第二個輸入信號為第i-1級延遲單元的輸出信號、第三個輸入信號為第i-2級延遲單元的輸出信號;所述三個輸入信號中的第一個輸入信號為第i-1級延遲單元的輸出信號、第二個輸入信號為第i-2級延遲單元的輸出信號、第三個輸入信號為第i-2級延遲單元的輸出信號;所述三個輸入信號中的第一個輸入信號為第i-1級延遲單元的輸出信號、第二個輸入信號為第i-2級延遲單元的輸出信號、第三個輸入信號為第i-3級延遲單元的輸出信號。

15、在上述實施例中,若k=3,i大于等于4時,第i級延遲單元的三個輸入信號可以包括上述4種中的一種,從而可以根據延遲需要,通過切換不同的連接方式來調整延遲單元的延遲,以適應各種場景。

16、第二方面,本申請實施例還提供了一種壓降檢測電路,包括:如上述第一方面實施例的任一種可能的實施方式提供的延遲鏈電路、m個鑒相電路以及邏輯電路;所述延遲鏈電路用于對時鐘輸入信號進行延遲,輸出m個延遲信號,m為大于等于1的整數;m個鑒相電路中的每個所述鑒相電路用于接收一個延遲信號和所述時鐘輸入信號,并比較接收的延遲信號和所述時鐘輸入信號之間的相位關系;邏輯電路與每個所述鑒相電路、每級延遲單元連接,所述邏輯電路用于根據所述m個鑒相電路輸出的相位關系調節所述延遲鏈電路中延遲單元的延遲。

17、第三方面,本申請實施例還提供了一種芯片,包括:如上述第二方面實施例提供的壓降檢測電路。

18、第四方面,本申請實施例還提供了一種電子設備,包括:如上述第二方面實施例提供的壓降檢測電路。

19、第五方面,本申請實施例還提供了一種電子設備,其特征在于,包括如上述第三方面實施例提供的芯片。

20、上述第二方面至第五方面實施例所能實現的技術效果,參照第一方面中對應的技術效果,此處不重復說明。

21、本申請的其他特征和優點將在隨后的說明書闡述。本申請的目的和其他優點可通過在所寫的說明書以及附圖中所特別指出的結構來實現和獲得。

技術特征:

1.一種延遲鏈電路,其特征在于,包括:

2.根據權利要求1所述的延遲鏈電路,其特征在于,所述k路延遲支路還包含固定延遲支路,所述固定延遲支路與所述至少一路可控延遲支路并聯。

3.根據權利要求1所述的延遲鏈電路,其特征在于,每路可控延遲支路包括:可控器件和延遲器件;所述可控器件和延遲器件串聯;

4.根據權利要求3所述的延遲鏈電路,其特征在于,所述延遲器件包括:

5.根據權利要求3所述的延遲鏈電路,其特征在于,所述可控器件包括選擇器,多路可控延遲支路復用同一個所述選擇器。

6.根據權利要求1-5中任一項所述的延遲鏈電路,其特征在于,第1級延遲單元的k個輸入端的輸入信號全部相同,第2級至第n級延遲單元的k個輸入端的輸入信號包括部分相同或全部不同。

7.根據權利要求6所述的延遲鏈電路,其特征在于,若k=3,i大于等于4時,第i級延遲單元的三個輸入信號包括以下中的一種:

8.一種壓降檢測電路,其特征在于,包括:

9.一種芯片,其特征在于,包括:如權利要求8所述的壓降檢測電路。

10.一種電子設備,其特征在于,包括:如權利要求1-8中任一項所述的壓降檢測電路。

11.一種電子設備,其特征在于,包括如權利要求9所述的芯片。

技術總結

本申請提供了一種延遲鏈電路、壓降檢測電路、芯片及電子設備,屬于電子電路領域。延遲鏈電路包括:m級延遲單元,每級延遲單元包含一個輸出端和n個輸入端,m為大于等于2的整數,n為大于等于2的整數;第i級延遲單元的至少一個輸入端與第i?1級延遲單元的輸出端連接,i為大于等于2的整數;每級延遲單元的靈敏度可調,每級延遲單元包括并聯的n路延遲支路;所述n路延遲支路包含至少一路可控延遲支路,每路可控延遲支路的狀態包含導通狀態或斷開狀態。通過調節延遲鏈電路的靈敏度,能夠適應不同的負載變化,能夠支持芯片在使用動態降頻技術時的最大電壓收益。

技術研發人員:吳瑞,王文根

受保護的技術使用者:海光信息技術(蘇州)有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!