半導體器件及其制備方法、存儲系統與流程

本申請實施方式涉及半導體,尤其涉及半導體器件及其制備方法、存儲系統。

背景技術:

1、隨著半導體制造工藝的特征尺寸越來越小,存儲器件的存儲密度越來越高,三維存儲器應用而生。為了提升三維存儲器的單位面積的存儲容量,三維存儲器的疊層結構的堆疊層數不斷增加。然而,隨著堆疊層數的增加,溝道孔的深寬比隨之增大,進而導致諸如溝道孔的刻蝕、填充等工藝難度也增大,套刻精度變得難以控制,從而需要引進更先進的機臺,導致成本大幅增加。

2、目前,如何在不大幅增加成本的前提下提高三維存儲器的單位面積的存儲容量是本領域技術人員亟待解決的技術問題之一。

技術實現思路

1、本申請實施方式提供的半導體器件及其制備方法、存儲系統可解決或部分解決現有技術中的上述不足或現有技術中的其他不足。

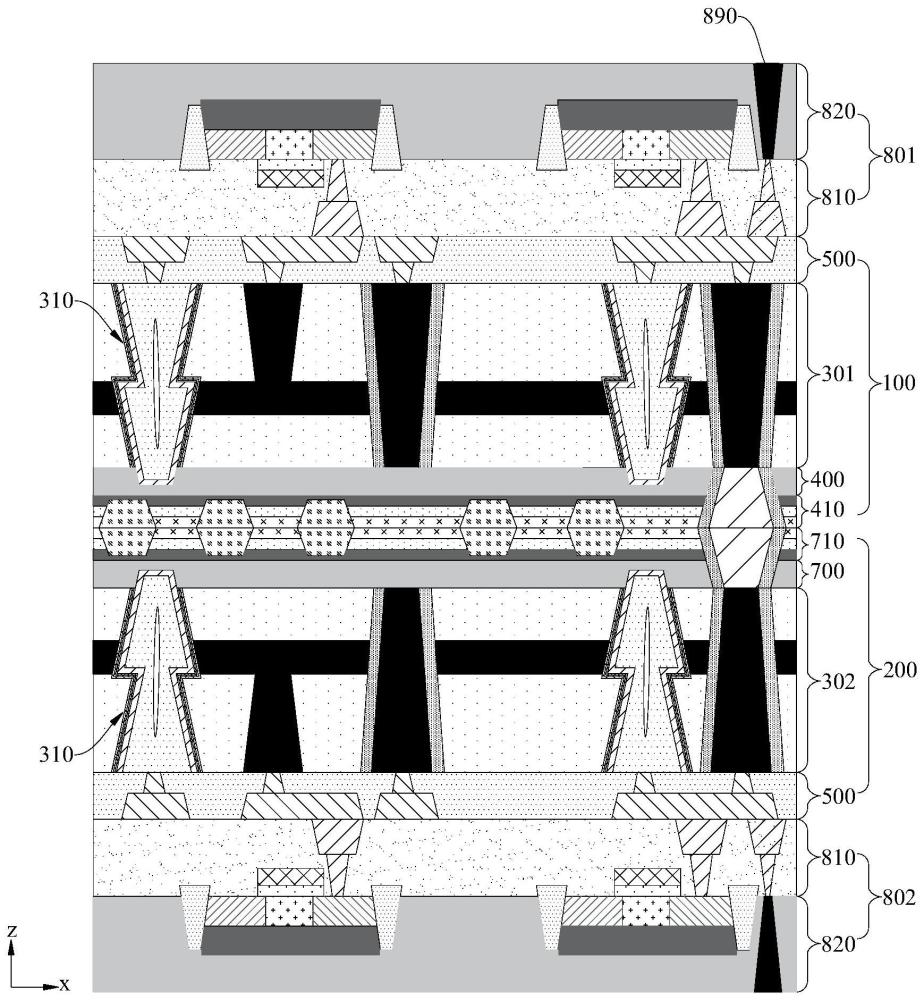

2、根據本申請第一方面提供的半導體器件,包括:

3、第一半導體結構,包括第一存儲陣列以及沿第一方向位于所述第一存儲陣列一側的第一源極結構;以及

4、第二半導體結構,包括第二存儲陣列以及沿所述第一方向位于所述第二存儲陣列一側的第二源極結構,所述第一源極結構和所述第二源極結構鍵合連接。

5、根據本申請第二方面提供的半導體器件的制備方法,包括:

6、形成包括第一存儲陣列和第一源極結構的第一半導體結構,所述第一源極結構沿第一方向位于所述第一存儲陣列的一側;

7、形成包括第二存儲陣列和第二源極結構的第二半導體結構,所述第二源極結構沿所述第一方向位于所述第二存儲陣列的一側;以及

8、將所述第一源極結構和所述第二源極結構進行鍵合。

9、根據本申請第三方面提供的存儲系統,所述存儲系統包括控制器及上述所述的半導體器件,所述控制器耦合至所述半導體器件,且用于控制所述半導體器件存儲數據。

10、本申請實施方式提供的半導體器件通過將第一半導體結構的第一源極結構與第二半導體結構的第二源極結構鍵合連接,換言之,通過實現第一半導體結構和第二半導體結構的共源連接,不僅可以增加整個半導體器件的堆疊層數,進而提升整個半導體器件的單位面積的存儲容量,而且第一半導體結構與第二半導體結構鍵合連接,彼此的形成工藝可以相互獨立,而相比于整個半導體器件來說第一半導體結構和第二半導體結構各自的堆疊層數較少,從而第一半導體結構和第二半導體結構各自的工藝難度較小,在保證套刻精度的前提下可以借助現有的機臺來形成第一半導體結構和第二半導體結構,無需引入更先進的機臺。此外,將第一半導體結構與第二半導體結構進行鍵合還可以實現各個半導體結構彼此之間的應力平衡。

11、應當理解,本部分所描述的內容并非旨在標識本申請的實施例的關鍵或重要特征,也不用于限制本申請的范圍。本申請的其它特征將通過以下的說明書而變得容易理解。

技術特征:

1.一種半導體器件,其特征在于,包括:

2.根據權利要求1所述的半導體器件,其中,所述第一源極結構包括第一源極層以及位于所述第一源極層遠離所述第一存儲陣列一側的第一鍵合層,所述第一鍵合層內設置有第一鍵合觸點,所述第二源極結構包括第二源極層以及位于所述第二源極層遠離所述第二存儲陣列一側的第二鍵合層,所述第二鍵合層內設置有第二鍵合觸點,所述第一鍵合觸點與所述第二鍵合觸點接觸。

3.根據權利要求2所述的半導體器件,其中,所述第一鍵合層包括第一導電阻擋層和第一絕緣層,所述第一導電阻擋層位于第一源極層和所述第一絕緣層之間,所述第一鍵合觸點沿所述第一方向貫穿所述第一絕緣層并延伸至所述第一導電阻擋層內;和/或

4.根據權利要求3所述的半導體器件,其中,所述第一導電阻擋層和/或所述第二導電阻擋層的材料包括金屬硅化物和/或金屬。

5.根據權利要求2所述的半導體器件,其中,所述第一鍵合層包括第一絕緣層和第一介質阻擋層,所述第一介質阻擋層位于所述第一絕緣層遠離所述第一源極層的一側,所述第一鍵合觸點沿所述第一方向貫穿所述第一介質阻擋層和所述第一絕緣層;和/或

6.根據權利要求5所述的半導體器件,其中,所述第一介質阻擋層和/或所述第二介質阻擋層的材料包括氮化硅和/或摻雜氮化硅。

7.根據權利要求1所述的半導體器件,其中,所述第一源極結構包括第一源極層以及位于所述第一源極層內的第一導電結構,所述第一導電結構沿垂直于所述第一方向的第二方向延伸,所述第二源極結構包括第二源極層以及位于所述第二源極層內的第二導電結構,所述第二導電結構沿垂直于所述第二方向延伸,所述第一導電結構與所述第二導電結構接觸。

8.根據權利要求7所述的半導體器件,其中,所述第一導電結構包括沿所述第二方向延伸的第一連接部以及與所述第一連接部連接的至少一個第一導電凸起,所述第一導電凸起位于所述第一連接部朝向所述第一存儲陣列的一側,所述第一連接部遠離所述第一存儲陣列的一側暴露于所述第一源極層的表面;和/或

9.根據權利要求8所述的半導體器件,其中,沿所述第一方向、所述第一導電凸起朝遠離所述第一連接部的方向貫穿所述第一源極層;和/或

10.根據權利要求8所述的半導體器件,其中,所述第一源極層內沿所述第二方向間隔分布有多個所述第一連接部,和/或,所述第二源極層內沿所述第二方向間隔分布有多個所述第二連接部。

11.根據權利要求10所述的半導體器件,其中,相鄰兩個所述第一連接部和/或所述相鄰兩個所述第二連接部之間設置有絕緣部。

12.根據權利要求1至11任一項所述的半導體器件,其中,所述第一存儲陣列和所述第二存儲陣列均包括:

13.根據權利要求12所述的半導體器件,其中,所述第一存儲陣列的所述溝道結構和所述第二存儲陣列的所述溝道結構的所述第一端均相對其所述第二端靠近或者遠離所述第一源極結構;或者,

14.根據權利要求12所述的半導體器件,其中,所述第一存儲陣列遠離所述第一源極結構的一側設置有第三半導體結構,所述第三半導體結構包括與所述第一存儲陣列連接的第一外圍電路;和/或

15.根據權利要求14所述的半導體器件,其中,所述第一存儲陣列包括第一接觸結構,所述第一接觸結構的一端與所述第一源極結構連接,另一端與所述第一外圍電路連接;和/或

16.根據權利要求14所述的半導體器件,其中,所述堆疊結構包括沿所述第一方向交替堆疊的第三絕緣層和柵極層;

17.一種半導體器件的制備方法,其特征在于,包括:

18.根據權利要求17所述的半導體器件的制備方法,其中,形成包括第一存儲陣列和第一源極結構的第一半導體結構和/或形成包括第二存儲陣列和第二源極結構的第二半導體結構包括:

19.根據權利要求18所述的半導體器件的制備方法,其中,在所述源極層遠離所述存儲陣列的一側形成鍵合層包括:

20.根據權利要求18所述的半導體器件的制備方法,其中,在所述源極層遠離所述存儲陣列的一側形成鍵合層包括:

21.根據權利要求16所述的半導體器件的制備方法,其中,形成包括第一存儲陣列和第一源極結構的第一半導體結構和/或形成包括第二存儲陣列和第二源極結構的第二半導體結構包括:

22.根據權利要求21所述的半導體器件的制備方法,其中,所述源極層遠離所述存儲陣列的表面包括第一區域以及位于所述第一區域內的至少一個第二區域;

23.一種存儲系統,其特征在于,所述存儲系統包括控制器及權利要求1至16中任一項所述的半導體器件,所述控制器耦合至所述半導體器件,且用于控制所述半導體器件存儲數據。

技術總結

本申請公開了一種半導體器件及其制備方法、存儲系統。該半導體器件包括:第一半導體結構,包括第一存儲陣列以及沿第一方向位于第一存儲陣列一側的第一源極結構;以及第二半導體結構,包括第二存儲陣列以及沿第一方向位于第二存儲陣列一側的第二源極結構,第一源極結構和第二源極結構鍵合連接。該制備方法包括:形成包括第一存儲陣列和第一源極結構的第一半導體結構,第一源極結構沿第一方向位于第一存儲陣列的一側;形成包括第二存儲陣列和第二源極結構的第二半導體結構,第二源極結構沿第一方向位于第二存儲陣列的一側;以及將第一源極結構和第二源極結構進行鍵合。

技術研發人員:張坤,高庭庭,周文犀,夏志良,霍宗亮

受保護的技術使用者:長江存儲科技有限責任公司

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!