一種含失調校正的高速模擬比較器電路

本發明涉及集成電路,特別是涉及一種含失調校正的高速模擬比較器電路。

背景技術:

1、在目前流行的模數轉換器(adc,analog?to?digital?converter)技術中,逐次逼近型(sar,successiveapproximation?register)adc憑借低功耗,高精度,面積小和結構相對簡單,在模數混合信號處理系統中得到廣泛應用。比較器作為saradc的核心模塊,其速度、精度、功耗已經逐漸成為saradc發展的瓶頸。由于工藝和電路架構的限制,當運行速度在超ghz以上的adc中,比較器的速度完全決定了adc的總采樣速率,其延時也就成為了關鍵指標。另外,在高精度的adc中,比較器的失調導致比較器無法比較兩個相近電壓值,降低了靈敏度,影響了adc的精度。

2、adc在目前混合信號處理系統中發揮著模擬到數字域的橋梁作用,影響著信號的處理質量和信噪比。高速低失調比較器的設計對于實現高性能adc至關重要。它不僅需要快速響應輸入信號的變化,以滿足高速采樣的需求,同時還要在保持高速度的同時減少失調,以提高信號處理能力。

3、目前常用的比較器可分為靜態比較器和動態比較器兩種,靜態比較器通常是運算放大器的開環應用,器件相對較少,結構簡單,不需要頻率補償,但響應速度不夠快,輸出共模不易確定,工作時功耗大,在現在的adc應用中逐漸被動態比較器所替代。與靜態比較器相比,動態比較器幾乎不存在功耗,且比較速度更快,但卻存在較大的電壓失調。目前傳統的高速動態比較器有strongarm鎖存比較器,雙尾電流鎖存比較器,兩級鎖存比較器和三級鎖存比較器等,采用一個或多個預放大級和鎖存器串聯的結構,通過預放大級的高帶寬和增益來進行小信號放大,然后利用鎖存器進行大信號的正向反饋放大并鎖存。但由于小信號增益很有限,比較器延時很難減小到50ps以內,外加通過堆疊鎖存結構加速的方式,使得比較器的電壓余量減小,在低壓納米下設計很困難。三級鎖存比較器雖然提高了小信號的增益,但由于級聯級數的增多,增加了延時和失調,很難滿足高速高精度adc設計的需求。

技術實現思路

1、本發明所要解決的技術問題是提供一種含失調校正的高速模擬比較器電路,能夠滿足高速高精度adc設計的需求。

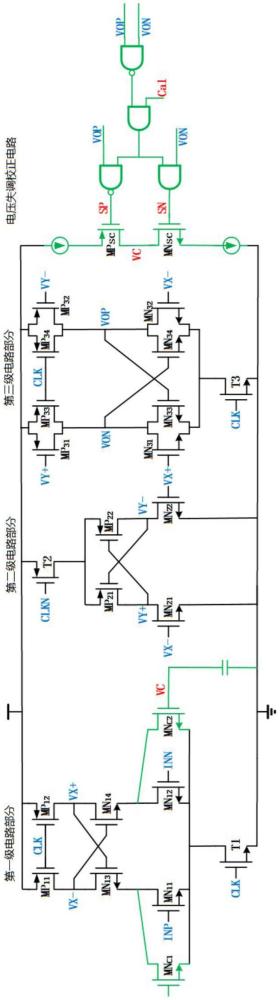

2、本發明解決其技術問題所采用的技術方案是:提供一種含失調校正的高速模擬比較器電路,包括三級信號放大級電路和電壓失調校正電路,所述三級信號放大級電路包括級聯的第一級電路部分、第二級電路部分和第三級電路部分;所述第一級電路部分用于提供一個增益來衰減所述第二級電路部分和第三級電路部分的噪聲、失調和回踢;所述第二級電路部分用于以指數方式增加信號的差分輸出;所述第三極電路部分采用雙向鎖存結構來最小化再生時間;所述第一級電路部分還連接有輔助輸入支路;所述電壓失調校正電路用于在校正模式下通過檢測所述三級信號放大級電路的輸出來對所述輔助輸入支路的電容進行充放電,以控制所述輔助支路的共模電平來減小電壓失調。

3、所述第一級電路部分包括第一nmos管、第二nmos管、第三nmos管、第四nmos管、第一pmos管、第二pmos管和第一控制管;所述第一nmos管的柵極作為所述第一級電路部分的第一輸入端,源極與所述第一控制管的漏極相連,漏極與所述第三nmos管的源極相連;所述第二nmos管的柵極作為所述第一級電路部分的第二輸入端,源極與所述第一控制管的漏極相連,漏極與所述第四nmos管的源極相連;所述第三nmos管的柵極與所述第一級電路部分的第一輸出端相連,漏極與所述第一pmos管的漏極相連,并作為所述第一級電路部分的第二輸出端;所述第四nmos管的柵極與所述第一級電路部分的第二輸出端相連,漏極與所述第二pmos管的漏極相連,并作為所述第一級電路部分的第一輸出端;所述第一pmos管的柵極連接時鐘信號,源極與電源端相連,所述第二pmos管的柵極連接時鐘信號,源極與電源端相連;所述第一控制管的柵極連接時鐘信號,源極接地。

4、所述輔助輸入支路包括第一輔助nmos管和第二輔助nmos管,所述第一輔助nmos管的漏極與所述第一nmos管的漏極相連,源極與所述第一控制管的漏極相連;所述第二輔助nmos管的柵極與電容的一端,漏極與所述第二nmos管的漏極相連,源極與所述第一控制管的漏極相連;所述電容的另一端接地。

5、所述第二級電路部分包括第五nmos管、第六nmos管、第三pmos管、第四pmos管和第二控制管,所述第五nmos管的柵極與所述第一級電路部分的第二輸出端相連,漏極與所述第三pmos管的漏極相連,并作為所述第二級電路部分的第一輸出端,源極接地;所述第六nmos管的柵極與所述第一級電路部分的第一輸出端相連,漏極與所述第四pmos管的漏極相連,并作為所述第二級電路部分的第二輸出端,源極接地;所述第三pmos管的柵極與所述第二級電路部分的第二輸出端相連,源極與所述第二控制管的漏極相連;所述第四pmos管的柵極與所述第二級電路部分的第一輸出端相連,源極與所述第二控制管的漏極相連;所述第二控制管的柵極連接時鐘信號的反相信號,源極與電源端相連。

6、所述第三極電路部分包括第七nmos管、第八nmos管、第九nmos管、第十nmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管和第三控制管,所述第七nmos管的柵極與所述第一級電路部分的第一輸出端相連,漏極與所述第九nmos管的漏極相連,并作為所述第三極電路部分的第二輸出端,源極與所述第三控制管的漏極相連;所述第八nmos管的柵極與所述第一級電路部分的第二輸出端相連,漏極與所述第十nmos管的漏極相連,并作為所述第三極電路部分的第一輸出端,源極與所述第三控制管的漏極相連;所述第九nmos管的柵極與所述第三極電路部分的第一輸出端相連,漏極與所述第五pmos管的漏極相連,源極與所述第三控制管的漏極相連;所述第十nmos管的柵極與所述第三極電路部分的第二輸出端相連,漏極與所述第六pmos管的漏極相連,源極與所述第三控制管的漏極相連;所述第五pmos管的柵極與第二級電路部分的第一輸出端相連,漏極與所述第七pmos管的漏極相連,源極與電源端相連;所述第六pmos管的柵極與第二級電路部分的第二輸出端相連,漏極與所述第八pmos管的漏極相連,源極與電源端相連;所述第七pmos管的柵極連接時鐘信號,源極與電源端相連;所述第八pmos管的柵極連接時鐘信號,源極與電源端相連。

7、所述電壓失調校正電路包括第一與非門、第二與非門、第一與門、第二與門、失調校正pmos管、失調校正nmos管、第一電流源和第二電流源;所述第一與非門的第一輸入端與所述第三極電路部分的第一輸出端相連,第二輸入端與所述第三極電路部分的第二輸出端相連,輸出端與所述第一與門的第一輸入端相連;所述第一與門的第二輸入端連接cal信號,輸出端分別與所述第二與非門的第二輸入端和第二與門的第二輸入端相連;所述第二與非門的第一輸入端與所述第三極電路部分的第一輸出端相連,輸出端與所述失調校正pmos管的柵極相連;所述第二與門的第一輸入端與所述第三極電路部分的第二輸出端相連,輸出端與所述失調校正nmos管的柵極相連;所述失調校正pmos管的源極與所述第一電流源的正極相連,漏極與所述失調校正nmos管的漏極相連;所述失調校正nmos管的源極與所述第二電流源的負極相連;所述失調校正nmos管的漏極還與所述輔助輸入支路的電容相連;所述第一電流源的負極與電源端相連,所述第二電流源的正極接地。

8、有益效果

9、由于采用了上述的技術方案,本發明與現有技術相比,具有以下的優點和積極效果:本發明通過輔助支路校正比較器失調電壓的設計,減小比較器的失調,失調控制在1mv以內,使其能夠在高速高精度adc設計中得到使用。另外,本發明還通過增加信號的前饋通路,減少小信號的轉化時間,結合前饋通路和直接通路的高增益,使得比較器在原來三級放大的基礎上兼具二級低延時的優勢,將比較器延遲控制在30ps左右,可以用于10ghz以上的高速比較。本發明通過與鎖存器水平級聯而不是垂直堆疊的方式,增加了比較器的電壓余量,使得本發明電路架構可以在更加先進的工藝中得到應用。

- 還沒有人留言評論。精彩留言會獲得點贊!