具有雙電源的集成電路器件的制作方法

本公開總體上涉及集成電路器件領域,并且更具體地,涉及具有雙電源的集成電路器件。

背景技術:

1、集成電路(ic)器件、芯片和/或塊可以從一個或多個外部源(例如,電源和數據源)接收電力和數據信號作為操作的一部分。一些ic器件可以經由前側(fs)導電結構接收電力和數據信號。例如,ic器件可以包括fs配電網絡(fspdn),其具有在后段工藝(beol)過程期間形成的一個或多個部件,并且用于數據信號的導電結構可以與fspdn在ic器件的同一側上。ic器件可以包括各種晶體管結構,包括例如二維(2d)平面結構、鰭式場效應晶體管、柵極環繞晶體管、多橋溝道fet(mbcfettm)和堆疊晶體管(例如,三維(3d)堆疊晶體管)。

2、最近,還開發了背側pdn(bspdn)其中ic器件的襯底的背側用作配電網絡(pdn)。例如,電力軌可以用在ic器件的bspdn中,并且可以在襯底的與ic器件的有源部件(例如,晶體管)相對的一側上。此外,用于數據信號的導電結構可以在ic器件的fs上,因此bspdn和用于數據信號的導電結構可以在ic器件的相反側上。

3、無論提供fs電力還是bs電力,使用單個電源都可能難以控制功耗。ic器件的常規塊可以被設計為單獨的高電壓塊和低電壓塊,其中每個塊接收單個電壓(高電壓或低電壓)。因此,可能需要基于電壓電平來設計和/或分離常規塊。

技術實現思路

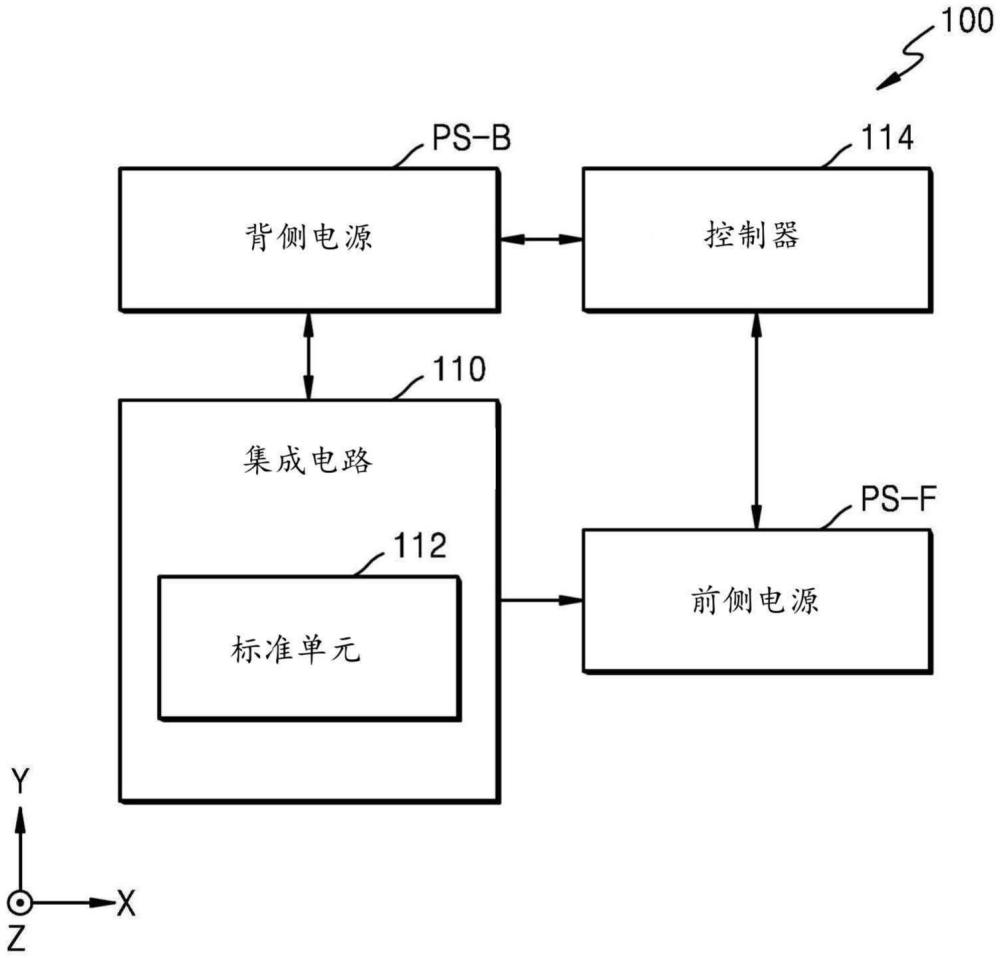

1、根據本文的一些實施例,集成電路器件可以包括垂直晶體管堆疊,該垂直晶體管堆疊包括具有第一導電類型的第一晶體管和具有不同于第一導電類型的第二導電類型的第二晶體管。例如,該器件可以是互補金屬氧化物半導體(cmos)器件,第一晶體管可以是p型金屬氧化物半導體(pmos)晶體管,并且第二晶體管可以是n型金屬氧化物半導體(nmos)晶體管。此外,cmos器件可包括分別耦合到前側(fs)電力軌和后側(bs)電力軌的第一電源和第二電源,其中前側和后側電力軌兩者都耦合到pmos晶體管。

2、根據本文的一些實施例,集成電路器件可以包括具有pmos晶體管和nmos晶體管的襯底。集成電路器件可以包括均耦合到pmos晶體管的前側(fs)電力軌和背側(bs)電力軌。集成電路器件可以包括fs電源和bs電源,fs電源和bs電源分別經由fs電力軌和bs電力軌耦合到pmos晶體管。此外,cmos器件可以包括耦合到fs電源和bs電源的控制器。控制器可以被配置為在bs電源被停用時激活fs電源,并且還可以被配置為在fs電源被停用時激活bs電源。

3、根據本文的一些實施例,集成電路器件可以包括垂直晶體管堆疊,該垂直晶體管堆疊包括第一晶體管和第二晶體管。所述集成電路器件可包括被配置為供應具有第一電壓的第一電力信號的第一電源及被配置為供應具有高于所述第一電壓的第二電壓的第二電力信號的第二電源。第一電源和第二電源都可以耦合到第一晶體管。此外,cmos器件可以包括耦合到第一電源和第二電源的控制器。控制器可以被配置為在第二電源被關閉時接通第一電源,并且還可以被配置為在第一電源被關閉時接通第二電源。

技術特征:

1.一種互補金屬氧化物半導體cmos器件,包括:

2.根據權利要求1所述的cmos器件,其中所述第一晶體管是pmos晶體管,并且所述第二晶體管是nmos晶體管。

3.根據權利要求1所述的cmos器件,

4.根據權利要求1所述的cmos器件,還包括信號線,

5.根據權利要求1所述的cmos器件,

6.根據權利要求1所述的cmos器件,還包括第一前側金屬線和第二前側金屬線,

7.根據權利要求1所述的cmos器件,還包括第一電源和第二電源,所述第一電源和所述第二電源分別經由所述第一電力軌和所述第二電力軌耦合到所述第一晶體管。

8.根據權利要求7所述的cmos器件,

9.根據權利要求7所述的cmos器件,其中,在所述第二電源不活動時所述第一電源被配置為活動,并且

10.根據權利要求9所述的cmos器件,還包括耦合到所述第一電源和所述第二電源兩者的控制器,

11.根據權利要求7所述的cmos器件,

12.根據權利要求1所述的cmos器件,

13.一種互補金屬氧化物半導體cmos器件,包括:

14.根據權利要求13所述的cmos器件,其中,所述pmos晶體管和所述nmos晶體管被布置為在所述垂直方向上彼此重疊。

15.根據權利要求13所述的cmos器件,其中,所述pmos晶體管和所述nmos晶體管被布置為在水平方向上彼此重疊。

16.根據權利要求13所述的cmos器件,

17.根據權利要求13所述的cmos器件,其中所述雙電力軌包括第一電力軌和第二電力軌,所述第一電力軌和所述第二電力軌兩者都耦合到所述pmos晶體管并且在所述垂直方向上布置在所述pmos晶體管的所述相反側上,并且

18.一種互補金屬氧化物半導體cmos器件,包括:

19.根據權利要求18所述的cmos器件,還包括:

20.根據權利要求19所述的cmos器件,

技術總結

提供了CMOS器件。CMOS器件包括PMOS晶體管和NMOS晶體管。此外,CMOS器件包括雙電力軌,所述雙電力軌具有前側電力軌和后側電力軌,前側電力軌和后側電力軌兩者都耦合到PMOS晶體管或NMOS晶體管中的一者。PMOS晶體管和NMOS晶體管在垂直晶體管堆疊中,或者并排。

技術研發人員:金珍泰,樸判濟,徐康一

受保護的技術使用者:三星電子株式會社

技術研發日:

技術公布日:2025/4/24

- 還沒有人留言評論。精彩留言會獲得點贊!