一種高速信號測試電路及測試方法與流程

本申請屬于信號測試領域,更具體地,涉及一種高速信號測試電路及測試方法。

背景技術:

1、在驗證高速信號性能、解決高速信號出現的問題時,進行信號測試是業界普遍使用的方法。測試高速信號會用到高速示波器及探頭,在待測設備上找到合適的測試點位,使用探頭將信號從測試點位引入高速示波器中,就可以通過測試眼圖、協議一致性測試等方法來判定待測設備的高速信號質量是否合格。

2、若待測設備上預留有測試點,則通過焊接或點觸的方式將探頭和測試點連接后進行信號測試;又或待測設備上高速信號通道一般會有ac電容,可通過焊接或點觸的方式將探頭和ac電容的焊盤連接后進行信號測試。點觸后進行信號測試的測試方案存在信號不穩定的問題,焊接后進行信號測試的測試方案存在切換操作困難的問題,目前尚沒有一種操作方便且測試信號穩定的測試方案。

技術實現思路

1、針對現有技術的以上缺陷或改進需求,本申請提供了一種高速信號測試電路及測試方法,其目的在于解決目前測試方案無法兼顧操作方便和測試信號穩定的技術問題。

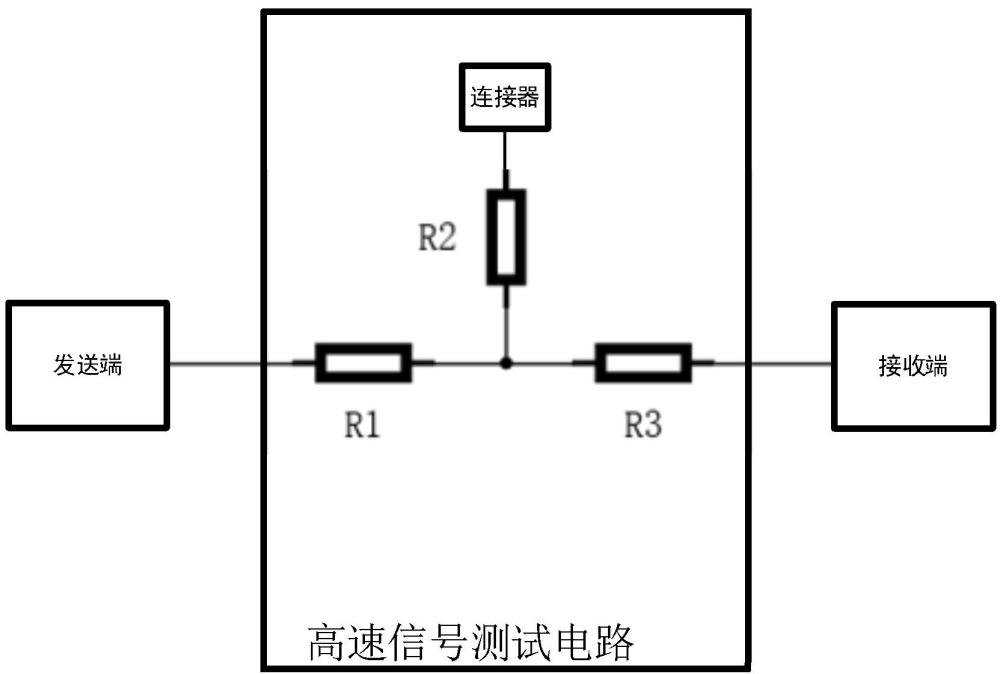

2、為實現上述目的,第一方面,本申請提供了一種高速信號測試電路,所述高速信號測試電路包括電阻網絡,所述電阻網絡包括第一電阻、第二電阻、第三電阻和連接器,所述第一電阻的第一端連接高速信號的發送端,所述第三電阻的第一端連接高速信號的接收端,所述第二電阻的第一端和連接器的第一端相連,所述連接器的第二端接地,所述第一電阻、第二電阻和第三電阻的第二端相連;

3、所述連接器為凹形結構,和示波器探頭轉接器的凸型結構互補匹配。

4、優選的,所述連接器為smp射頻連接器或smpm射頻連接器。

5、優選的,所述第一電阻、第二電阻和第三電阻構成t型電阻網絡,確保高速信號的信號源輸出阻抗、負載輸入阻抗和連接線特征阻抗之間滿足阻抗匹配。

6、優選的,所述第一電阻、第二電阻和第三電阻組成的t型電阻網絡的等效阻抗為:

7、ω

8、其中,第二電阻和第三電阻的阻值相等。

9、優選的,其中,第一電阻、第二電阻和第三電阻的阻值小于等于歐姆。

10、優選的,所述高速信號測試電路的pcb布局中,連接器和第二電阻之間的走線盡量短,第一電阻和第三電阻之間的連線到第二電阻之間的走線盡量短。

11、優選的,所述高速信號測試電路的pcb布局中,連接器焊盤和電阻焊盤下層的gnd層內,位于焊盤下方區域的銅箔被去除。

12、優選的,所述高速信號為高速差分信號,差分結構的兩條線路均設置有所述電阻網絡。

13、第二方面,本申請提供了一種信號驅動與檢測設備,包括如第一方面所述的高速信號測試電路。

14、第三方面,本申請提出了一種如第一方面所述高速信號測試電路的測試方法,包括調節第二電阻的阻值,直至連接器輸出的高速信號質量最優。

15、總體而言,通過本申請所構思的以上技術方案與現有技術相比,具有以下有益效果:

16、(1)本申請通過連接器將高速信號引至高速示波器進行信號測試,連接器和示波器探頭轉接器的接口結構互補匹配,方便示波器探頭和連接器的連接斷開,并且信號穩定,由此克服了通過點觸或焊接將高速信號引至高速示波器所帶來的信號不穩定或切換操作困難的問題。

17、(2)本申請中三電阻組成的t型電阻網絡,通過調整其中電阻的阻值確保信號源、連接線和負載之間阻抗匹配,減少測試電路對所采集高速信號的影響。

18、(3)本申請中t型電阻網絡的第二電阻可調,由此可在測試過程中微調增加第二電阻的阻值,抵消接收端和信號發送端之間由轉接造成的阻抗增加。

19、(4)本申請高速信號測試電路的pcb布局中,通過對其中分支段的長度限定優化,電阻焊盤、連接器焊盤下層gnd層的挖空優化,走線布局優化,進一步確保了信號源和負載之間阻抗匹配。

技術特征:

1.一種高速信號測試電路,其特征在于,所述高速信號測試電路包括電阻網絡,所述電阻網絡包括第一電阻、第二電阻、第三電阻和連接器,所述第一電阻的第一端連接高速信號的發送端,所述第三電阻的第一端連接高速信號的接收端,所述第二電阻的第一端和連接器的第一端相連,所述連接器的第二端接地,所述第一電阻、第二電阻和第三電阻的第二端相連;

2.根據權利要求1所述的高速信號測試電路,其特征在于,所述連接器為smp射頻連接器或smpm射頻連接器。

3.根據權利要求1所述的高速信號測試電路,其特征在于,所述第一電阻、第二電阻和第三電阻構成t型電阻網絡,確保高速信號的信號源輸出阻抗、負載輸入阻抗和連接線特征阻抗之間滿足阻抗匹配。

4.根據權利要求1或3所述的高速信號測試電路,其特征在于,所述第一電阻、第二電阻和第三電阻組成的t型電阻網絡的等效阻抗為:

5.根據權利要求4所述的高速信號測試電路,其特征在于,其中,第一電阻、第二電阻和第三電阻的阻值小于等于歐姆。

6.根據權利要求1所述的高速信號測試電路,其特征在于,所述高速信號測試電路的pcb布局中,連接器和第二電阻之間的走線盡量短,第一電阻和第三電阻之間的連線到第二電阻之間的走線盡量短。

7.根據權利要求1所述的高速信號測試電路,其特征在于,所述高速信號測試電路的pcb布局中,連接器焊盤和電阻焊盤下層的gnd層內,位于焊盤下方區域的銅箔被去除。

8.根據權利要求1所述的高速信號測試電路,其特征在于,所述高速信號為高速差分信號,差分結構的兩條線路均設置有所述電阻網絡。

9.一種信號驅動與檢測設備,其特征在于,包括如權利要求1-8所述的高速信號測試電路。

10.一種如權利要求1-8所述高速信號測試電路的測試方法,其特征在于,包括調節第二電阻的阻值,直至連接器輸出的高速信號質量最優。

技術總結

本申請屬于信號測試領域,具體公開了一種高速信號測試電路及測試方法。本申請測試電路中包括第一電阻、第二電阻、第三電阻和連接器,所述第一電阻的第一端連接高速信號的發送端,所述第三電阻的第一端連接高速信號的接收端,所述第二電阻的第一端和連接器的第一端相連,所述連接器的第二端接地,所述第一電阻、第二電阻和第三電阻的第二端相連;所述連接器為凹形結構,和示波器探頭轉接器的凸型結構互補匹配,連接器和探頭轉接器連接后將高速信號引入示波器進行測試。本申請方案克服了通過點觸或焊接將高速信號引至示波器所帶來的信號不穩定或切換操作困難的問題。

技術研發人員:李威,張春梅

受保護的技術使用者:武漢精立電子技術有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!