電路板組件和顯示裝置的制作方法

本技術涉及顯示,具體涉及一種電路板組件和顯示裝置。

背景技術:

1、在印刷電路板組件(printed?circuit?board?assembly,pcba)中,會存在兩個主控元器件、多個存儲芯片(flash)、電平轉換芯片(lvevl?shift?ic)、以及燒錄接口。其中,主控元器件可以是可編程門陣列芯片(field?programmable?gate?array、fpga)、時序控制芯片(timer?control?register,tcon)。在相關技術的印刷電路板組件中,時序控制芯片和存儲芯片位于可編程門陣列芯片在印刷電路板(printed?circuit?board,pcb)長度方向的兩側。

2、在對印刷電路板組件進行燒錄的過程中,會存在燒錄失敗的情況。引起該現象的原因是:電性連接時序控制芯片與存儲芯片的串行外設接口總線(serial?peripheralinterface,spi)的走線長度較長,導致時序控制芯片與存儲芯片之間的通訊信號受到較多其他信號(如電平轉換芯片輸出的goa信號)的干擾,造成時序控制芯片與存儲芯片的信號傳輸不穩定。

3、故,有必要提出一種新的技術方案,以解決上述技術問題。

技術實現思路

1、本技術的目的在于提供一種電路板和顯示裝置,可以縮減電性連接時序控制芯片與存儲芯片的串行外設接口總線的長度,從而縮短時序控制芯片與存儲芯片之間的通訊信號傳輸路徑,以提高時序控制芯片與存儲芯片的信號傳輸的穩定性。

2、為解決上述問題,本技術的技術方案如下:

3、第一方面,本技術提出了一種電路板組件,包括:

4、電路板,包括第一串行外設接口總線,所述第一串行外設接口總線包括多條第一子線;

5、時序控制器,設于所述電路板上;以及

6、第一存儲器,設于所述電路板上;

7、其中,多條所述第一子線電性連接所述時序控制器和所述第一存儲器,所述第一子線的長度小于或等于9000密爾。

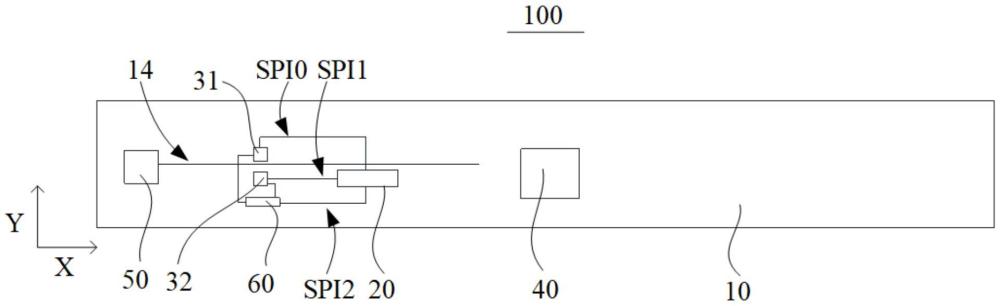

8、在本技術的一實施例中,所述電路板組件還包括可編程門陣列芯片,所述可編程門陣列芯片設于所述電路板上;

9、在所述電路板組件的平面視圖中,所述時序控制器位于所述第一存儲器和所述可編程門陣列芯片之間,所述時序控制器與所述第一存儲器的間距小于所述時序控制器與所述可編程門陣列芯片的間距。

10、在本技術的一實施例中,在所述電路板組件的平面視圖中,所述第一存儲器和所述可編程門陣列芯片分別位于所述時序控制器在所述電路板的長邊方向的兩側;

11、所述第一子線的長度小于或等于3000密爾。

12、在本技術的一實施例中,多條所述第一子線包括:

13、第一數據輸入信號線,電性連接所述時序控制器和所述第一存儲器;

14、第一數據輸出信號線,電性連接所述時序控制器和所述第一存儲器;

15、第一時鐘信號線,電性連接所述時序控制器和所述第一存儲器;以及

16、第一片選信號線,電性連接所述時序控制器和所述第一存儲器;

17、其中,所述第一數據輸入信號線、所述第一數據輸出信號線、所述第一時鐘信號線、所述第一片選信號線中的任意兩者的長度差值的絕對值小于20密爾。

18、在本技術的一實施例中,多條所述第一子線還包括:

19、第一寫保護輸入信號線,電性連接所述時序控制器和所述第一存儲器;

20、第一狀態維持輸入信號線,電性連接所述時序控制器和所述第一存儲器;

21、其中,所述第一數據輸入信號線、所述第一數據輸出信號線、所述第一時鐘信號線、所述第一片選信號線、所述第一寫保護輸入信號線、所述第一狀態維持輸入信號線中的任意兩者的長度差值的絕對值小于10密爾。

22、在本技術的一實施例中,所述電路板組件還包括電平轉換器,所述電平轉換器設于所述電路板上,并與所述時序控制器電性連接;

23、在所述電路板組件的平面視圖中,所述第一存儲器位于所述電平轉換器和所述時序控制器之間;

24、所述電路板包括沿所述電路板的厚度方向層疊設置的第一走線層、參考地層以及第二走線層;

25、所述第一走線層包括所述第一串行外設接口總線;

26、所述參考地層分別與所述第一走線層、所述第二走線層絕緣,所述參考地層接入參考地電位;

27、所述第二走線層包括行驅動信號總線,所述行驅動信號總線與所述電平轉換器電性連接,所述行驅動信號總線被配置為向顯示面板輸出行驅動信號。

28、在本技術的一實施例中,所述行驅動信號總線包括多條第二子線,所述第二子線被配置為向顯示面板輸出行驅動信號;

29、至少一條所述第一子線在所述參考地層上的正投影與至少一條所述第二子線在所述參考地層上的正投影交叉;和/或,

30、多條所述第二子線在所述參考地層上的正投影間隔設置,相鄰兩條所述第二子線在所述參考地層上的正投影之間形成間隙,至少一個所述間隙與所述第一子線在所述參考地層上的正投影不完全重疊。

31、在本技術的一實施例中,所述電路板組件還包括第二存儲器,所述第二存儲器設于所述電路板上;

32、在所述電路板組件的平面視圖中,所述第二存儲器位于所述電平轉換器和所述時序控制器之間,所述第二存儲器和所述第一存儲器沿所述電路板的短邊方向間隔設置;

33、所述第一走線層還包括第二串行外設接口總線,所述第二串行外設接口總線電性連接所述時序控制器和所述第二存儲器,所述第二串行外設接口總線與所述第一串行外設接口總線間隔設置在所述參考地層遠離所述第二走線層的一側;

34、所述第二串行外設接口總線包括多條第三子線,所述第三子線電性連接所述時序控制器和所述第二存儲器;

35、所述行驅動信號總線包括多條第二子線,所述第二子線被配置為向顯示面板輸出行驅動信號;

36、至少一條所述第三子線在所述參考地層上的正投影與至少一條所述第二子線在所述參考地層上的正投影交叉;和/或,

37、多條所述第二子線在所述參考地層上的正投影間隔設置,相鄰兩條所述第二子線在所述參考地層上的正投影之間形成間隙,至少一個所述間隙與所述第三子線在所述參考地層上的正投影不完全重疊。

38、在本技術的一實施例中,所述電路板包括第一區域,所述第一區域包括近端區域和位于所述近端區域至少一側的遠端區域,所述時序控制器和所述第一存儲器位于所述近端區域;

39、多條所述第一子線間隔設置在所述第一區域,至少一條所述第一子線位于所述近端區域,至少一條所述第一子線位于所述遠端區域;

40、位于所述近端區域的所述第一子線包括多個第一彎折部;

41、在所述電路板組件的平面視圖中,所述第一彎折部的圖案為弧形結構、折線形結構或方形結構中的一種。

42、在本技術的一實施例中,所述電路板組件還包括燒錄接口,所述燒錄接口設于所述電路板上,所述燒錄接口與所述第一存儲器電性連接;

43、所述電路板包括第三串行外設接口總線,所述第三串行外設接口總線包括多條第四子線,所述第四子線電性連接所述燒錄接口和所述時序控制器,所述第四子線的長度小于9000密爾。

44、第二方面,本技術提出了一種顯示裝置,包括電路板組件,所述電路板組件包括電路板、時序控制器以及第一存儲器,電路板包括第一串行外設接口總線,所述第一串行外設接口總線包括多條第一子線;時序控制器設于所述電路板上;第一存儲器設于所述電路板上;其中,多條所述第一子線電性連接所述時序控制器和所述第一存儲器,所述第一子線的長度小于或等于9000密爾。

45、在本技術中,電性連接時序控制器和第一存儲器的第一串行外設接口總線包括多條第一子線,通過將每條第一子線的長度控制在9000密爾以內,就可以縮減電性連接時序控制芯片與存儲芯片的串行外設接口總線的長度,從而縮短時序控制芯片與存儲芯片之間的通訊信號傳輸路徑,以提高時序控制芯片與存儲芯片的信號傳輸的穩定性。

- 還沒有人留言評論。精彩留言會獲得點贊!