納米FET中的硅鍺表面處的基于氮化物的鈍化層的制作方法

本公開涉及納米fet中的硅鍺表面處的基于氮化物的鈍化層。

背景技術:

1、半導體器件被用于各種電子應用中,例如,個人計算機、蜂窩電話、數碼相機、以及其他電子設備。半導體器件通常是通過如下方式來制作的:在半導體襯底之上依次沉積絕緣或電介質層、導電層和半導體材料層,并且使用光刻術對各種材料層進行圖案化,以在其上形成電路組件和元件。半導體行業通過不斷縮小最小特征尺寸來持續改善各種電子組件(例如,晶體管、二極管、電阻器、電容器,等等)的集成密度,這允許更多的組件被集成到給定的區域中。然而,隨著最小特征尺寸的減小,出現了應當解決的額外問題。

技術實現思路

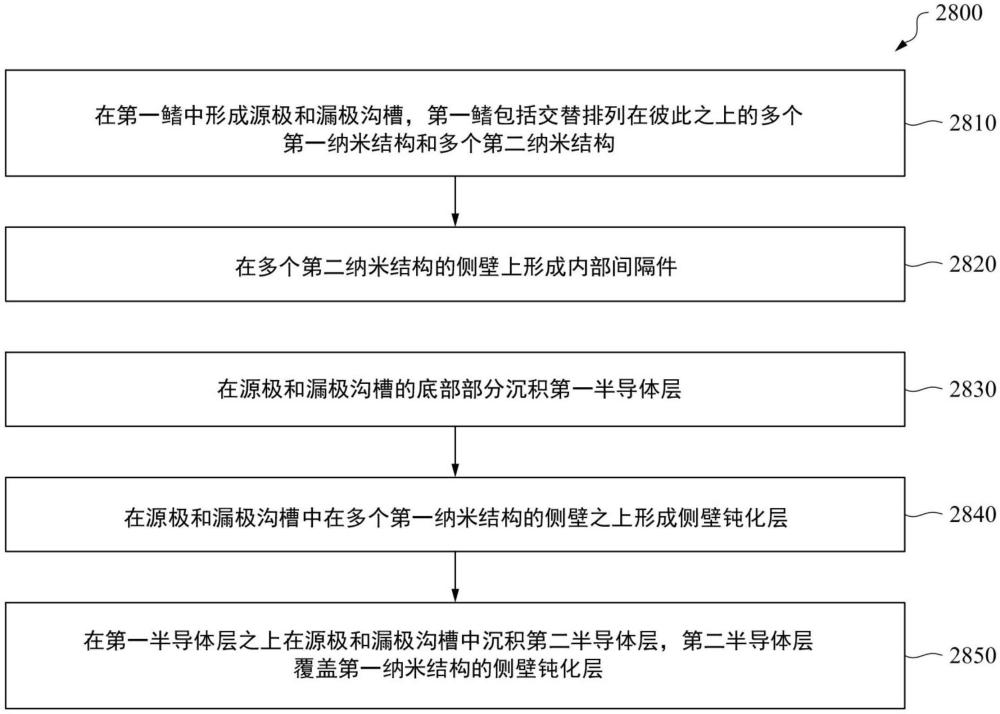

1、根據本公開的一個實施例,提供了一種形成半導體器件的方法,包括:在第一鰭中形成源極和漏極第一溝槽,其中,所述第一鰭包括交替形成在彼此之上的多個第一納米結構和多個第二納米結構;在所述多個第二納米結構的側壁上形成內部間隔件;在源極和漏極第一溝槽的底部部分沉積第一半導體層,其中,所述第一半導體層延伸到最底部納米結構;在所述源極和漏極第一溝槽中在所述多個第一納米結構的側壁之上形成側壁鈍化層;并且在所述第一半導體層之上在所述源極和漏極第一溝槽中沉積第二半導體層,其中,所述第二半導體層在所述源極和漏極第一溝槽的側壁處覆蓋第一納米結構的側壁鈍化層。

2、根據本公開的一個實施例,提供了一種形成半導體器件的方法,包括:在半導體鰭中形成源極/漏極溝槽,其中,所述半導體鰭包括交替形成在彼此之上的多個第一納米結構和多個第二納米結構;在源極/漏極溝槽的底部部分沉積第一sige層,其中,所述第一sige層延伸到最底部納米結構;在所述源極/漏極溝槽中在所述多個第一納米結構的側壁之上形成側壁鈍化層;并且在所述第一sige層之上在所述源極/漏極溝槽中沉積第二sige層,其中,所述第二sige層在所述源極/漏極溝槽的側壁處覆蓋一個或多個第一納米結構的側壁鈍化層。

3、根據本公開的一個實施例,提供了一種半導體器件,包括:第一半導體鰭,在半導體襯底之上,其中,所述第一半導體鰭包括多個第一納米結構;柵極電極,圍繞所述多個第一納米結構中的每一者;源極和漏極區域,在所述第一半導體鰭中,其中,所述源極和漏極區域中的每一者包括:第一半導體層,其中,所述第一半導體層覆蓋所述多個第一納米結構中的至少一者;以及側壁鈍化層,在所述多個第一納米結構中的所述至少一者的側壁上,其中,所述側壁鈍化層在所述第一半導體層和所述多個第一納米結構中的所述至少一者之間。

技術特征:

1.一種形成半導體器件的方法,包括:

2.如權利要求1所述的方法,其中,頂部鈍化層被形成在所述第一半導體層之上,所述方法還包括:

3.如權利要求1所述的方法,其中,所述第一鰭被形成在半導體襯底之上,所述方法還包括:

4.如權利要求3所述的方法,還包括:

5.如權利要求1所述的方法,還包括:

6.如權利要求5所述的方法,其中,所述第二半導體層覆蓋一個或多個額外第一納米結構的側壁鈍化層,并且其中,外延生長的源極和漏極區域與未被所述第二半導體層覆蓋的第一納米結構電接觸。

7.如權利要求6所述的方法,其中,所述第二半導體層在所述源極和漏極第一溝槽的側壁處覆蓋兩個或更多個第一納米結構的側壁鈍化層,并且其中,所述源極和漏極區域不與被所述第二半導體層覆蓋的兩個或更多個第一納米結構電連接。

8.一種形成半導體器件的方法,包括:

9.如權利要求8所述的方法,其中,所述半導體鰭被形成在半導體襯底之上,并且其中,所述源極/漏極溝槽延伸到所述半導體襯底中。

10.一種半導體器件,包括:

技術總結

本公開涉及納米FET中的硅鍺表面處的基于氮化物的鈍化層。在產生納米FET的方法中,在鰭中形成源極和漏極第一溝槽,該鰭包括交替形成在彼此之上的多個第一納米結構和多個第二納米結構。第一半導體層被沉積在源極和漏極第一溝槽的底部部分并且延伸到最底部納米結構。在源極和漏極第一溝槽中在多個第一納米結構的側壁之上形成側壁鈍化層,并且在多個第二納米結構的側壁上形成內部間隔件。在第一半導體層之上在源極和漏極第一溝槽中沉積第二半導體層以覆蓋第一納米結構的側壁鈍化層。

技術研發人員:劉鎮瑋,蔡濟印,游明華

受保護的技術使用者:臺灣積體電路制造股份有限公司

技術研發日:

技術公布日:2025/4/28

- 還沒有人留言評論。精彩留言會獲得點贊!